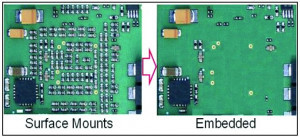

Abb. 2: Eine Baugruppe umgearbeitet von SM auf eingebettete TechnikDie vielen Matratzen und die Erbse erinnern stark an eine Mehrlagenkarte mit eingebetteten Bauteilen. Spricht man also in der Elektronik von einem Matratzenlager, so denkt man nicht an den dünnblütigen Adel sondern an Leiterplatten, in denen sich hoffentlich keine trockene, ungekochte Erbse verbirgt.

Abb. 2: Eine Baugruppe umgearbeitet von SM auf eingebettete TechnikDie vielen Matratzen und die Erbse erinnern stark an eine Mehrlagenkarte mit eingebetteten Bauteilen. Spricht man also in der Elektronik von einem Matratzenlager, so denkt man nicht an den dünnblütigen Adel sondern an Leiterplatten, in denen sich hoffentlich keine trockene, ungekochte Erbse verbirgt.

Eingebettete Bauteile liegen derzeit im Trend, denn sie haben eine Reihe von Vorteilen, wobei man einige Schwierigkeiten jedoch nicht verheimlichen sollte. Der Versuch, Bauteile in die Leiterplatte zu verlegen ist nicht ganz neu [5]. Jedoch ist man in der Zwischenzeit von den eher ‚primitiven' Anfängen, Widerstände in Durchkontaktierungen zu stecken bereits weit entfernt und was man heutzutage schon alles im Innern gewisser Leiterplatten antrifft, geht über die passiven Bauteile beträchtlich hinaus.

Wann immer eine neue Technologie sich bemerkbar macht, wird sie von einigen Vorzügen getrieben, die entweder realistisch sind oder aber nur eine geschickte Vermarktung darstellen. Als offenkundige Vorteile werden angeführt:

- Eine potentielle Verkleinerung der Baugruppe, da auf der Oberfläche weniger Bauteile angeordnet werden

- Oder es wird etwa bei Mobiltelefonen die Anzahl der Bauteile erhöht und die Funktionalität erweitert, ohne dass die Größe verändert werden muss.

- Die Verkürzung der Leiterbahnen reduziert die Selbstinduktion und erlaubt so eine höhere Geschwindigkeit des Kreislaufs.

- Störungen werden reduziert indem die Bauteile in einen Faradaykäfig gesperrt werden.

- Obgleich die Kosten für die Leiterplatte zunehmen, können eventuell die Gesamtkosten der Baugruppe niedriger liegen.

- Durch ein gekonntes Ausnutzen der Leiterplatteneigenschaften (etwa Aluminium) kann man thermische Probleme besser in den Griff bekommen.

- Einige Zuverlässigkeitsprobleme werden reduziert, denn innenliegende Bauteile sind gegen ein Verbiegen der Leiterplatte unempfindlicher als auf der Oberfläche montierte.

Als größter Nachteil wird derzeit die Bildungslücke bei den Ingenieuren gesehen, die weder Erfahrungen beim Layout noch bei der Herstellung haben. Dazu kommt, dass die meisten Rechnerprogramme, die verwendet werden, diese Technologie noch nicht integriert haben und so der Ingenieur bei den Toleranzen und anderen kritischen Vorgaben alleine gelassen wird. Das Problem ist in gewisser Weise durchaus verständlich, da beinahe jede Firma eine andere Vorgehensweise eingeführt hat, die speziell auf deren Produkt zugeschnitten ist.

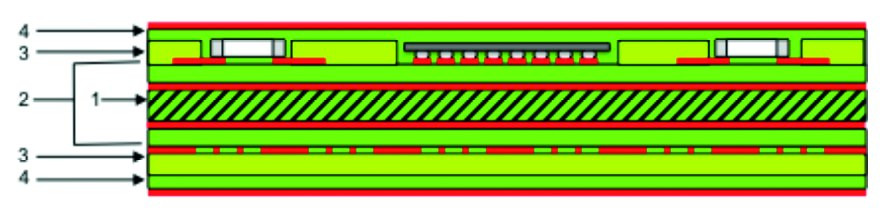

Abb. 3: Beispiel einer LP mit aktiven und passiven eingebetteten Bauteilen (1 = Kern mit zweiseitiger Kupferbeschichtung; 2 = Basis für Bauteilbestückung; 3 = Prepreg mit Aussparungen für Bauteile; 4 = kupferbeschichtetes Dielektrikum)

Abb. 3: Beispiel einer LP mit aktiven und passiven eingebetteten Bauteilen (1 = Kern mit zweiseitiger Kupferbeschichtung; 2 = Basis für Bauteilbestückung; 3 = Prepreg mit Aussparungen für Bauteile; 4 = kupferbeschichtetes Dielektrikum)

Für den Prozessingenieur muss klar sein, dass eine Reparatur weitgehend ausgeschlossen ist, was speziell bei aktiven Bauteilen im Innern ein echtes und eventuell teures Hindernis sein kann.

Zwei Fälle sollen hier als Beispiele für die Vorgehensweise bei der Herstellung von solchen Leiterplatten dienen.

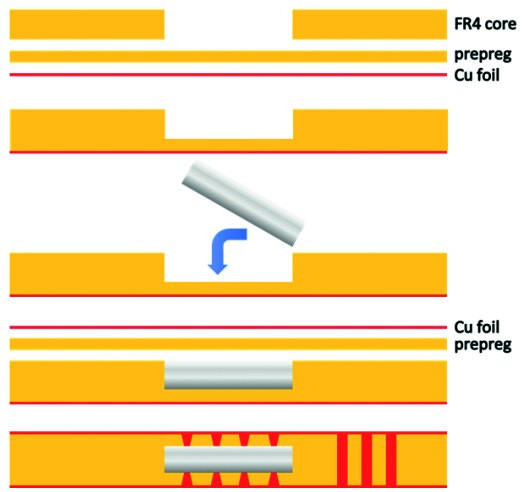

Auf einem vorlaminierten Substrat (Abb. 4), das aus einem strukturierten FR4-Kern besteht und bereits eine Aussparung für die Schottky-Diode enthält, wird ein dünnes Prepreg sowie eine Kupferfolie aufgesetzt. Dieser Stapel wird auf ein Substrat vorlaminiert. Während der anschließenden Laminierung wirkt die Prepreg-Schicht nur als ‚Klebeschicht' da sie nicht vollständig ausgehärtet wurde. In dieses Substrat wird nun der Siliziumchip eingesenkt. Die vorgegebenen Aussparungen im FR4-Kern bestimmen die Position des Chips und müssen so genau wie möglich angeordnet sein.

Abb. 4: Prozessablauf für doppelseitige Cu-Mikro-Durchgänge

Abb. 4: Prozessablauf für doppelseitige Cu-Mikro-Durchgänge

Anschließend werden zusätzliche Lagen aufgebaut (Prepegs plus Kupferfolien). Die Laminierung findet in einer Standard-Mehrlagenpresse statt. Bei diesem Vorgehen wird ein vollständig symmetrischer Aufbau realisiert, der die Chips in der Mitte des Kerns zentriert.

Die elektrischen Kontakte an Anode und Kathode des eingebetteten Chips werden mittels Mikrovias erstellt. Dazu bohrt man Löcher mit einem UV-Laser. Die Verbindung der Anoden von der Vorderseite zur Rückseite der Leiterplatte erfordert das mechanische Bohren von Löchern für eine Durchkontaktierung. Danach wird die Kupfermetallisierung der Durchkontaktierungen erstellt. Lithographie und strukturierendes Ätzen bildet den Abschluss.

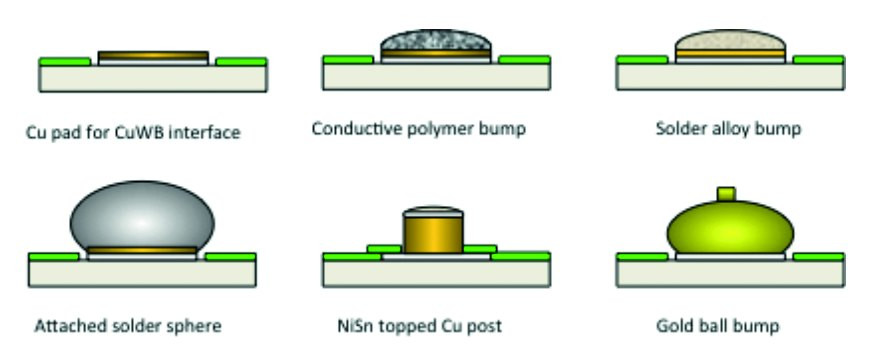

Bei weitem nicht alle Bauteile, die man gerne ins Innere der Leiterplatte versenkt sind sofort dafür geeignet. Da die meisten mit einer Aluminiumbeschichtung für herkömmliche Golddraht-Bondverbindungen versehen sind, die Verbindungen aber in der Leiterplatte andere Chemie und Techniken verwenden, müssen Zwischenschritte durchgeführt werden, die das Bauteil für die Verwendung vorbereiten (Beispiele möglicher Anschlusskonfigurationen siehe Abb. 5).

Abb. 5: Je nach späterer Verbindungstechnik geänderte Anschlussflächen (STC)

Abb. 5: Je nach späterer Verbindungstechnik geänderte Anschlussflächen (STC)

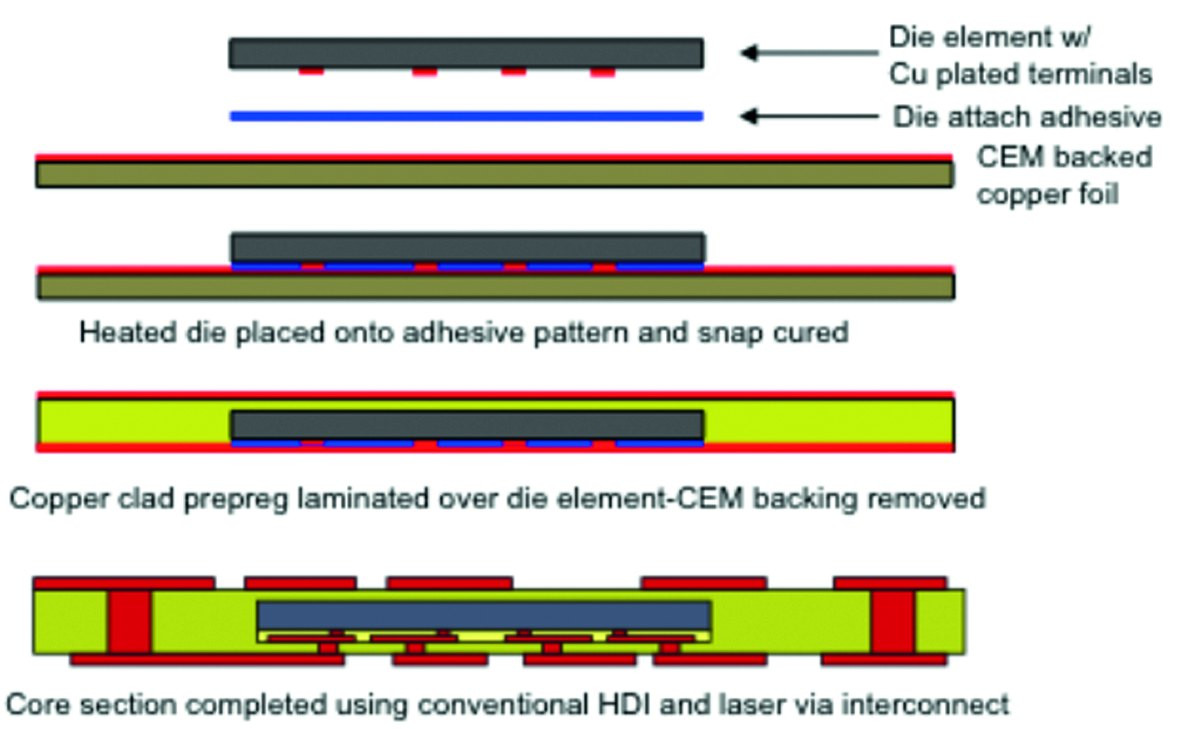

Eine weitere der vielen Varianten des Prozessablaufs wurde von HERMES entwickelt, einem Konsortium der Industrie und akademischer Institute. Hierbei wird eine Kombination aus HDI-Herstellung und Mikroabtragung und -plattierung sowie eine semi-additive Beschichtungstechnologie für ultrafeine Linien verwendet. Die Vorgehensweise eignet sich sowohl für diskrete passive wie auch aktive Bauteile.

Zuerst werden mittels eines Lasers Referenzmarken auf der Oberfläche einer ultradünnen Kupferfolien-Basisschicht markiert. Klebstoff wird auf der Kupferoberfläche aufgetragen und teilweise ausgehärtet. Die Bauteile setzt man dann in das Klebstoffmuster so dass die Anschlussflächen nach unten weisen. Ein thermischer Aushärtungsprozess folgt.

Abb. 6: Variation eines Themas (AT&S)

Abb. 6: Variation eines Themas (AT&S)

Abb. 7: Lötfreie Aluminium-Substrate mit internen Bauteilen können sogar gestapelt und miteinander ,vernietet‘ werdenAnschließend werden zusätzliche vorgestanzte oder laserablatierte FR-4-Prepregs aufgelegt. Alles wird abschließend mit einer herkömmlichen Mehrschichtvakuumpresse laminiert. Die Leiterplatte wird dann mehr oder weniger mit Standardmethoden fertig gestellt (siehe Abb. 6).

Abb. 7: Lötfreie Aluminium-Substrate mit internen Bauteilen können sogar gestapelt und miteinander ,vernietet‘ werdenAnschließend werden zusätzliche vorgestanzte oder laserablatierte FR-4-Prepregs aufgelegt. Alles wird abschließend mit einer herkömmlichen Mehrschichtvakuumpresse laminiert. Die Leiterplatte wird dann mehr oder weniger mit Standardmethoden fertig gestellt (siehe Abb. 6).

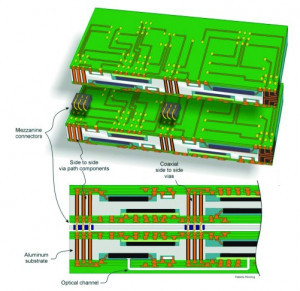

Eine für gewisse Technologien besonders vielversprechende Methode – ebenfalls eine Variation zum Thema Einbettung – verwendet Aluminium-Substrate und kommt ohne Löten aus (Abb. 8).

Unter dem Oberbegriff SAFE (Das Akronym steht entweder für ‚solderless assembly for electronics' (lötfreie Montage für Elektronik) oder ‚solder alloy free electronics' (Lotlegierungsfreie Elektronik)) werden die elektrisch getesteten Bauteile auf einem Aluminiumträger angebracht und die Verbindungen mittels Kupfer hergestellt.

Wieder wird eine lange Liste an Vorteilen genannt, die von Kosteneinsparungen bis zur Umweltfreundlichkeit reichen, wobei einige der elektrischen und elektronischen sowie thermischen sicherlich am interessantesten sein könnten.

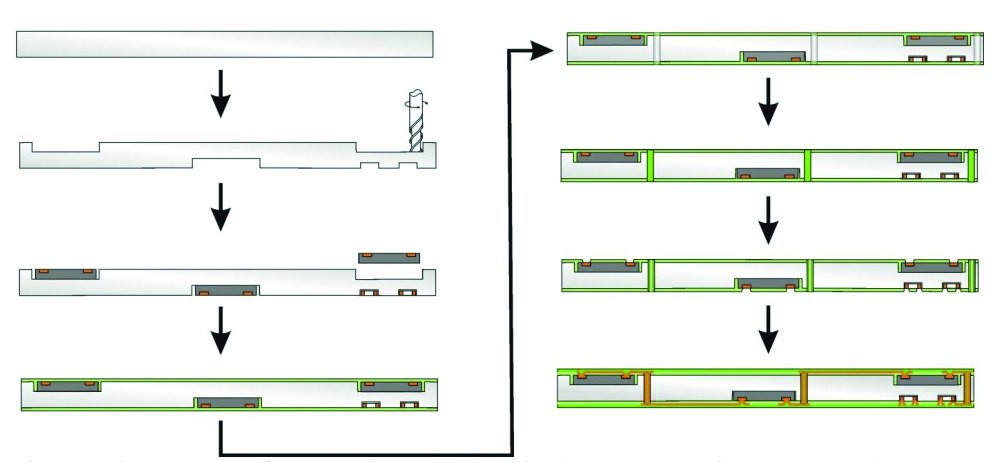

Abb. 8: Prozessschritte für eine doppelseitige Aluminiumschaltung ohne Lötmittel montiert

Abb. 8: Prozessschritte für eine doppelseitige Aluminiumschaltung ohne Lötmittel montiert

Literatur und Anmerkungen:

G. Mayr: Embedded Components: A Comparative Analysis of Reliability Part II, IPC APEX EXPO Conference Proceedings

J.S. Peiffer: Embedded Passives Become Mainstream Technology, Finally!, IPC APEX EXPO Proceedings

H. Chammas: Embedded Passive Technology, IPC APEX EXPO Proceedings

V. Solberg: Embedding Passive and Active Components: PCB Design and Fabrication Process Variations, IPC APEX EXPO Conference Proceedings

IPC-7092: Design and Assembly Process Implementation for Embedded Passive and Active Components, Standard publication, IPC.org

S. Johansson et al.: Miniaturization of Hearing Aid Electronics using Embedded Die Packaging, SMTA Proceedings

J. Fjelstad; Method for the Manufacture of an Aluminum Substrate PCB and its Advantages; IPC proceedings

Referenzen:

[1] Spanisch ‚Sangre azul' – Unter der maurischen Herrschaft in Spanien (711–1492) kam die Bezeichnung ,azurblaues Blut' auf die von den germanischen Westgoten abstammende Oberschicht zur Anwendung

[2] https://www1.wdr.de/stichtag/stichtag1170.html

[3] https://de.wikipedia.org/wiki/Deutscher_Adel#Nachfolgeorganisationen_des_deutschen_Adels

[4] Eigentlich schon bei Hans Christian Andersen

[5] US3519959A: Integral electrical power distribution network and component mounting plane; 1966

[6] HERMES – High density integration by Embedding chips for Reduced size Modules and Electronic Systems. Die Hermes-Partner sind ASM Assembly Systems, Atotechm, Bosch, Circuit Foil Luxembourg, Fraunhofer IZM, Fundico, IMEC, Infineon, Roodmicrotec sowie Thales Communications & Thales Corporate Services