Mitte März wurde in Mountains Hills, Arizona die 19. Internationale Device and Packaging Konferenz und Ausstellung durchgeführt. Die 66 angebotenen Aussteller-Stände wurden weit im Voraus ausverkauft, das Konferenzhotel schon Anfang Februar ausgebucht. Mit den 12 Professional Development Courses, hochkarätigen Keynote-Präsentationen und über 80 Fachvorträgen war die Konferenz ein gelungenes Event für alle Spezialisten im Bereich des Elektronik Packaging.

Auch wir freuen uns, zu bewährten Formaten zurück zu kommen. Am 23. März findet an der TU Ilmenau das Frühjahrsseminar von IMAPS Deutschland statt. Zwölf Vorträge beleuchten die unterschiedlichen Aspekte des breiten Themas ‚Nachhaltigkeit' im Elektronikumfeld.

Im September kommt das wichtigste Event des Jahres für die europäische IMAPS-Community – die ‚24th European Microelectronics & Packaging Conference EMPC'. Die Konferenz wird vom UK IMAPS Chapter ausgetragen und findet in Genome Centre in Hinxton in der Nähe von Cambridge statt. Das Call-for-Papers ist abgeschlossen, die Organisatoren arbeiten an der Zusammenstellung des Konferenzprogramms zu den gewohnten Themen Semiconductor Industry Trends, Packaging Technologies, Performance and Reliability, Design & Process Optimisation, Markets and Developments, Integration, Materials, Design and Test. Wir laden Sie herzlich ein, an der EMPC teilzunehmen, die Frühbucher-Anmeldegebühr ist noch bis Ende Mai gültig.

Galvanische Abscheidung von Aluminium auf Waferlevel für die Aufbau- und Verbindungstechnik

Das Fraunhofer Institut für elektronische Nanosysteme (ENAS) in Chemnitz hat seit 2014 kontinuierlich an der Umsetzung der galvanischen Abscheidung von Aluminium für die Aufbau- und Verbindungstechnik von Mikrosystemen geforscht. Dafür wurden verschiedene Substrate und Anwendungsfälle betrachtet. Im BMBF-Verbundprojekt ‚AioLi' (FKZ: 16ES0329K) wurde dabei der Grundstein für die Skalierung auf Waferlevel gelegt. In diesem Projekt wurde die Beschichtung von Leiterplatten (FR4), Keramik-Leiterplatten in Dünnschichttechnik und Al-Schichten für die Herstellung von Aluminiumoxidmembranen untersucht. Weiterhin konnte der Prozess auf 100 mm- und später 150 mm-Wafer skaliert werden. Im Rahmen einer Fraunhofer ENAS-internen Eigenforschung und eines CORNET-Projektes (AdEPT; IGF-Vorhabennr.: 200EBG) wurde der galvanische Abscheideprozess auf 150 mm-Waferlevel weiterentwickelt. Der Vorteil liegt darin, dass viel dickere Al-Schichten abgeschieden werden können als bei PVD-Prozessen und somit die Verformbarkeit des Al ausgenutzt werden kann. Mit diesen Al-Schichten wird daher das Waferlevel Al-Al-Thermokompressionsbonden (TKB) zur hermetischen Verkapselung und elektrischen Kontaktierung von MEMS und die Ultraschall Flip Chip Montage als neuartige Chip Verbindungstechnik erforscht (Fraunhofer intern, AlPiMon, Fördernr. SME 601 470). Aluminium bietet dabei den Vorteil, dass es eine sehr gute Haftung und Kontaktierung zum Siliciumoxid bzw. Silicium aufweist. Eine Diffusionsbarriere wie bei Kupferschichten ist nicht notwendig. Somit kann perspektivisch ein monometallisches System aufgebaut werden, welches entsprechend frei von intermetallischen Phasen ist. Die Zuverlässigkeit der Verbindungstechnik soll somit ebenfalls erhöht werden.

Die Al-Abscheidung muss aus nicht-wässrigen Medien erfolgen. Am ENAS wird dafür die ionische Flüssigkeit (ionic liquid, IL) 1-Ethyl-3-Methylimidazoliumchlorid mit Aluminiumtrichlorid (EMImCl/AlCl3) im Verhältnis 1:1,5 von IoLiTec GmbH (Heilbronn) eingesetzt. Das IL ist wassersensitiv und muss daher feuchtigkeitsfrei in einer Glovebox gehandhabt werden. Die Abscheidung auf Waferlevel findet in einer IL kompatiblen Abscheidezelle (Silicet AG) statt, d. h. die verwendeten Materialien werden nicht oder nur sehr geringfügig von dem IL angegriffen. Hierbei handelt es sich derzeit noch um einen Laboraufbau, siehe Abbildung 1.

Abb. 1: A) Abscheidezelle außerhalb der Glovebox in geöffneter Position; B) Abscheidezelle während der Befüllung mit IL innerhalb der Glovebox; C) Netto-Reaktionsgleichungen im IL

Abb. 1: A) Abscheidezelle außerhalb der Glovebox in geöffneter Position; B) Abscheidezelle während der Befüllung mit IL innerhalb der Glovebox; C) Netto-Reaktionsgleichungen im IL

Für die Abscheidung werden thermisch oxidierte Siliciumwafer mit einer gesputterten Al-Startschicht genutzt. Die Al Strukturen werden durch die Abscheidung in einer Lackmaske erzielt. Zunächst mussten die Abscheideparameter für eine Al-Startschicht identifiziert werden, da eine Übertragung der bekannten Parameter von Gold- oder Kupferstartschicht nicht möglich war. Es ist ein anodischer Rückpuls notwendig, um Haftung und Schichtwachstum auf der Al Startschicht zu erzielen. Weiterhin können nur geringe Stromdichten von 5 bis max. 7,5 mA/cm² genutzt werden, so dass die Abscheiderate zwischen 100 und 160 nm/min liegt. Durch eine entsprechende Optimierung der Prozessbedingungen können reproduzierbar Schicht-Inhomogenitäten kleiner 15 % erzielt werden. Das ENAS hat damit weltweit einen einzigartigen Prozess aufgebaut.

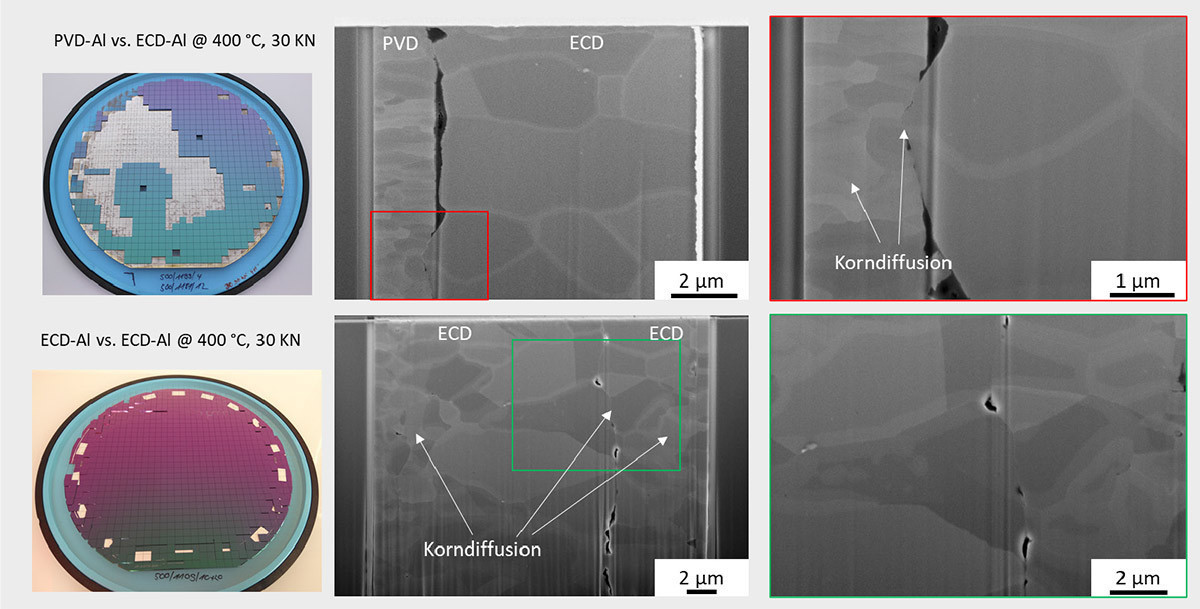

Die hergestellten Al-Schichten sollen z. B. für das Thermokompressionsbonden (TKB) eingesetzt werden. Das TKB beruht auf der Festkörperdiffusion über eine Phasengrenze hinweg. Die natürliche Oxidschicht des Al wirkt allerdings als Diffusionsbarriere. Daher müssen relativ hohe Kräfte und Temperaturen eingesetzt werden, um die Diffusion zwischen dem darunter liegenden Al zu erreichen. Die galvanischen Al-Schichten (nachfolgend ECD-Al) sind nicht nur dicker als PVD-Schichten, sondern auch rauer. Diese Rauheiten könnten die Oxidschicht und somit die Diffusionsbarriere durchstechen, so dass geringere Fügetemperaturen und -kräfte appliziert werden könnten. In einigen Bonduntersuchungen zwischen PVD-Al (2 µm) und ECD-Al (8 µm) konnte festgestellt werden, dass die Rauheiten das Oxid durchstechen können. Allerdings fungieren diese auch als Abstandshalter, so dass keine geschlossene Fügegrenze entstehen kann. Bei gleichen Fügeparametern, aber zwei ECD-Al Schichten (19 und 8 µm Dicke), sind hingegen deutlich weniger Fehlstellen in der Fügezone vorhanden. Außerdem ist die Korndiffusion sowohl an der Fügezone als auch im Schichtinneren deutlich sichtbar. Der Schichtverbund wurde dabei ca. 5 µm komprimiert, wohingegen beim PVD-Al vs. ECD-Al keine Komprimierung messbar war. Die Sägeausbeute ist bei zwei ECD-Al Schichten ebenfalls wesentlich höher als bei PVD-Al vs. ECD-Al. Beispielhaft sind beide Ergebnisse für 400 °C und 30 kN in Abbildung 2 dargestellt.

Abb. 2: Gegenüberstellung der Bonduntersuchungen für 400 °C und 30 kN für PVD-Al vs. ECD-Al (oben) und ECD-Al vs. ECDl-Al (unten)

Abb. 2: Gegenüberstellung der Bonduntersuchungen für 400 °C und 30 kN für PVD-Al vs. ECD-Al (oben) und ECD-Al vs. ECDl-Al (unten)

Für ein weiteres Prozessverständnis müssen noch Untersuchungen hinsichtlich der Prozessintegration der Al Abscheidung, des Einflusses der Rauheit sowie der Schichtdicke folgen.

Weiterhin können mit der Abscheidemethode Aluminium-Pillars für die Chip Montage hergestellt werden. Der Fügeprozess ist vergleichbar mit einem Ultraschall-Drahtbondprozess, nur dass viele Pillars gleichzeitig unter Einwirkung von Ultraschall gefügt werden können. Da hier die Aluminiumpads eines fertigen Halbleiterchips genutzt werden, ist keine Ummetallisierung notwendig, wie man es von Lotbumps oder Kupfer-Zinn-Bumps kennt. Der Vorteil liegt somit in weniger Prozessschritten, weniger intermetallischen Phasengrenzen und somit einer potentiell höheren Zuverlässigkeit. Dies gilt es noch zu beweisen.

Die galvanische Al-Abscheidung soll in den nächsten zwei Jahren auf eine vollautomatische industrienahe Anlage überführt werden, so dass auch die Prozessierung von 200 mm-Wafern möglich ist.

Kontakt: Silvia Braun, Fraunhofer Institut für elektronische Nanosysteme (ENAS), Chemnitz, Diese E-Mail-Adresse ist vor Spambots geschützt! Zur Anzeige muss JavaScript eingeschaltet sein!.

Veranstaltungskalender

|

Ort |

Zeitraum |

Name |

Veranstalter |

|

Albuquerque |

18. - 20. Apr 2023 |

CICMT 2023 |

IMAPS/ACerS |

|

Oslo |

12. - 14. Jun 2023 |

NordPac 2023 |

IMAPS Nordic |

|

Cambridge |

11. - 14. Sep 2023 |

EMPC 2023 |

IMAPS UK |

|

San Diego |

02. - 05. Okt 2023 |

56th International Symposium on Microelectronics |

IMAPS US |

|

München |

19. - 20. Okt 2023 |

Herbstkonferenz |

IMAPS DE |

|

München |

14. - 17. Nov 2023 |

SEMICON EUROPA |

SEMI Europa |

IMAPS Deutschland – Ihre Vereinigung für Aufbau- und Verbindungstechnik

IMAPS Deutschland, Teil der ‚International Microelectronics and Packaging Society' (IMAPS), stellt seit 1973 in Deutschland das Forum für alle dar, die sich mit Mikroelektronik und Aufbau- und Verbindungstechnik beschäftigen. Mit fast 300 Mitgliedern verfolgen wir im Wesentlichen drei wichtige Ziele:

- wir verbinden Wissenschaft und Praxis

- wir sorgen für den Informationsaustausch unter unseren Mitgliedern und

- wir vertreten den Standpunkt unserer Mitglieder in internationalen Gremien.

Impressum

IMAPS Deutschland e. V.

Kleingrötzing 1, D-84494 Neumarkt-St. Veit

1. Vorsitzender: Prof. Dr.-Ing. Martin Schneider-Ramelow, Institutsleiter Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration (IZM),

Diese E-Mail-Adresse ist vor Spambots geschützt! Zur Anzeige muss JavaScript eingeschaltet sein!

Schatzmeister

(bei Fragen zu Mitgliedschaft und Beitrag):

Ernst G. M. Eggelaar, Diese E-Mail-Adresse ist vor Spambots geschützt! Zur Anzeige muss JavaScript eingeschaltet sein!

Ausführliche Kontaktinformationen zu den Vorstandsmitgliedern finden Sie unter www.imaps.de

(Vorstand)