Vom 2. bis zum 3. Februar 2023 haben unsere amerikanischen Kollegen in San Diego zum „Topical Workshop & Tabletop Exhibition on WIRE BONDING“ eingeladen und viele Interessenten sind diesem Aufruf gefolgt. Auch dank unseres Mitglieds HESSE Mechatronics konnten sich die Teilnehmer in diversen Vorträgen, aber auch in dem von Mike McKeown geleiteten Workshop über die neuesten Entwicklungen der Drahtbondtechnologien in den Anwendungsbereichen Batterieproduktion für E-Mobility und Sustainable Energy, Halbleiterfertigung und Microelectronic Packaging informieren und in gemeinsamen Breakout-Sessions austauschen.

Drahtbonden ist mit einem Marktanteil von immer noch über 85 % weiterhin die vorherrschende Methode der Chipverbindung und bietet herausragende Vorteile gegenüber der FlipChip-Technologie. Jährlich werden Aber-Billionen von Drahtbonds hergestellt. In hochvolumigen und gut kontrollierten Anlagen liegen die Fehlerraten im niedrigen ppm-Bereich. Es bleibt somit eine kostengünstige und vor allen Dingen äußerst flexible Methode der Chipverbindung.

Sowohl beim Ball- als auch beim Wedge-Bonden wird der Draht zwischen dem Bondwerkzeug und dem Bondpad oder Substrat massiv verformt, wodurch eine Schweißverbindung entsteht. Die dominanten Variablen, die die Verformung beeinflussen, sind Ultraschallenergie, Temperatur, Bondkraft und Bondzeit.

Ultraschallenergie ist die wesentliche Prozessvariable beim Drahtbonden. Sie reduziert die erforderlichen Kräfte und ermöglicht eine Verformung bei deutlich geringerer Belastung des Drahtes und der zu verbindenden Komponenten wie Chip und Substrat, als es sonst erforderlich wäre. Hochfrequenz-Ultraschall sorgt für höhere Dehnungsraten und ermöglicht eine schnellere, besser kontrollierte Verformung, die für präzises Bonden mit hoher Ausbeute und hohe Produktivität erforderlich ist. Dieses gilt sowohl für das weit verbreitete Dünndrahtbonden als auch für das immer prominenter werdende Dickdrahtbonden, wie es Lee Levine in seinem Tutorial herausgestellt hat.

Weitere interessante Vorträge beleuchteten die Herausforderungen aber auch Prozessvariationen und Lösungsansätze für das Dickdrahtbonden von Kupfer-Drähten, den Einsatz von neuen Bondmaterialien, die Anforderungen an eine hohe Zuverlässigkeit und Fehleranalyse sowie neue Teststrategien bei zunehmenden Systemherausforderungen und Packungsdichten.

Insgesamt ein sehr zeitgemäßes Programm, welches durch rund 10 Aussteller in der parallelen Begleitausstellung abgerundet wurde.

Fast schon auf die Inhalte der Konferenz in San Diego aufbauend haben unsere französischen Kollegen in Poitier vom 8. bis 9. März 2023 einen Workshop über Thermal Management organisiert, der leider auf Grund des zeitgleichen Streiks der öffentlichen Verwaltung und des Transportsystems nicht so gut besucht gewesen ist, wie es das Thema verdient hätte. Forschungsnahe, industrielle und innovative Vorträge zum Thema Kühlung von integrierten Schaltkreisen und Packages, Advanced Materials, Thermal Management über die gesamt Prozesskette, vom Basismaterial über Komponenten, Hilfs- und Betriebsstoffe bis zum fertigen Produkt, hätten hier durchaus mehr Beachtung verdient.

Und was dürfen unsere Mitglieder von uns, dem IMAPS Deutschland e. V. erwarten?

IMAPS Deutschland knüpfte nach dreijähriger Pause am 23. März 2023 wieder an die Tradition an, ein Frühjahrseminar zu einem aktuellen Thema der Mikrosystemtechnik anzubieten. In diesem Jahr haben wir durch verschiedene Vorträge eine Diskussionsbasis zu einem drängenden Thema der Gegenwart mit Bezug zur Nachhaltigkeit in der Elektronikfertigung geschaffen, welches da lautete: Wie können wir es schaffen, die Produktion oder einzelne Fertigungsabschnitte nachhaltig zu gestalten und welche Aspekte müssen dabei zwingend berücksichtigt werden?

Dieses Thema wird dann der Schwerpunkt unserer Berichterstattung in der kommenden PLUS Ausgabe sein. Bleiben Sie gespannt.

Prototypenfertigung von System-in-Foil mit ultradünnen Siliciumchips bei Hahn-Schickard

Abb. 1: System-in-Foil mit ultradünnem Siliziumchip und elektrischer Kontaktierung mit Inkjetdruck (Fotos: Hahn-Schickard)Folienbasierte Mikrosysteme mit integrierten, ultradünnen Siliciumchips, besser bekannt als System-in-Foil (SiF), ermöglichen einen Einsatz überall dort, wo konventionelle Schaltungsträger an ihre Grenzen kommen (Abb. 1). Durch die geringe Bauhöhe können solche Systeme in dünnwandige Strukturen integriert werden. Das erlaubt beispielsweise die Nachrüstung von Produktionsanlagen mit Sensorik („Retrofit“), die Funktionalisierung von Leichtbau-Elementen oder eine platzsparende Batterieüberwachung. In der Luft- und Raumfahrt und bei Elektrofahrzeugen können SiF einen Beitrag zur Gewichtseinsparung leisten. Weiterhin lässt die hohe mechanische Flexibilität dynamische Bewegungen zu, so dass SiF auch in gekrümmte Bauräume eingebaut oder für körpernahe Sensoren und in Form von Smart Wearables für medizintechnische Anwendungen realisiert werden können.

Abb. 1: System-in-Foil mit ultradünnem Siliziumchip und elektrischer Kontaktierung mit Inkjetdruck (Fotos: Hahn-Schickard)Folienbasierte Mikrosysteme mit integrierten, ultradünnen Siliciumchips, besser bekannt als System-in-Foil (SiF), ermöglichen einen Einsatz überall dort, wo konventionelle Schaltungsträger an ihre Grenzen kommen (Abb. 1). Durch die geringe Bauhöhe können solche Systeme in dünnwandige Strukturen integriert werden. Das erlaubt beispielsweise die Nachrüstung von Produktionsanlagen mit Sensorik („Retrofit“), die Funktionalisierung von Leichtbau-Elementen oder eine platzsparende Batterieüberwachung. In der Luft- und Raumfahrt und bei Elektrofahrzeugen können SiF einen Beitrag zur Gewichtseinsparung leisten. Weiterhin lässt die hohe mechanische Flexibilität dynamische Bewegungen zu, so dass SiF auch in gekrümmte Bauräume eingebaut oder für körpernahe Sensoren und in Form von Smart Wearables für medizintechnische Anwendungen realisiert werden können.

Für ultradünne Siliciumchips wird die Chiprückseite durch Schleifen abgetragen. Bei Dicken von 50 µm und niedriger wird das kristalline Silicium mechanisch flexibel und kann gebogen werden. Dies erschwert jedoch auch die Handhabung der Siliciumchips während der Prozesskette vom Pick-&-Place-Prozess bis hin zur klebtechnischen Montage. Eine ungeeignete Aufnahme der ultradünnen Chips mit einem Ansaugwerkzeug kann zum Sprödbruch führen. Weiterhin neigen die rückgedünnten Chips durch die Strukturen auf der Oberfläche zu thermo-mechanischen Spannungen, die eine Wölbung des gesamten Siliciumchips zur Folge hat, wenn dieser während der Montage nicht konstant fixiert wird.

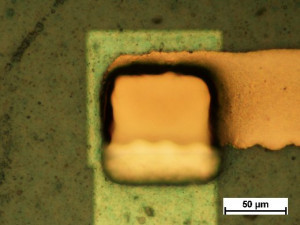

Das Hahn-Schickard-Institut für Mikroaufbautechnik entwickelte manuelle sowie automatisierbare Prozesse zur Montage von ultradünnen Siliciumchips [1] mit Hilfe von Klebeverfahren. Hierbei wird auf den Foliensubstraten eine homogene Klebstoffverteilung mit wenigen Mikrometern Dicke erreicht, so dass der Klebstoff keine Versteifung des biegbaren Chips bewirkt. Nach der Montage wurde zum Schutz der empfindlichen Chips mittels Sprühbeschichtung eine Einbettung in flexiblen Lötstopplack durchgeführt. Die nur 15–20µm dicke Lötstopplackschicht wurde fotolithografisch strukturiert, um die Kontaktflächen auf dem Siliciumchip zu öffnen. Da hierbei ein maskenloses Direktbelichtungs-Verfahren auf Basis von UV-LEDs eingesetzt wurde, konnten die Layouts zur Öffnung der Kontaktflächen sowie die Position der Öffnungen individuell variiert werden, beispielsweise zur Fertigung von Prototypen oder um eine eventuelle Verdrehung der Chips bei der Montage auszugleichen.

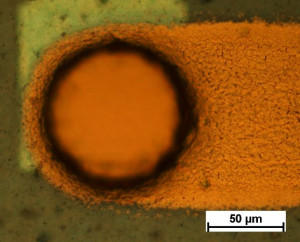

Die elektrische Kontaktierung der ultradünnen Siliciumchips erfolgt durch Inkjetdruck von nanopartikulären Metalltinten. Sowohl Tinten mit Silber- als auch Goldnanopartikeln wurden untersucht (Abb. 2). Die unterschiedlichen Lösungsmittel der Tinten bewirkten unterschiedliche Benetzungseigenschaften, die sich sowohl als Coffee-Stain-Effekt als auch als Marangoni-Effekt äußerten [2].

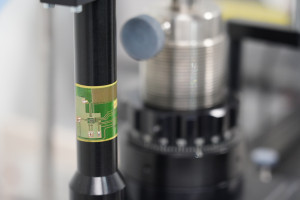

Abb. 3: Folienbasiertes System zur Charakterisierung der BiegewechselfestigkeitNeben ultradünnen Siliciumchips sind auf SiF meist auch SMD, wie beispielsweise Kondensatoren oder Widerstände, notwendig. Zur Bestimmung der Ausfallwahrscheinlichkeit der kontaktierten Komponenten wurde ein Biegeprüfstand aufgebaut, mit dem SiF unter definierten Biegeradien dynamisch belastet und mit dem unterschiedliche Metallisierungsschichten und Kontaktierungsverfahren untersucht werden können.

Abb. 3: Folienbasiertes System zur Charakterisierung der BiegewechselfestigkeitNeben ultradünnen Siliciumchips sind auf SiF meist auch SMD, wie beispielsweise Kondensatoren oder Widerstände, notwendig. Zur Bestimmung der Ausfallwahrscheinlichkeit der kontaktierten Komponenten wurde ein Biegeprüfstand aufgebaut, mit dem SiF unter definierten Biegeradien dynamisch belastet und mit dem unterschiedliche Metallisierungsschichten und Kontaktierungsverfahren untersucht werden können.

So zeigte sich beispielweise eine Tendenz zu höherer Biegezyklenanzahl bis zum Ausfall bei leitfähig geklebten SMD im Vergleich zu gelöteten SMD [3]. Der Formfaktor der SMD hingegen zeigte einen vernachlässigbaren Einfluss.

Literatur:

1. Janek, F.; Saller, E.; Müller, E.; Meißner, T.; Weser, S.; Barth, M.; Eberhardt, W.; Zimmermann, A.: Feasibility Study of an Automated Assembly Process for Ultrathin Chips, Micromachines, 11, 2020, 654, doi:10.3390/mi11070654

2. Janek, F.; Eichhorn, N.; Weser, S.; Gläser, K.; Eberhardt, W.; Zimmermann, A.: Embedding of Ultrathin Chips in Highly Flexible, Photosensitive Solder Mask Resist, Micromachines, 12, 2021, 856, doi:10.3390/mi12080856

3. Saleh, R.; Schütt, S.; Barth, M.; Lang, T.; Eberhardt, W.; Zimmermann, A.: Assembly of Surface-Mounted Devices on Flexible Substrates by Isotropic Conductive Adhesive and Solder and Lifetime Characterization, Micromachines, 13, 2022, doi:10.3390/mi13081240

Veranstaltungskalender

|

Ort |

Zeitraum |

Name |

Veranstalter |

|

Albuquerque |

18. - 20. Apr 2023 |

3-in-1: CICMT+ HITEC+ PowerPack 2023 |

IMAPS/ACerS |

|

Oslo |

12. - 14. Jun 2023 |

NordPac 2023 |

IMAPS Nordic |

|

Cambridge |

11. - 14. Sep 2023 |

EMPC 2023 |

IMAPS UK |

|

San Diego |

02. - 05. Okt 2023 |

56th International Symposium on Microelectronics |

IMAPS US |

|

München |

19. / 20. Okt 2023 |

IMAPS Deutschland Herbstkonferenz |

IMAPS DE |

|

München |

14. - 17. Nov 2023 |

SEMICON EUROPA |

SEMI Europa |

Dieser Kalender gilt unter Vorbehalt. Bitte beachten Sie die Informationen und Hinweise der Veranstalter auf den entsprechenden Webseiten!

IMAPS Deutschland – Ihre Vereinigung für Aufbau- und Verbindungstechnik

IMAPS Deutschland, Teil der ‚International Microelectronics and Packaging Society' (IMAPS), stellt seit 1973 in Deutschland das Forum für alle dar, die sich mit Mikroelektronik und Aufbau- und Verbindungstechnik beschäftigen. Mit fast 300 Mitgliedern verfolgen wir im Wesentlichen drei wichtige Ziele:

- wir verbinden Wissenschaft und Praxis

- wir sorgen für den Informationsaustausch unter unseren Mitgliedern und

- wir vertreten den Standpunkt unserer Mitglieder in internationalen Gremien.

Impressum

IMAPS Deutschland e. V.

Kleingrötzing 1, D-84494 Neumarkt-St. Veit

1. Vorsitzender: Prof. Dr.-Ing. Martin Schneider-Ramelow, Institutsleiter Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration (IZM),

Diese E-Mail-Adresse ist vor Spambots geschützt! Zur Anzeige muss JavaScript eingeschaltet sein!

Schatzmeister

(bei Fragen zu Mitgliedschaft und Beitrag):

Ernst G. M. Eggelaar, Diese E-Mail-Adresse ist vor Spambots geschützt! Zur Anzeige muss JavaScript eingeschaltet sein!

Ausführliche Kontaktinformationen zu den Vorstandsmitgliedern finden Sie unter www.imaps.de

(Vorstand)

Kontakt:

Herr Florian Janek

Hahn-Schickard-Gesellschaft für angewandte Forschung e. V.

E-Mail: Diese E-Mail-Adresse ist vor Spambots geschützt! Zur Anzeige muss JavaScript eingeschaltet sein!