Deutschland kann Digitalisierung und Technologie

Konnektivität+Rechentechnik+Cloud ist der Kernantrieb der intelligenten Gesellschaft. „Das explosive Wachstum des datengenerierten und globalen Netzwerkverkehrs verändert die Struktur der Wirtschaft“, betonte Laith Altimime, Präsident SEMI Europe im Januar. Uwe Peter, Deutschlandchef von Cisco resümierte im Mai: „In den letzten Wochen haben wir gesehen, wie ein digitales Deutschland aussehen kann. Wenn es drauf ankommt, kann Deutschland Digitalisierung auch in Lichtgeschwindigkeit. Wir haben Technologien dazu genutzt, unser Zusammenleben, unsere Wirtschaft sowie unsere Verwaltungs-, Regierungs-, Bildungs- und Gesundheitssysteme aufrecht zu erhalten. Und wir haben gemerkt: Es funktioniert. Das sollte uns Mut machen, den Weg der Digitalisierung noch entschlossener weiter zu gehen.“ Der Präsident des SEMI Europa, Laith Altimime im Gespräch mit Michael Kaiser/Smart Systems Hub Dresden GmbH (links)

Der Präsident des SEMI Europa, Laith Altimime im Gespräch mit Michael Kaiser/Smart Systems Hub Dresden GmbH (links)

Einerseits steigt die Marktnachfrage für schnellere und spezialisierte Logikchips, die sprachgesteuerte digitale Assistenten oder künstlich intelligente Systeme erst möglich machen. Andererseits sind für viele neue mobile Geräte universelle Wollmilchsäue gefragt, die Chip, Datensender, Prozessor und Sensor-Phalanx in einem sind, ganz wenig Strom verbrauchen und wenig kosten. Früher wurde dabei einfach auf Chips mit kleineren Strukturen (More Moore) gesetzt. Jetzt muss sich die Branche auf eine grundsätzlich höhere funktionelle Dichte der Produkte einstellen (More than Moore) und deutlich mehr in F und E investieren. Dabei sind immer mehr physikalische Grenzen zu überwinden und geeignete Fabriken kosten zweistellige Milliarden-Beträge. Die Corona-Krise hat die Branche nur wenig ausgebremst: Die Umsätze des MEMS-Auftragsfertiger X-Fab Silicon Foundries aus Erfurt/Dresden fielen zwar im ersten Quartal um 3 %, aber das Auftragsvolumen legte um ein Viertel zu, teilte CEO Rudi De Winter mit. Im Mai fuhr das Unternehmen eine neue Linie für SiC-Leistungshalbleiter hoch. Laura Mirkarimi, hier auf dem Informationsstand der Xperi Co., informierte im Vortrag über die Xperi-DBI Ultra Die-to-Wafer Hybrid Bond-Technologie (16-fach 3D-gestapelte Speicher), rechts M. Jürgen Wolf (Fraunhofer-IZM/Mitglied des SEMI-Organisations-komitees)

Laura Mirkarimi, hier auf dem Informationsstand der Xperi Co., informierte im Vortrag über die Xperi-DBI Ultra Die-to-Wafer Hybrid Bond-Technologie (16-fach 3D-gestapelte Speicher), rechts M. Jürgen Wolf (Fraunhofer-IZM/Mitglied des SEMI-Organisations-komitees)

Mikroelektronikexperten trafen sich in Dresden

Die sächsische Landeshauptstadt Dresden war im Januar wieder Gastgeber des ‚SEMI 3D & Systems Summit‘. Spitzenvertreter der weltweit führenden Branchengrößen Intel, TSMC, Infineon, ASML, Globalfoundries, Huawei, IMEC oder CEA-Leti befanden sich unter den weit mehr als 300 Teilnehmern des seit 2009 jährlichen Treffens des globalen Mikroelektronikverbandes SEMI. Hintergrund des 3D-Gipfels in diesem Jahr war dieser Umdenkprozess in der Branche: Wegen immens steigender Kosten und technologischer Herausforderungen ist ein „weiter so wie früher“ für die Halbleiterindustrie nicht mehr möglich. Dem starken Mikroelektronik/IKT-Cluster, jeder zweite in Europa gefertigte Chip kommt aus Dresden, und der ausgeprägten Expertise zur 3D- und heterogenen Systemintegration ist zu verdanken, dass dieses hochkarätig besetzte Treffen seit drei Jahren wieder mit stetig wachsendem Interesse in Dresden stattfindet.

Im ‚Großen Ballsaal‘ des Hilton-Hotels in Dresden sprach Séverine Cheramy vom französischen Forschungszentrum CEA-Leti über die Innovationswelle der 3D-VLSI-Technologien

Im ‚Großen Ballsaal‘ des Hilton-Hotels in Dresden sprach Séverine Cheramy vom französischen Forschungszentrum CEA-Leti über die Innovationswelle der 3D-VLSI-Technologien

Die Branchenvertreter diskutierten, wie sich Chips noch effektiver in 3D verbinden lassen, welche Chancen so entwickelte smarte Systeme im IoT oder für den 5G-Mobilfunk haben, welche Technologien nötig sind, welche Chip-Bauformen sich durchsetzen und wie sich ganze Systeme in einem Chipgehäuse unterbringen lassen.

Multichip- und Chipletmodule – hochintegrierte Systeme

Die Präsidentin der TechSearch International Inc., einem weltweit führenden Beratungs- und Lizensierungsunternehmen für Elektronik-Fertigung und Halbleiterpackaging, E. Jan Vardaman, betonte in ihrem Eröffnungsvortrag, dass „eine neue Ära für 3D angebrochen ist“. Sie analysierte die Packaging Trends für Anwendungen im Bereich Künstlicher Intelligenz KI, Machine Deep Learning und Prädiktion sowie Mobilfunk 5G. Auch Séverine Cheramy vom französischen Forschungszentrum CEA-Leti betonte, dass Smartes Computing nicht mehr nur eine Frage des Cloud Hochleistungsrechnens HPC ist, sondern für verteiltes Rechnen und KI in Smart Sensor- oder Smart Vision-Systemen mit extremer Energieeffizienz essenziell. Die Entwicklung wird neue Hierarchien für Informatik und KI hervorrufen: smarte Hierarchien für kombinierte Speicher-/Rechentechnik immenser Datenvolumina und effiziente Edge-to-Cloud-Kommunikation.

Einheitliche Lösungen für den Aufbau von 3D-Stapelungen und Multichip-Modulen gibt es nicht. Neben der Direktmontage und 3D-Stapelung auf dem Grundsubstrat (PCB-Kern) mit Flip-Chip-BGA, Flip-Chip-CSP oder Fan-Out auch auf zusätzlichen Zwischenträgern (Interposer) werden Stapelung im Chipniveau (Die-to-Die Interconnects) oder Einbettungen EMIB (Embedded Multi-Die-Interconnect Bridge) ausgeführt. Möglich sind Module mit kleinstem Formfaktor (System-on-Chip SoC), größere (System-in-Package SiP) und große SiP-Systeme mit 100 und mehr Komponenten durch Hinzufügen von Interposern. Dieses Design ermöglicht 2.xD- und 3D-Paketarchitekturen mit mechanischer Stabilität und Fan-Out-Fähigkeit. Das Routing (Umverdrahtung) erfolgt bei 2.5D-Architekturen in Interposern mit durchgehenden Silizium-Vias (TSV) oder eingebetteten Brücken. Mittlerweile gibt es alternative High Density-Lösungen, wie organische Fan-Out Interposer, hybride Substrate, gegossene Formteile oder die monolithische vertikale 3D-Interconnect Technologie mit Face-to-Face-Platzierung von aktiven Chips. Direkte Diffusionsverbindungen Kupfer-zu-Kupferpad können den Pitch auf unter 10 µm reduzieren. Kombinationen von 2.xD- und 3D-Technologien, die heterogene 3D-Integration und die hohe Verbindungsdichte der Hybrid-Bond Technologie bieten viele neue Möglichkeiten.

Zurzeit reifen Konzepte wie aktiver Interposer oder Chiplet mit hochdichten Hybridbindungen (Wafer-zu-Wafer, Chip-zu-Wafer), hochdichten TSVs, monolithischen 3D-Bindungen mit Bauhöhen um 100 nm. Die sogenannten Chiplets, auf die Fabless-Unternehmen neuerdings umsteigen, sind unabhängige funktionale Schaltungsblöcke mit meist wiederverwendbaren Designs unterschiedlicher Anbieter, die im komplexen Multichipsystem verschaltet zusammenarbeiten.

Mustafa Badaroglu von der Huawei Technologies Deutschland GmbH Dresden betonte, dass für Mobilanwendungen neben More Moore Skalierungen auch Taktfrequenz-Skalierung, Fine-pitch 3D-Stapelung und zudem die Investausgaben kennzeichnend sind. In Face-to-Face Konfiguration, verbesserter Abschirmung und Möglichkeiten zur Miniaturisierung und Kostenreduktion ist hochintegrierte SiP-Technologie für das Packaging mobiler Anwendungen oder von Compilern für speicherzentriertes Rechnen gut geeignet, stellte Romain Freux (System Plus Consulting) fest. Untersucht wurden Technologietrends für Wearables, mm Wellen- (Mittel- und HF-, 5G- bis Sub-6G- bzw. unlizensierte Bänder) oder RF Front-End-Module bzw. SiP-Anwendungen für Forecast by Air Standards, in Mobilen, für 60 GHz-Radar und für den Seitenschutz (FO-WLP-Technologien).

3D- und heterogene Systemintegration – Marktanalysen

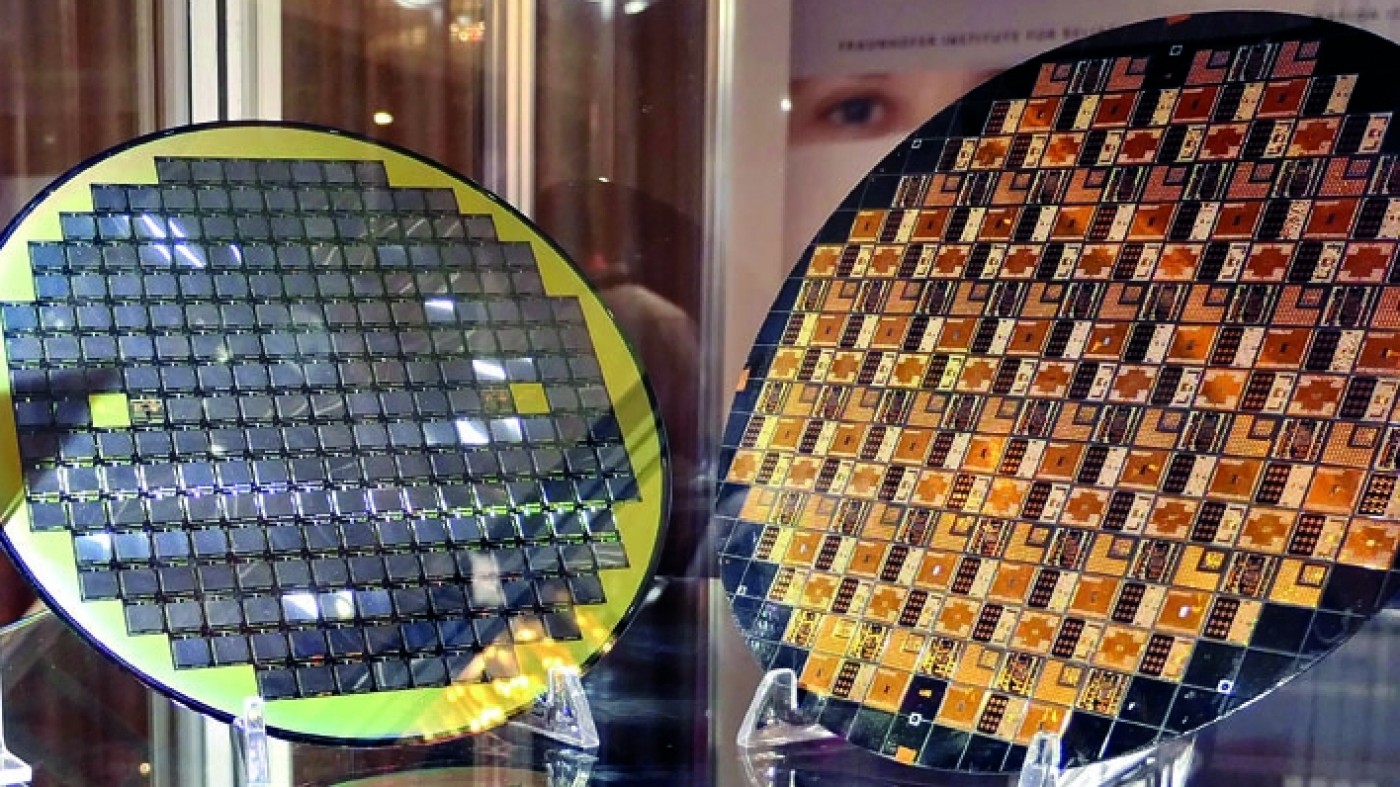

Der 3D-Gipfel mit den rund um den Globus angereisten Teilnehmern zeigte, wie vernetzt unsere Welt ist. Ein Vorteil, wenn es um Spitzentechnologien geht, deren Umsetzung Milliarden-Investitionen erfordern und die nur durch hochvolumige Anwendungen rentabel werden. Zu stemmen ist das nur in einer arbeitsteiligen und globalisierten Weltwirtschaft. Aber die Krise hat auch gezeigt, wie verletzlich das System ist. Die Marktanalysen, die auf dem Gipfeltreffen vorgestellt wurden, entstanden vor dem Ausbruch der Pandemie. Deshalb sind die damals geschätzten Steigerungsraten bis 8 % vielleicht illusorisch (oder doch noch real?). Treiber des Advanced Packaging-Geschäfts sind aber nach wie vor 3D-Integrationstechnologien. Diese verändern die Welt, weil der Wertanteil des Halbleiter-Packaging am Gesamtwert des Gerätes parallel zur Entwicklung PCB/Substrat und der CMOS-Entwicklung kontinuierlich steigt. Die Technologie dringt in viele Computerprodukte ein und macht das High-Performance-Computing HPC für Rechenzentren oder Cloud-Computing erst möglich. Der sich entwickelnde Electric Powertrain-Markt wird schnell boomen. Elektrofahrzeuge benötigen fünfmal mehr Elektronik und die Hybridtechnik sogar das Siebenfache. Dabei spielt die Entwicklung der Fahrassistenzsysteme (ADAS) für die Stufen Feet-off, Hands-off, Eyes-off, Mind-off eine besondere Rolle. Herausforderungen für die Heterogene Integration sind Steuerungen, Kameramodule (komplett als 3D-Systeme mit eingebetteter Kontrollelektronik), Image Prozessoren (SoC) oder Trägheitssensoren (3D-SiP-Technik). Wafer mit hochdichten Microball-Arrays und Si-Interposern vom Spezialisten für Packaging- und Wafer Backend-Services AEMtec GmbH

Wafer mit hochdichten Microball-Arrays und Si-Interposern vom Spezialisten für Packaging- und Wafer Backend-Services AEMtec GmbH

Die Marktentwicklungen für die Heterogene Integration und die Technologie-Roadmap stellten Emilie Jolivet vom französischen Marktforschungs-, Technologie- und Strategieberatungsunternehmen Yole Développement, Moyra McManus von ASML, Jean-Marc Yannou von der ASE Gruppe und Eelco Bergmann von der Advanced Semiconductor Engineering Inc. vor. Daniel Lieske zeigt die winzigen TSVs mit der Lupe

Daniel Lieske zeigt die winzigen TSVs mit der Lupe

Ausgefeilte Technologien

Funktionsoptimierte Wafer-Technologien führen zu komplexen Multi-Chip-Paketen mit hoher Geschwindigkeit und hoher Verbindungsdichte zwischen den Tools, denn Standard-BGA-Substrate sind nicht in der Lage, die erforderlichen E/A-Pitches für derart dichte Chip-zu-Chip Verbindungen zu erreichen. Bernd Waidhas von Intel Deutschland GmbH Dresden meint, dass bisher entwickelte PCB/IC-Substrattechnologien einen vielseitigen Werkzeugkasten für die Aufbau- und Verbindungstechnik multifunktionaler Module bieten. Die derzeitige Technologieentwicklung verläuft in den drei Achsen:

- 3D-IC (Performance, Leistung,Formfaktoren, Funktionalitäten)

- Skalierung (extensive Lithografie, neue Materialien und Speichertechnologien)

- Domainspezifische Architekturen (Software-/Hardware-Co-Design, virtuelles Prototyping).

Erstmals vorgestellt wurde eine sensationelle Brückentechnologie der Schweizer ZeroEC (Entwicklungszentrum in Tel Aviv/Israel) für 2.5D Chip-zu-Chip. Dabei erfolgt der Datentransport statt Elektronenleitung auf die „physikalisch effektivste Art und Weise“ ohne Energieverbrauch und mit einer viel höheren Bandbreite, erklärte Daniel Graf. „Diese patentierte Technologie, die keinen elektrischen Leiter benötigt, ermöglicht die größte Revolution in der Datenübertragung seit der Entdeckung der Glasfaseroptik und leitet eine neue Generation von IT-Produkten ein.“ Die Verbindungstechnologie ist kostengünstiger als Si-Interposer und erreicht eine Datenkapazität von 10 Gbps (Interposer 1 Gbps) bei einer Bandweite von 25 Tbps/mm (Interposer 1 Tbps/mm). Rafael Santos und Florian Roick stellten neue PCB-Prototyping-Technologien von LPKF vor

Rafael Santos und Florian Roick stellten neue PCB-Prototyping-Technologien von LPKF vor

Für das heterogene 3D-Packaging werden bei 2.5D-Technologien oder der Chip-Einbettungs-Technologie ECP der AT&S AG entweder Kavitäten vorgebildet und danach der Chip kontaktiert (Chip last) oder in Chip first mehrere Verdrahtungslagen mit Fan-Out gebondeten Chips im Wafer-Level gestapelt und über TSVs kontaktiert (All-in-One Packagen). Beide Technologien sind kombinierbar. Rafael Santos, hier mit Jacqes Perrocheau von LCP’S Engineering/Frankreich, hielt einen Vortrag zu neuen FO-Technologien

Rafael Santos, hier mit Jacqes Perrocheau von LCP’S Engineering/Frankreich, hielt einen Vortrag zu neuen FO-Technologien

„Die Entwicklung neuer Klassen von Materialien mit überlegenen Funktionalitäten sind unerlässlich, um neue Prozessschemata für das Wafer- und Panel-Level-Packaging zu ermöglichen“ betonte Kimberly Arnold (Brewer Science Ltd. USA). Erläutert wurden neue Technologien im Back-End-of-Line (BEOL) bzw. im Front-End-of-Line (FEOL), neue Interposertechnologien und Chip-zu-Chip Design-Ansätze. Ralph Schachler erläutert einen Multichipbonder der Finetech GmbH Co.KG für großflächiges (max. 600 x 600 mm) Wafer- und Panel-Packaging (FOPLP, FOWLP, Chipeinbettung)

Ralph Schachler erläutert einen Multichipbonder der Finetech GmbH Co.KG für großflächiges (max. 600 x 600 mm) Wafer- und Panel-Packaging (FOPLP, FOWLP, Chipeinbettung)

Vorgestellt wurden von Eric Beyne vom belgischen IMEC Zwischenverbindungen mit Pitches bis 100 nm / Dichte bis 108 #/mm2. Verbesserungen von System-Leistung und -Kosten sind durch Backside Power, Verringerung der FEOL-Verkabelung, Reduzierung der dynamischen IR VDD-/VSS-Verluste und rückseitige Entkopplungskondensatoren (PDN-Rausch-Reduzierung) auf Gehäuse-Ebene möglich. Die FEOL- bzw. BEOL-Prozesse werden kostengünstiger als 2.5D/3D-Designs mit Interposer sein, unterstützen aber nicht immer die technischen Anforderungen. Die Amkor Technology Inc. bietet eine ganze Reihe von Wafer-Level-Plattformen an. Dabei ist Low-Density Fan-Out das extrem flexible Arbeitspferd und die meistproduzierte WL-Package mit 10 Mrd. Einheiten.

Rafael Santos (LPKF Laser & Electronics AG) erläuterte die Active Mold Packaging-Technologie (2.5D) für Mold Fan-Out Packagen, eine lasergestützte Funktionalisierung und selektiv stromlose Kupfer-Plattierung von LDS-Epoxy-Moldmaterial (Laser Direkt Strukturierung). Anwendung finden auch laserinduziert tiefgeätzte bzw. gebohrte Dünnglassubstrate.

Ruurd Boomsma von der niederländischen BE Semiconductor Industries N.V. meint, dass aktuelle Verbindungstechnologien wie Thermokompressionsbonden weiterzuentwickeln und die Back-End-Werkzeuge für 2.5D und 3D auf die nächste Stufe der Genauigkeit und Produktivität zu bringen sind. Neue Technologien wie die direkte Verklebung (Direktbonden) sind sehr attraktiv, erfordern aber Präzision und vor allem Sauberkeit, weshalb Backend-Systeme auf Systeme der FEOL-Technologieklasse umgestellt werden müssen. Die zGlue Inc. verwendet eine aktive (programmierbare und smarte) Integrations-Plattform ZiP, bei der Chiplets in z-Richtung durch Kleben montiert werden. Christian Kjelde von der dänischen Polyteknik AS präsentierte eine flexible PVD-Bearbeitungsplattform für 200 mm Wafer

Christian Kjelde von der dänischen Polyteknik AS präsentierte eine flexible PVD-Bearbeitungsplattform für 200 mm Wafer

Die Lithographiesysteme der Dresdner ASML Germany GmbH ermöglichen eine Skalierung zu niedrigsten Kosten pro Wafer, erläuterte Steven Stehen und ergänzte: „ASML kreiert eine neue Welt, zurzeit ein Nanometer.“ Der Halbleiterauftragsfertiger Globalfoundries Glofo hat ein hybrides Wafer-Bond-Verfahren für die Face-to-Face Stapelung von Chips mit einem hybriden Bondpad-Interface weiterentwickelt. Ende April wurde gemeldet, dass für Glofo Dresden ein Zertifikat zur Herstellung von Chips mit einer Sicherheitsstufe nach dem internationalen Standard Common Criteria 3.1 vom Bundesamt für Sicherheit in der Informationstechnik erteilt wurde.

Über virtuelles Prototyping sprach Andreas Grassmann von Infineon Technologies AG. Im April hat der Konzern die seit 2019 geplante Übernahme der Cypress Semiconductor Corporation abgeschlossen. Durch die Akquisition kann das Unternehmen branchenweit das umfangreichste Portfolio für die Verbindung der realen mit der digitalen Welt sowie zum Gestalten der industriellen Digitalisierung anbieten.

Heterogene System-integration in 3D

Miniaturisierung und Integration unterschiedlicher Speicher-, Prozessor- oder Sensor-/Aktor-Bauteile führt zu funktionell umfangreicheren Systemen und integriertem Packaging (IP-Partitionierung). 3D-gestapelt werden Speicher-Chips, Prozessoren, Sensoren, Mikrosender und andere Bauteile übereinander und senkrecht durchkontaktiert. Bisher ungeahnte Möglichkeiten der Skalierung, wie in der Fokus-Ebene angeordnete 3D-Bildgeber oder Neurorechentechnik, eröffnen sich.

Neue SoC-Entwicklungen sind z.B. die Photonik-Integration auf CMOS auf einer SiN-Plattform von STMicroelectronics, ein Packaging-Konzept für einen 4-Seiten Gapless-Sensor der Dectris AG oder die heterogene Integration von 5G-Komponenten durch das Fraunhofer-IZM. Die Fraunhofer-IPMS-Ausgründung Arioso-Systems GmbH erhielt im April Risikokapital für die Markteinführung einer Mikrochip-Technologie für einen Lautsprecher nach einem siliziumbasierten Schallwandlerprinzip (Nanoscopic Electrostatic Drive-Prinzip).

Ende 2019 wurde von Bosch und Globalfoundries das europäische Entwicklungs-Verbundprojekt ‚Ocean12‘ gestartet, das auf besonders energiesparende künstliche Augen und Nerven für autonom fahrende Autos oder Flugtaxis zielt. 27 europäische Projektpartner, darunter die TU Dresden und das Fraunhofer-IPMS werden neben Umfeld-Sensoren für Lidar-, Radar- und optische Erkennung auch Mikroprozessoren entwickeln, die gesammelte Sensordaten unmittelbar in Steuerbefehle für Bremsen, Steuerung und Antrieb übersetzen. Dazu werden Sensoren und Auswertelektronik auf jeweils einem SoC integriert.

Die chinesische Joyson Electronic Corp. verlegt ihren Hauptsitz von Dresden ins chinesische Ningbo und benannte ihren bisherigen Leitbetrieb Preh Car Connect im Mai zu Joynext GmbH um. Dresden bleibt dabei aber zentraler F und E-Standort für Autoelektronik. Der Konzern will „neue Ideen noch intensiver auf dem ausgesprochen technologie-affinen chinesischen Markt erproben“ betonte Konzernchef Yuan Kevin Liu. Dieser Markt sei für das Unternehmen wichtiger und außerdem „sind die Chinesen offener für neue Technologien“. Zu Joynext gehören neben Ningbo und Dresden weitere Standorte von Joyson in Shanghai und Dalian in China, eine Fabrik im polnischen Oborniki sowie Teams in Japan und Korea.

Das Licht am Ende des Corona-Tunnels wird heller. Deutschland hat, soviel scheint sicher, die erste Welle der weltweiten Pandemie vergleichsweise glimpflich überstanden. Nun beginnt der Wiederaufbau. All das, was in den vergangenen Monaten unter der Last des Shutdowns leiden musste, berappelt sich, sofern dies abseits globalisierter Strukturen möglich ist. Aber in zahlreichen Nationen lähmt Corona noch immer die Wirtschaft und Industrie. In internationalen Lieferketten knirscht es daher weiterhin. Um Corona-gestörte Lieferketten wieder zu stabilisieren, hatte das Dresdner Netzwerk ‚Smart Systems Hub‘ seinen ersten ‚Digitalen Thin[gk]athon‘ Anfang April 2020 zum Thema Supply Chain Management durchgeführt. Michael Kaiser, Managing Direktor der Smart Systems Hub GmbH sagte dazu: „die Krise birgt auch Chancen, gemeinsam neue Wege zu gehen und Prozesse ganz neu zu denken. Die Notwendigkeit, ausgetretene Pfade zu verlassen, war noch nie so groß wie heute.“

Quellen:

3D & Systems Summit:

www.semi.org/eu/connect/events/3d-and-systems-summit

Silicon Saxony e.V., www.silicon-saxony.de

Nachrichtenportal Oiger, www.computer-oiger.de