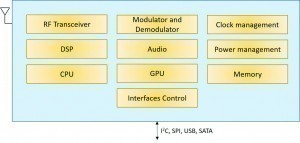

Hochfrequente (HF) integrierte Schaltkreise (IC) sind das Herzstück einer Vielzahl heutiger Anwendungen und Dienste, darunter drahtlose lokale Netzwerke (LANs), Mobilfunk, globale Positionierungssysteme (GPS), Automobilelektronik und Internet der Dinge (IoT). Mit den jüngsten Fortschritten im Bereich der Prozesstechnologie, wie der Entwicklung hochohmiger Substrate, der Integration passiver Bauelemente am Halbleiter-Wafer und der Integration bipolarer Übergangstransistoren (BJTs) und komplementärer Metalloxid-Halbleitertechnologien (CMOS) in eine neue BiCMOS-Technologie in Kombination mit allgemeiner Technologieskalierung, hat sich die Integration von HF-Komponenten von einem rein diskreten Komponentenraum zu kompakteren IC-Lösungen mit geringerer Leistung, die gute Geräuschzahlen (NF) und Linearität für ein breites Frequenzspektrum bieten, weiterentwickelt. Abb. 1: Konzeptionelles Blockdiagramm typischer Module moderner HF-SoCs

Abb. 1: Konzeptionelles Blockdiagramm typischer Module moderner HF-SoCs

Diese Entwicklung verstärkte auch den Trend zu System-on-Chip-Designs (SoC), bei denen das HF-Frontend auf demselben IC wie der digitale Basisband-Prozessor und die Speichermodule vorhanden ist (Abb. 1) [1]. Nebenstromblöcke wie Analog-Digital-Wandler (ADCs), Digital-Analog-Digital-Wandler (DACs), Phasenverriegelungsschleifen (PLLs), Frequenzsynthesizer, Spannungsreferenzen und Bias-Schaltkreise (z. B. Bandspalte und Stromspiegel) werden nun gemeinsam mit den HF-Front-End-Blöcken am gleichen Halbleiter-Wafer hergestellt. Die Erweiterung der Baseband-Integration verbessert zwar die Leistung und Effizienz erheblich, die zusätzliche Komplexität führt jedoch zu erhöhten Herausforderungen bei der Verifizierung dieser HF-ICs.

Werfen wir nun einen genaueren Blick auf die Arten von Kontrollen, die für diese Konstruktionen verwendet werden können, um die Auswirkungen dieser Herausforderungen auf Zuverlässigkeit und Leistung zu finden und zu überwinden, und überlegen wir, wie fortschrittliche Tools und Techniken zur elektronischen Designautomatisierung (EDA) Konstrukteuren dabei helfen, eine genaue, schnelle, automatisierte Verifizierung und Konstruktion für die Fertigungsoptimierung von HF-ICs sicherzustellen.

Herausforderungen bei der HF-IC-Verifizierung

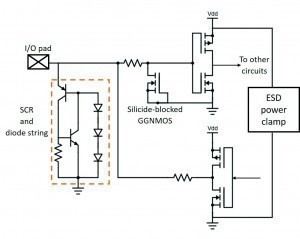

Für einen bestimmten Prozess bieten Hersteller in der Regel verschiedene Bauelementetypen und Bauelementevarianten für Komponenten wie Dioden, Widerstände, Kondensatoren, Feldeffekttransistoren (FET), BJT usw. an. Diese Bauelementetypen oder Varianten weisen unterschiedliche Eigenschaften auf, wie z. B. Grenzspannung (Vt), Durchschlagspannungen und -ströme, thermische Widerstände, Rauschzahlen, zulässige Bauelementeabmessungen usw. [3]. Je nach Bauelementeeigenschaften und Konstruktionsregeln des Herstellers ist es wünschenswert (und in einigen Fällen auch zwingend erforderlich), bestimmte Bauelemente in bestimmten Schaltungen zu verwenden. Abb. 2: Diodenstrang-gesteuerter SCR zum ESD-Schutz eines HF-I/O-Pads

Abb. 2: Diodenstrang-gesteuerter SCR zum ESD-Schutz eines HF-I/O-Pads

Metalloxid-Halbleiter-Feldwirkungstransistoren (MOSFETs) werden beispielsweise wegen ihrer Leistungsmerkmale häufig in HF-ICs eingesetzt. Während es generell wünschenswert ist, kürzere Kanallängen für Stromkreise mit hohen Leistungsanforderungen zu verwenden, ist es nicht in allen Fällen ideal, Bauelemente mit minimaler Länge zu verwenden. Wenn ein Entwicklungsteam Stromquellen aufbaut, um den Ausgangswiderstand zu erhöhen, verwendet es in der Regel Bauelemente mit Nicht-Mindestlängen [4].

Für Anwendungen, die eine Anbindung an ältere I/O-Stromkreise mit höherer Spannung erfordern, schreiben Herstellerregeln normalerweise die Verwendung von Bauelementen mit einer bestimmten Gateoxiddicke vor, die dem starken elektrischen Feld standhalten können, das durch die höheren Spannungen erzeugt wird, ohne einen oxidbedingten dielektrischen Ausfall zu verursachen. Diese Bauelemente unterscheiden sich zumeist stark von den Bauelementen, die in einem hochdichten On-Chip-Speicher-Array verwendet werden.

Abbildung 2 zeigt einen per Diodenstring gesteuerten siliziumgesteuerten Gleichrichter (SCR), ein häufig verwendetes Schutznetzwerk gegen elektrostatische Entladungen (ESD) für HF-Anwendungen [5]. Auf einem Chip mit vielen I/O-Pads erfordert jedoch nur ein Bruchteil der I/O-Pads, die HF/High-Speed sind, spezielle ESD-Schutzstrukturen. Es ist nicht ungewöhnlich, dass Konstrukteure mehrere Spezifikationen überprüfen müssen, um sicherzustellen, dass alle I/O-Pads über geeignete ESD-Schutzstrukturen verfügen, und alle nicht konformen kennzeichnen:

Nur HF-Pads dürfen einen bipolaren Schutz haben, wobei ein weiterer bipolarer Transistor und ein drei Diodenstring zwischen Sockel und Erde angeschlossen sein müssen. Andere I/O-Pads verwenden herkömmliche ESD-Strukturen.

An diese HF-Pads angeschlossene Gates müssen über einen geerdeten Siliziumblock-NMOS-Schutz mit einem geladenen Bauelementewiderstand (CDM) verfügen. An diese HF-Pads angeschlossene Ausgangstreiber müssen einen Schutzwiderstand mit einem Wert zwischen 40 und 60 Ohm haben. Der geerdete Gate NMOS-Schutz zwischen Strom- und Erdnetzen muss eine Mindestbreite von 400 µm aufweisen.

HF-Stromkreise reagieren auch sehr empfindlich auf parasitäre Elemente und Layout-abhängige Effekte. Um einen robusten Stromkreis zu erreichen, der unter verschiedensten Betriebsbedingungen zuverlässig arbeitet, sind sowohl Vor- als auch Nach-Layout-Simulationen unerlässlich, so dass überprüft werden kann, ob alle Parameter den Designspezifikationen entsprechen. Dieser Nachweis erfordert oft viele Arten von Simulationsanalysen, darunter Rauschen, Linearität, Stromverbrauch und Stabilität. Je nach Schaltungstyp, Art der durchzuführenden Analyse und Anwendung wird entweder eine Zeitdomänen- oder eine Frequenzdomänensimulation verwendet. All diese Simulationen sind jedoch computerintensive Operationen, die sowohl teuer (aufgrund der benötigten Hardware) als auch zeitaufwendig sind.

Da diese Schaltungen so akut empfindlich auf die Auswirkungen von Störungen reagieren, müssen die Schaltungsentwickler eng mit den Masken-Layout-Ingenieuren zusammenarbeiten, um sicherzustellen, dass die Schaltkreisimplementierung die Auswirkungen von Störungen auf den Schaltungsbetrieb minimiert. Insbesondere das Einfügen von Füllmustern in das Layout ist entscheidend. Während Füllung bei niedrigeren Frequenzen nur die Kapazität beeinflusst, kann sie bei höheren Frequenzen Widerstand und Induktivität erheblich verändern [2].

Die Durchführung von Bauelemente- und ESD-Prüfungen mit optischen Inspektions- oder herkömmlichen Werkzeugen zur einmaligen Überprüfung ist nicht nur umständlich und zeitaufwendig, sondern auch fehleranfällig. SPICE-Tools erfordern eine präzise Einrichtung, um geringfügige Abweichungen zu erkennen, ein Prozess, der anfällig für menschliche Fehler ist. Gleichzeitig ist es aufgrund des reinen Umfangs und der Komplexität moderner SoC-Designs nicht immer machbar, dynamische Simulationen auf Vollchip-Ebene durchzuführen, um solche Abweichungen zu erkennen. Während Simulationen notwendig sind, um sicherzustellen, dass die Schaltungen eine Basisleistung erreichen, kann der Aufwand an Zeit und Ressourcen reduziert werden, indem Bauelementetyp, Bauelementeeigenschaften, Ausrichtung, Symmetrie und andere kritische Auslegungsparameter überprüft werden, bevor Laufzeitsimulationen durchgeführt werden. Indem sichergestellt wird, dass ein Entwurf vor der Durchführung von Simulationen bereits zur Genauigkeit tendiert, wird eine schnellere Durchlaufzeit sichergestellt. Dabei werden sowohl die Anzahl der Simulationswiederholungen als auch die Zeit, die für die Korrektur von Problemen nach der Simulation aufgewendet wird, minimiert.

Automatisierte Verifizierungslösungen, die zuverlässig und schnell überprüfen können, ob das Design von HF-ICs sowohl technologische als auch benutzerspezifische Anforderungen erfüllt, sind entscheidend, um sicherzustellen, dass Entwicklungsunternehmen zuverlässige Produkte termingerecht liefern können.

Prüfung der Designtopologie

Es stehen jetzt Verifizierungstools für elektronische Designautomatisierung (EDA) zur Verfügung, die speziell für die topologische Prüfung von Schaltkreisen entwickelt wurden, um den komplexen Verifizierungsanforderungen von HF-IC-Konstruktionen gerecht zu werden. Wir gehen die wichtigsten Verifizierungsstrategien für HF-ICs durch und verwenden die Zuverlässigkeitsplattform Calibre PERC von Mentor, einem Unternehmen von Siemens, um die automatisierten Verifizierungsfunktionen zu demonstrieren, die HF-IC-Konstrukteuren zur Verfügung stehen.![Abb. 3: Ein volldifferenzierter Mischer [8] Abb. 3: Ein volldifferenzierter Mischer [8]](/images/stories/Abo-2020-11/thumbnails/thumb_plus-2020-11-0072.jpg) Abb. 3: Ein volldifferenzierter Mischer [8]

Abb. 3: Ein volldifferenzierter Mischer [8]

Regelprüfungen

Tools zur Zuverlässigkeitsprüfung können ein Schaltungsdesign mit den vom Hersteller bereitgestellten Regelkriterien sowie mit den spezifischen Anforderungen des Entwicklungsunternehmens prüfen. Konstrukteure können die von den Herstellern bereitgestellten Regeln anwenden oder bei Bedarf ihre eigenen, einfachen Regeln erstellen, um sicherzustellen, dass bei Bedarf die richtige Art von Schaltungsstrukturen verwendet wird und dass entsprechende Verbindungen mit diesen Strukturen hergestellt werden. Die Zuverlässigkeitsplattform Calibre PERC kann beispielsweise mehrere Eigenschaften von Bauelementen (z. B. Länge, Breite, Vt-Typ usw.) überprüfen und Mustervergleiche durchführen, um die Eigenschaften zu verifizieren und die korrekte Konstruktion bestimmter Schaltungsstrukturen zu überprüfen.

Diese Regelprüfungen beschränken sich nicht nur auf den gängigen Mainstream-CMOS-Prozess. Hersteller, Konstrukteure und CAD-Ingenieure können Einschränkungen definieren und Regelprüfungen für jeden Bauelementeprozess durchführen, wie etwa HeteroJunction-Bipolartransistoren oder HF-Silizium-Isolatoren (HF-SOIs), die beide häufig in HF-Konstruktionen verwendet werden.

HF/Analog-Layoutprüfung

Sowohl die Leistung als auch die Zuverlässigkeit von HF-Designs sind eng mit der Layout-Implementierung verknüpft. Sobald das physische Layout eines HF-Designs abgeschlossen ist und die Schaltungsimplementierung durch einen Vergleich von Layout und Schematic (LVS) validiert wurde, müssen viele mögliche layoutabhängige Auswirkungen analysiert werden, um Zuverlässigkeits- und Leistungsprobleme zu vermeiden. Einige dieser Effekte können bei der Simulation nach Erstellung des Layouts erfasst werden, andere werden erst sichtbar, wenn das Design auf dem Silizium ist. Daher ist es für den Markterfolg des Chips entscheidend, sie bei der Designverifizierung zu finden und zu beseitigen [6].

HF/analoge Masken-Layout-Designer befolgen in der Regel verschiedene Vorsichtsmaßnahmen bei der Gestaltung des Layouts, welche die Auswirkungen von Überlagerungen, Diskrepanzen, Rauschen usw. minimieren [7]. Zu den gängigen Techniken, die von diesen Konstrukteuren angewendet werden, gehören die Symmetrie der Bauelemente, die Übereinstimmung der aktuellen Ausrichtung, das Einsetzen von Dummy-Bauelementen, der gemeinsame Schwerpunkt und der Abstand zwischen den Bauelementen sowie die Anpassung elektrischer Parameter [6].

Differenzialkreise werden beispielsweise häufig in HF-Konstruktionen für geräuscharme Verstärker, Mischer, Leistungsverstärker und Ladepumpen verwendet (Abb. 3). In einem volldifferenzierten Stromkreis beeinträchtigt jede fehlende Symmetrie zwischen den Bauelementen ihre Fähigkeit, das Rauschen des Eingangs-Gleichtakts zu unterdrücken, führt zu den genannten Eingangs-Offsets und verursacht eine endlose gleichmäßige Verzerrung der Reihenfolge [7]. Aufgrund dieser Auswirkungen ist es wichtig, die Stromkreise rechtzeitig auf mögliche Asymmetrien zu überprüfen.

Um die Wirkung der Asymmetrie der Differentialstruktur zu verbessern, fügen Layout-Designer Dummy-Bauelemente auf beiden Seiten der funktionalen Bauelemente hinzu.

STI-Stress und WPE

Zuverlässigkeit ist bei der Entwicklung von HF-Schaltungen ein wichtiger Faktor für den Markterfolg. Viele HF-Produkte, wie sie in Anwendungen wie Luft- und Raumfahrt, Satellitenkommunikation, Militär und Verteidigung zum Einsatz kommen, arbeiten in rauen Umgebungen und/oder müssen über längere Zeiträume unter hohen Beanspruchungen betrieben werden, wobei sich die Kriterien für die Zeit bis zum Ausfall dieser Produkte teilweise auf mehrere Jahrzehnte erstrecken. Angesichts dieser Betriebsbedingungen und strenger Anforderungen stehen Konstrukteure bei der Auslegung von HF-Schaltungen strengen Kriterien für IC-Zuverlässigkeit gegenüber. Abb. 4: (a) Füllung in den ausgeschlossenen Bereichen in der Nähe empfindlicher Netze, (b) Füllung, die mit dem kombinierten Calibre PERC/Calibre YieldEnhancer erzeugt wird, der das Eindringen in die kritischen Netze verhindert

Abb. 4: (a) Füllung in den ausgeschlossenen Bereichen in der Nähe empfindlicher Netze, (b) Füllung, die mit dem kombinierten Calibre PERC/Calibre YieldEnhancer erzeugt wird, der das Eindringen in die kritischen Netze verhindert

Daher ist es wichtig, die Auswirkungen layoutabhängiger Effekte wie die Belastung durch flache

Grabenisolierung (STI) und Well-Näherungseffekte (WPE) zu berücksichtigen, die schwerwiegende Folgen für die Zuverlässigkeit und erwartete Lebensdauer von HF-ICs haben können. Konstrukteure müssen ihre Ursachen verstehen und bei der Implementierung von HF-Schaltungen auf anfällige Layout-Strukturen achten und geeignete Layout-Techniken anwenden, um die Auswirkungen dieser unerwünschten Phänomene zu mindern.

Die Auswirkungen von STI-Spannung können reduziert werden, indem Dummy-Bauelemente hinzugefügt und das Layout einheitlich und symmetrisch gestaltet wird [10].Um WPE zu minimieren, sollten alle Bauelemente, die sich voraussichtlich ähnlich verhalten und altern, aufeinander abgestimmt werden und den gleichen Layout-Kontext haben, einschließlich des Abstands zur Wannenkante. Die Überprüfung, ob diese Layout-Praktiken durch Sichtprüfungen oder Layout-Reviews eingehalten werden, ist nicht ideal, da es leicht zu Abweichungen kommt. Aufgrund der Größe und Komplexität der heutigen Designs ist es zudem schwierig, eine ausreichende Abdeckung zu gewährleisten.

Die Zuverlässigkeitsplattform Calibre PERC bietet eine konsistente, automatische Erkennung der subtilsten Fehler in einer Layout-Implementierung, wie z. B. Bauelementeasymmetrie und Nichtübereinstimmungen, fehlende Dummy-Bauelemente oder Ungenauigkeit in einem Common-Centroid-Layout. Im Rahmen des Analog Constraint Check Flow Calibre PERC definieren Konstrukteure die Prüfungen, die sie durchführen wollen, und wählen die Bauelemente aus, auf denen die Prüfungen durchgeführt werden sollen. Die Zuverlässigkeitsplattform Calibre PERC führt die Prüfungen an den angegebenen Bauelementen durch und zeigt die Ergebnisse in der Benutzeroberfläche Calibre RVE an, wobei die Abweichungen zur einfachen Anzeige und schnellen Korrektur hervorgehoben werden.

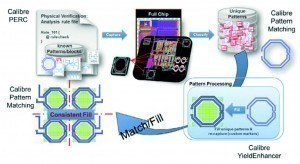

HF/analog Layout-Füllung

Um die Dickenunterschiede bei Kupferverbindungen zu verringern, die sich aus dem Prozessschritt der chemischen mechanischen Planarisierung in der Fertigung ergeben, wird Füllung in die Konstruktion eingefügt. Schwimmende Füllung wirkt sich jedoch auf die Verbindungskapazität aus und ändert die Signalverzögerung der Verbindungen [2]. Wenn die Füllung sich auf kritische Netze der Konstruktion auswirkt, kann sie die Leistung von Hochgeschwindigkeits- und HF-Konstruktionen erheblich reduzieren. Mit zunehmender Frequenz wird der Einfluss auf Widerstand und Induktivität erheblich. Oberhalb von 10 GHz zeigt sich der Wirbelstromverlust durch Füllung als Erhöhung des Widerstandes [2] und kann nicht mehr ignoriert werden. Abb. 5: Orientierungsbewusster Füllablauf sorgt für ein symmetrisches und gleichmäßiges Füllmuster um die Induktoren

Abb. 5: Orientierungsbewusster Füllablauf sorgt für ein symmetrisches und gleichmäßiges Füllmuster um die Induktoren

On-Chip-Spiralinduktoren werden häufig in HF-Schaltungen verwendet, ihre elektrische Leistung kann aber auch durch Füllung beeinträchtigt werden [11]. Die Füllformgröße und der Abstand der Füllung zum Signaldraht des Induktors beeinflussen den Qualitätsfaktor (Q-Faktor) und die Resonanzfrequenz des Induktors.

Daher ist es von entscheidender Bedeutung, den Füllprozess zu optimieren, durch eine konsistente Füll-anordnung, einen ausreichenden Abstand der Füllformen von den kritischen Netzen und die Bestimmung der optimalen Füllformgröße, um die Leistung zu maximieren, die Verbindungsverluste zu minimieren, den gewünschten Q-Faktor und die Resonanzfrequenzen für Induktoren zu erreichen und den Ertrag zu verbessern.

Designteams können den Prozess der Füllung optimieren, indem sie mit automatischen Beschriftungs- und Fülltechniken Füllformen konsistent in das Design einfügen und verhindern, dass Füllformen in Bereiche eindringen, die vom Abfüllprozess ausgeschlossen werden müssen (Abb. 4). Konstrukteure können die Zuverlässigkeitsplattform Calibre PERC nutzen, um die Beschriftung kritischer Netze in ihrem Design vor dem Schritt der Füllungserzeugung zu automatisieren. Der Calibre YieldEnhancer SmartFill-Prozess erkennt und erfüllt dann automatisch alle Einschränkungen, die durch den Ausschluss von Marker-Layern im Layout auferlegt werden. Diese Kombination von Tools bietet einen enormen Vorteil gegenüber herkömmlichen Füllabläufen, bei denen Konstrukteure Füllformen entweder manuell um kritische Netze herum entfernen oder diese kritischen Netze manuell kommentieren müssen, bevor die Füllung hinzugefügt wird, beides langsame, iterative und fehleranfällige Prozesse.

Wenn dieser Kombination die Funktion Calibre Pattern Matching hinzugefügt wird, kann ein automatischer, orientierungsbewusster Füllablauf gewährleistet werden, der zu einer konsistenten Füllung ohne Verschiebungen des Füllmusters für Elemente wie Induktoren, Gatter, Zellen usw. führt. Designer erfassen einzigartige Konfigurationen als Muster, füllen jedes Muster so effizient und effektiv wie möglich und speichern dann die gefüllte Form als neues Muster. Sobald das ursprüngliche Muster im Design gefunden wird, wird es automatisch entsprechend dem gespeicherten Füllmuster gefüllt, um Konsistenz im gesamten Layout zu gewährleisten, wie in Abbildung 5 [12] gezeigt.

Zusammenfassung

Konstrukteure von HF-ICs stehen aufgrund der technologischen Skalierung, der zunehmenden Integration mit Basisband und digitalen Blöcken und der Notwendigkeit, mehrere Protokolle zu unterstützen, in Kombination mit der Nachfrage nach kompakteren Bauelementen mit geringerem Energieverbrauch, höherer Bandbreite und Durchsatzanforderungen, vor einer zunehmenden Anzahl von Verifizierungsproblemen. Die Nutzung manueller Techniken und traditioneller simulationsbasierter Ansätze ist suboptimal, was zu erhöhten Verifikations-Zyklen und potenziell minderwertigen Designs führt, die sich in den heutigen schnelllebigen und anspruchsvollen Märkten als kostspielig erweisen können. Indem sie die fortschrittlichen Funktionen der EDA-Zuverlässigkeitsprüfungstools nutzen, um eine Vielzahl komplexer Verifizierungsprozesse in jeder Phase des Designs von der Schema- und Layout-Prüfung zu automatisieren und eine Kombination von Werkzeugfunktionen zur Standardisierung und Optimierung der Befüllung nach dem Layout zu nutzen, können die Konstrukteure von HF-ICs die Verifizierungszeiten drastisch verkürzen und gleichzeitig sicherstellen, dass ihre Designs während der gesamten Lebensdauer der Produkte, in denen sie verwendet werden, zuverlässig ihre Designspezifikationen erfüllen.

Zur Person

Neel NatekarNeel Natekar ist Senior Product Engineer in der Abteilung Design to Silicon von Mentor. Er studierte an der Universität Mumbai und an der Universität Michigan. Bevor Natekar zu Mentor kam, arbeitete er als Konstrukteur bei Qualcomm und konzentrierte sich auf Stromversorgungslösungen für kundenspezifische CPUs. Er ist erreichbar unter Diese E-Mail-Adresse ist vor Spambots geschützt! Zur Anzeige muss JavaScript eingeschaltet sein!

Neel NatekarNeel Natekar ist Senior Product Engineer in der Abteilung Design to Silicon von Mentor. Er studierte an der Universität Mumbai und an der Universität Michigan. Bevor Natekar zu Mentor kam, arbeitete er als Konstrukteur bei Qualcomm und konzentrierte sich auf Stromversorgungslösungen für kundenspezifische CPUs. Er ist erreichbar unter Diese E-Mail-Adresse ist vor Spambots geschützt! Zur Anzeige muss JavaScript eingeschaltet sein!

Referenzen:

- Qualcomm Announces World’s Most Power-Efficient NB2 IoT Chipset,' Qualcomm. April 16, 2020. https://www.qualcomm.com/news/releases/2020/04/16/qualcomm-announces-worlds-most-power-efficient-nb2-iot-chipset

- Tsuchiya, Akira; Onodera, Hidetoshi, ‚Effect of Dummy fills on characteristics of passive devices in CMOS millimeter-wave circuits', 2009 IEEE 8th International Conference on ASIC, vol., p.296 – 299. https://ieeexplore.ieee.org/document/5351449/

- High-performance SiGe BiCMOS solutions,' GLOBALFOUNDRIES. https://www.globalfoundries.com/sites/default/files/sige_hp_pb_2020-0212web.pdf

- Lee, Thomas H. The Design of CMOS Radio-Frequency Integrated Circuits. 2nd ed. Cambridge: Cambridge University Press, 2003. doi:10.1017/CBO9780511817281

- White Paper 1: A Case for Lowering Component Level HBM ESD Specifications and Requirements,' Industry Council on ESD Target Levels, June 2018, Revision 4.0. https://www.esdindustrycouncil.org/ic/docs/industry%20council_esd_target_levels_whitepaper1_rev4.0_ june2018%20final.pdf

- Hossam Sarhan and Alexandre Arriordaz, ‚Automated Constraint Checks Enhance Analog Designs Reliability', Mentor, a Siemens Business. Oct. 2018.

- B. Razavi, Design of Analog CMOS Integrated Circuits. New York: McGraw-Hill, 2001.

- N. Natekar, V. Vasudevan, A. Viswanath, ‚A 5.2GHz RF Front-End,' University of Michigan, EECS 522 Final Project, 2011. https://www.eecs.umich.edu/courses/eecs522/w11/project/group8report.pdf

- S.K. Marella, S.S. Sapatnekar, ‚The impact of shallow trench isolation effects on circuit performance,' 2013 IEEE/ ACM International Conference on Computer-Aided Design (ICCAD). San Jose, CA, 2013, pp. 289-294, doi: 10.1109/ICCAD.2013.6691134

- V. Moroz, et al., ‚Stress-aware design methodology,' 7th International Symposium on Quality Electronic Design (ISQED’06), San Jose, CA, 2006. doi: 10.1109/ISQED.2006.124

- Akira Tsuchiya and Hidetoshi Onodera, ‚Dummy fill Insertion considering the effect on high-frequency characteristics of spiral inductors,' 2008 IEEE MTT-S International Microwave Symposium Digest, Atlanta, GA, USA, 2008, pp. 787-790. doi: 10.1109/MWSYM.2008.4632950

- Sherif Hany, ‚Integrating Pattern Matching with DFM Properties to Enhance and Optimize Layouts', Mentor, a Siemens Business. Nov. 2017.