Improve the reliability and performance of RF ICs with advanced EDA technology: With advanced features of EDA reliability verification tools, a variety of complex verification processes can be automated at any stage of the design. This enables RF IC designers to drastically reduce verification times.

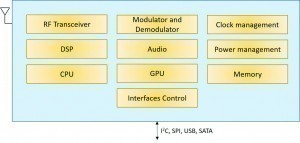

Radio frequency (RF) integrated circuits (ICs) are at the heart of a wide range of today's applications and services, including wireless local area networks (LANs), cellular communications, global positioning systems (GPS), automotive electronics and the Internet of Things (IoT). With recent advances in process technology, such as the development of high impedance substrates, the integration of passive devices on the semiconductor wafer and the integration of bipolar junction transistors (BJTs) and complementary metal oxide semiconductor (CMOS) technologies into a new BiCMOS technology combined with general technology scaling, the integration of RF components has evolved from a purely discrete component space to more compact, lower power IC solutions that offer good noise figures (NF) and linearity for a wide frequency spectrum. Fig. 1: Conceptual block diagram of typical modules of modern RF SoCs

Fig. 1: Conceptual block diagram of typical modules of modern RF SoCs

This development also reinforced the trend towards system-on-chip (SoC) designs, where the RF front end is present on the same IC as the digital baseband processor and memory modules(Fig. 1) [1]. Off-line blocks such as analog-to-digital converters (ADCs), digital-to-analog-to-digital converters (DACs), phase-locked loops (PLLs), frequency synthesizers, voltage references and bias circuits (e.g. bandgaps and current mirrors) are now co-fabricated with the RF front-end blocks on the same semiconductor wafer. While the addition of baseband integration significantly improves performance and efficiency, the added complexity leads to increased challenges in verifying these RF ICs.

Let's now take a closer look at the types of controls that can be used for these designs to find and overcome the impact of these challenges on reliability and performance, and consider how advanced electronic design automation (EDA) tools and techniques are helping designers ensure accurate, fast, automated verification and design for RF IC manufacturing optimization.

Challenges in RF IC verification

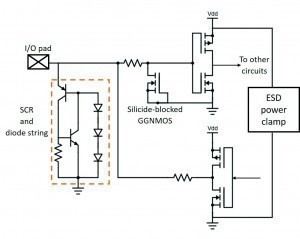

For a given process, manufacturers typically offer different device types and device variants for components such as diodes, resistors, capacitors, field-effect transistors (FET), BJT, etc.. These component types or variants have different properties, such as limit voltage (Vt), breakdown voltages and currents, thermal resistances, noise figures, permissible component dimensions, etc. [3]. Depending on the component characteristics and the manufacturer's design rules, it is desirable (and in some cases mandatory) to use certain components in certain circuits. Fig. 2: Diode string-controlled SCR for ESD protection of an RF I/O pad

Fig. 2: Diode string-controlled SCR for ESD protection of an RF I/O pad

Metal oxide semiconductor field-effect transistors (MOSFETs), for example, are often used in RF ICs because of their performance characteristics. While it is generally desirable to use shorter channel lengths for circuits with high power requirements, it is not ideal to use minimum length devices in all cases. When a design team builds power sources to increase output resistance, they typically use non-minimum length devices [4].

For applications that require interfacing to higher voltage legacy I/O circuits, manufacturer rules typically dictate the use of devices with a specific gate oxide thickness that can withstand the strong electric field generated by the higher voltages without causing oxide-induced dielectric failure. These devices are usually very different from the devices used in a high-density on-chip memory array.

Figure 2 shows a diode string controlled silicon controlled rectifier (SCR), a commonly used electrostatic discharge (ESD) protection network for RF applications [5]. However, on a chip with many I/O pads, only a fraction of the I/O pads that are RF/high-speed require special ESD protection structures. It is not uncommon for designers to have to review multiple specifications to ensure that all I/O pads have appropriate ESD protection structures and mark all non-compliant ones:

Only RF pads may have bipolar protection, with another bipolar transistor and a three diode string connected between the socket and ground. Other I/O pads use conventional ESD structures.

Gates connected to these RF pads must have grounded silicon block NMOS protection with a charged device resistor (CDM). Output drivers connected to these RF pads must have a protective resistor with a value between 40 and 60 ohms. The grounded gate NMOS protection between power and ground networks must have a minimum width of 400 µm.

RF circuits are also very sensitive to parasitic elements and layout-dependent effects. In order to achieve a robust circuit that works reliably under a wide range of operating conditions, both pre- and post-layout simulations are essential so that it can be verified that all parameters meet the design specifications. This verification often requires many types of simulation analysis, including noise, linearity, power consumption and stability. Depending on the type of circuit, the type of analysis to be performed and the application, either a time-domain or a frequency-domain simulation is used. However, all these simulations are computer-intensive operations that are both expensive (due to the hardware required) and time-consuming.

Because these circuits are so acutely sensitive to the effects of disturbances, circuit designers must work closely with mask layout engineers to ensure that circuit implementation minimizes the effects of disturbances on circuit operation. In particular, the insertion of fill patterns into the layout is critical. While fill only affects capacitance at lower frequencies, it can significantly alter resistance and inductance at higher frequencies [2].

Performing component and ESD testing with optical inspection or conventional one-time inspection tools is not only cumbersome and time-consuming, but also error-prone. SPICE tools require a precise set-up to detect minor deviations, a process that is prone to human error. At the same time, due to the sheer scale and complexity of modern SoC designs, it is not always feasible to perform dynamic simulations at the full-chip level to detect such deviations. While simulations are necessary to ensure that circuits achieve baseline performance, the time and resources required can be reduced by verifying device type, device characteristics, orientation, symmetry and other critical design parameters before runtime simulations are performed. By ensuring that a design is already trending towards accuracy before running simulations, a faster turnaround time is ensured. This minimizes both the number of simulation iterations and the time spent correcting post-simulation issues.

Automated verification solutions that can reliably and quickly verify that the design of RF ICs meets both technology and user-specific requirements are critical to ensuring that design organizations can deliver reliable products on time.

Design topology verification

Electronic design automation (EDA) verification tools specifically designed for topological circuit verification are now available to address the complex verification requirements of RF IC designs. We review the key verification strategies for RF ICs and use the Calibre PERC reliability platform from Mentor, a Siemens company, to demonstrate the automated verification capabilities available to RF IC designers.![Abb. 3: Ein volldifferenzierter Mischer [8] Abb. 3: Ein volldifferenzierter Mischer [8]](/images/stories/Abo-2020-11/thumbnails/thumb_plus-2020-11-0072.jpg) Fig. 3: A fully differentiated mixer [8]

Fig. 3: A fully differentiated mixer [8]

Control testing

Reliability testing tools can test a circuit design against the control criteria provided by the manufacturer as well as the specific requirements of the design organization. Designers can apply the rules provided by the manufacturers or create their own simple rules as needed to ensure that the correct type of circuit structures are used when required and that appropriate connections are made to those structures. For example, the Calibre PERC reliability platform can check multiple device characteristics (e.g. length, width, Vt type, etc.) and perform pattern matching to verify the characteristics and check the correct construction of certain circuit structures.

These rule checks are not limited to the common mainstream CMOS process. Manufacturers, designers and CAD engineers can define constraints and perform rule checks for any device process, such as heterojunction bipolar transistors or RF silicon insulators (RF SOIs), both of which are commonly used in RF designs.

RF/analog layout testing

Both the performance and reliability of RF designs are closely linked to layout implementation. Once the physical layout of an RF design is completed and the circuit implementation has been validated by a layout-to-schematic (LVS) comparison, many possible layout-dependent effects must be analyzed to avoid reliability and performance issues. Some of these effects can be captured in the simulation after the layout has been created, others only become visible once the design is on the silicon. Therefore, finding and eliminating them during design verification is critical to the market success of the chip [6].

RF/analog mask layout designers usually follow various precautions in designing the layout that minimize the effects of overlays, mismatches, noise, etc [7]. Common techniques used by these designers include symmetry of devices, matching current orientation, insertion of dummy devices, common center of gravity and spacing between devices, and electrical parameter matching [6].

Differential circuits are often used, for example, in RF designs for low-noise amplifiers, mixers, power amplifiers and charge pumps(Fig. 3). In a fully differential circuit, any lack of symmetry between the components impairs their ability to suppress input common mode noise, leads to the aforementioned input offsets and causes endless uniform order distortion [7]. Due to these effects, it is important to check the circuits for possible asymmetries in time.

To improve the effect of differential structure asymmetry, layout designers add dummy devices on both sides of the functional devices.

STI stress and WPE

Reliability is an important factor for market success in the development of RF circuits. Many RF products used in applications such as aerospace, satellite communications, military and defense operate in harsh environments and/or must operate under high stress for extended periods of time, with time-to-failure criteria for these products sometimes extending to several decades. Given these operating conditions and stringent requirements, designers face strict criteria for IC reliability when designing RF circuits. Fig. 4: (a) Fill in the excluded areas near sensitive nets, (b) fill created with the combined Calibre PERC/Calibre YieldEnhancer that prevents ingress into the critical nets

Fig. 4: (a) Fill in the excluded areas near sensitive nets, (b) fill created with the combined Calibre PERC/Calibre YieldEnhancer that prevents ingress into the critical nets

It is therefore important to consider the impact of layout-dependent effects such as shallow trench insulation (STI) loading.

trench isolation (STI) and well proximity effects (WPE), which can have serious consequences for the reliability and expected lifetime of RF ICs. Designers need to understand their causes and be aware of vulnerable layout structures when implementing RF circuits and apply appropriate layout techniques to mitigate the effects of these undesirable phenomena.

The effects of STI voltage can be reduced by adding dummy components and making the layout uniform and symmetrical [10].To minimize WPE, all components that are expected to behave and age similarly should be matched and have the same layout context, including the distance to the well edge. Verifying that these layout practices are followed through visual inspections or layout reviews is not ideal, as deviations easily occur. Due to the size and complexity of today's designs, it is also difficult to ensure sufficient coverage.

The Calibre PERC reliability platform provides consistent, automatic detection of the most subtle errors in a layout implementation, such as device asymmetry and mismatches, missing dummy devices or inaccuracy in a common-centroid layout. Within the Analog Constraint Check Flow Calibre PERC, designers define the checks they want to perform and select the components on which the checks are to be performed. The Calibre PERC reliability platform performs the checks on the specified components and displays the results in the Calibre RVE user interface, highlighting the deviations for easy viewing and quick correction.

HF/analog layout fill

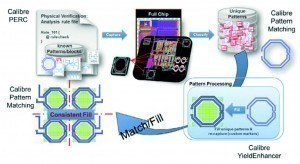

Filling is added to the design to reduce the thickness differences in copper connections resulting from the chemical mechanical planarization process step in manufacturing. However, floating filler affects the joint capacitance and changes the signal delay of the joints [2]. If the fill affects critical nets of the design, it can significantly reduce the performance of high-speed and RF designs. As frequency increases, the impact on resistance and inductance becomes significant. Above 10 GHz, the eddy current loss due to filling manifests itself as an increase in resistance [2] and can no longer be ignored. Fig. 5: Orientation-aware filling sequence ensures a symmetrical and uniform filling pattern around the inductors

Fig. 5: Orientation-aware filling sequence ensures a symmetrical and uniform filling pattern around the inductors

On-chip spiral inductors are often used in RF circuits, but their electrical performance can also be affected by filling [11]. The fill shape size and the distance of the fill to the signal wire of the inductor affect the quality factor (Q-factor) and the resonant frequency of the inductor.

Therefore, it is critical to optimize the fill process through consistent fill placement, sufficient distance of the fill shapes from the critical nets, and determination of the optimal fill shape size to maximize performance, minimize interconnect losses, achieve the desired Q-factor and resonant frequencies for inductors, and improve yield.

Design teams can optimize the process of filling by using automatic marking and filling techniques to consistently insert fill shapes into the design and prevent fill shapes from entering areas that need to be excluded from the filling process(Fig. 4). Designers can use the Calibre PERC reliability platform to automate the labeling of critical nets in their design prior to the fill generation step. The Calibre YieldEnhancer SmartFill process then automatically recognizes and satisfies any constraints imposed by the exclusion of marker layers in the layout. This combination of tools provides a huge advantage over traditional fill workflows where designers must either manually remove fill shapes around critical meshes or manually annotate those critical meshes before adding fill, both of which are slow, iterative and error-prone processes.

When Calibre Pattern Matching is added to this combination, an automatic, orientation-aware fill flow can be ensured, resulting in a consistent fill with no shifts in the fill pattern for elements such as inductors, gates, cells, etc. Designers capture unique configurations as patterns, fill each pattern as efficiently and effectively as possible, and then save the filled shape as a new pattern. Once the original pattern is found in the design, it is automatically filled according to the saved fill pattern to ensure consistency throughout the layout, as shown in Figure 5 [12].

Summary

RF IC designers are facing an increasing number of verification issues due to technology scaling, increasing integration with baseband and digital blocks and the need to support multiple protocols, combined with the demand for more compact devices with lower power consumption, higher bandwidth and throughput requirements. The use of manual techniques and traditional simulation-based approaches is suboptimal, leading to increased verification cycles and potentially inferior designs that can prove costly in today's fast-moving and demanding markets. By leveraging the advanced capabilities of EDA's reliability verification tools to automate a variety of complex verification processes at every stage of the design from schematic and layout verification and using a combination of tool capabilities to standardize and optimize post-layout fill, RF IC designers can dramatically reduce verification times while ensuring that their designs reliably meet their design specifications throughout the life of the products in which they are used.

About the person

Neel NatekarNeelNatekar is a Senior Product Engineer in Mentor's Design to Silicon department. He studied at the University of Mumbai and the University of Michigan. Prior to joining Mentor, Natekar worked as a design engineer at Qualcomm, focusing on power supply solutions for custom CPUs. He can be reached at

Neel NatekarNeelNatekar is a Senior Product Engineer in Mentor's Design to Silicon department. He studied at the University of Mumbai and the University of Michigan. Prior to joining Mentor, Natekar worked as a design engineer at Qualcomm, focusing on power supply solutions for custom CPUs. He can be reached at

References:

- Qualcomm Announces World's Most Power-Efficient NB2 IoT Chipset,' Qualcomm. April 16, 2020. https://www.qualcomm.com/news/releases/2020/04/16/qualcomm-announces-worlds-most-power-efficient-nb2-iot-chipset

- Tsuchiya, Akira; Onodera, Hidetoshi, 'Effect of Dummy fills on characteristics of passive devices in CMOS millimeter-wave circuits', 2009 IEEE 8th International Conference on ASIC, vol., p.296 - 299. https://ieeexplore.ieee.org/document/5351449/

- High-performance SiGe BiCMOS solutions,' GLOBALFOUNDRIES. https://www.globalfoundries.com/sites/default/files/sige_hp_pb_2020-0212web.pdf

- Lee, Thomas H. The Design of CMOS Radio-Frequency Integrated Circuits. 2nd ed. Cambridge: Cambridge University Press, 2003. doi:10.1017/CBO9780511817281

- White Paper 1: A Case for Lowering Component Level HBM ESD Specifications and Requirements,' Industry Council on ESD Target Levels, June 2018, Revision 4.0. https://www.esdindustrycouncil.org/ic/docs/industry%20council_esd_target_levels_whitepaper1_rev4.0_ june2018%20final.pdf

- Hossam Sarhan and Alexandre Arriordaz, 'Automated Constraint Checks Enhance Analog Designs Reliability', Mentor, a Siemens Business. Oct. 2018.

- B. Razavi, Design of Analog CMOS Integrated Circuits. New York: McGraw-Hill, 2001.

- N. Natekar, V. Vasudevan, A. Viswanath, 'A 5.2GHz RF Front-End,' University of Michigan, EECS 522 Final Project, 2011. https://www.eecs.umich.edu/courses/eecs522/w11/project/group8report.pdf

- S.K. Marella, S.S. Sapatnekar, 'The impact of shallow trench isolation effects on circuit performance,' 2013 IEEE/ ACM International Conference on Computer-Aided Design (ICCAD). San Jose, CA, 2013, pp. 289-294, doi: 10.1109/ICCAD.2013.6691134

- V. Moroz, et al, 'Stress-aware design methodology,' 7th International Symposium on Quality Electronic Design (ISQED'06), San Jose, CA, 2006. doi: 10.1109/ISQED.2006.124

- Akira Tsuchiya and Hidetoshi Onodera, 'Dummy fill insertion considering the effect on high-frequency characteristics of spiral inductors,' 2008 IEEE MTT-S International Microwave Symposium Digest, Atlanta, GA, USA, 2008, pp. 787-790. doi: 10.1109/MWSYM.2008.4632950

- Sherif Hany, 'Integrating Pattern Matching with DFM Properties to Enhance and Optimize Layouts', Mentor, a Siemens Business. Nov. 2017.