Hay indicios en todo el mundo de que la inteligencia artificial (IA) se está utilizando para elevar la industria electrónica a un nuevo nivel de calidad, ya sea en parte o en su totalidad. El proyecto IDEA de DARPA es un ejemplo llamativo del desarrollo de super IC, módulos semiconductores complejos como SoC y PCB.

Las partes 1 y 2 de este informe esbozan los revolucionarios objetivos de IDEA. La Parte 3 presenta otros proyectos europeos y estadounidenses para integrar la IA en el diseño y la producción de placas de circuitos impresos.

IDEA + POSH + otros 27 proyectos = ERI

Además de IDEA, hay que mencionar el proyecto asociado POSH (posh Open Source Hardware). Su objetivo es crear una plataforma basada en Linux y un ecosistema para diseñar y verificar bloques de hardware IP de código abierto para circuitos integrados de próxima generación. Ambos proyectos y otros 27 forman parte de ERI, la Iniciativa de Resurgimiento Electrónico lanzada por Darpa en 2017 [3]. Traducido literalmente, significa 'Iniciativa de Resurgimiento Electrónico'. Se puso en marcha no solo para revitalizar la industria nacional de chips en Estados Unidos, cada vez más deslocalizada a Asia desde hace décadas, sino también para elevarla a un nuevo nivel en general bajo el lema del futuro de la microelectrónica. Pero algo más parece haber sobresaltado al DoD: China está invirtiendo enormes sumas de dinero en la construcción y expansión de su industria de chips y ha declarado que quiere fabricar chips que añadan IA a todos los dispositivos. Se trata de un claro objetivo mundial para la electrónica del futuro.

En realidad, IDEA y POSH forman parte de un conjunto de cinco temas que se resumen en el ERI bajo el título "Mitigar los costes desorbitados del diseño electrónico". Los tres temas restantes son

- Estrategias comunes para la integración heterogénea y la reutilización de la propiedad intelectual (IP) (CHIPS)

- Aprendizaje automático en tiempo real (RTML)

- Generación automática inteligente y composición de modelos sustitutos (DITTO) (AIE)

Las vulnerabilidades en las cadenas de suministro de la industria electrónica mundial reveladas por la pandemia de coronavirus han dado a los esfuerzos de DARPA de 2017 una urgencia aún mayor, sobre todo porque el futuro de la Ley de Moore también es incierto y los sistemas de CI complejos mucho más grandes del futuro tendrán que realizarse utilizando la tecnología SoC o chiplet tanto por razones tecnológicas como económicas.

En [4] hay una justificación formulada de forma algo más precisa para el inicio de ERI (y por tanto de IDEA y POSH), que también se reproduce aquí como suplemento.

Los proyectos del ERI pretenden acelerar el desarrollo de SoC complejos y altamente individualizados. ERI está motivado por dos tendencias en el diseño de chips: En primer lugar, como la hoja de ruta de la Ley de Moore se está ralentizando, los diseñadores de SoC dependen menos de las CPU y más de una abundancia cada vez más necesaria de GPU, FPGA, chips neuronales y otros coprocesadores, lo que aumenta la complejidad tanto eléctrica como física de los sistemas de circuitos necesarios. En segundo lugar, los expertos ven una mayor variedad de aplicaciones para los componentes semiconductores mencionados, que van desde la IA basada en la nube hasta las redes definidas por software y el Internet de las cosas. Estas aplicaciones tan diversas suelen requerir combinaciones de procesadores muy diferentes, incluidos chips novedosos como los aceleradores para redes neuronales. Aquí también surge la necesidad de un amplio sistema modular de diferentes componentes de circuitos, que deben "ensamblarse" de la forma más eficiente posible en sistemas acabados de la máxima complejidad en el menor tiempo posible.

Continúa en [4]:

Darpa prevé que el mundo de la tecnología avance hacia una mayor variedad de SoCs con diferentes mezclas de bloques IP, incluyendo SoCs altamente personalizados para aplicaciones específicas. Sin embargo, con las herramientas de diseño de semiconductores actuales, este escenario se vería sumido en costes y retrasos crecientes. ERI planea acelerar las cosas.

El proyecto IDEA de EDA, que forma parte del ERI, se basa principalmente en el trabajo de David White en Cadence. El objetivo inmediato es desarrollar un generador de diseños que permita a los usuarios, incluso con poca experiencia en diseño electrónico, completar el diseño físico de hardware electrónico, como un ordenador de placa única, en 24 horas. Un objetivo más amplio y también un requisito fundamental para IDEA y, por tanto, también para ERI es permitir que el sistema EDA automatizado capte la experiencia de los diseñadores que lo utilizan para procesarla automáticamente, de modo que esté efectivamente disponible como una IA de apoyo al sistema en segundo plano para el trabajo de diseño.

Objetivo: automatización total del diseño

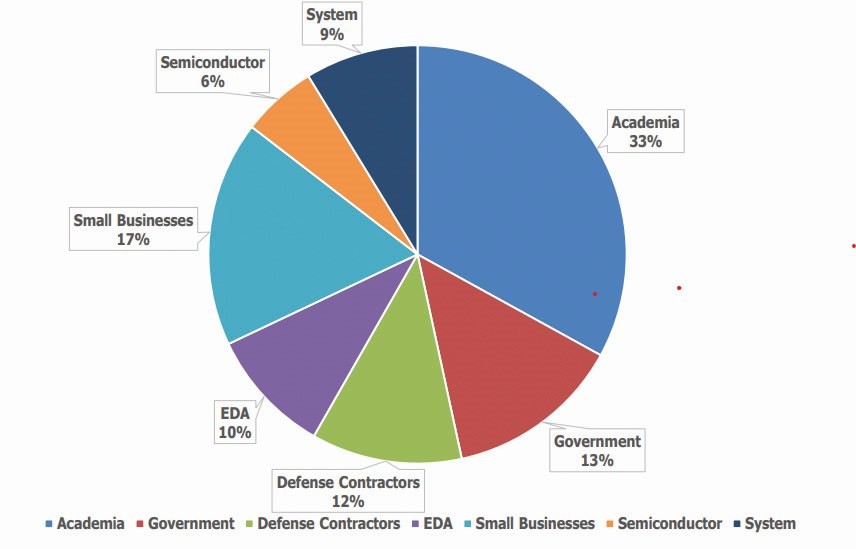

El primer Día del Proponente para IDEA y POSH tuvo lugar el 22 de septiembre de 2017 en Mountin View, California [5]. ERI se explica en detalle en el documento básico de 89 diapositivas del evento, que debe considerarse la base intelectual de la reunión y también del propio proyecto. El resumen estadístico de la Figura 3 demuestra el gran interés que suscitan ERI, IDEA y POSH. El horizonte temporal de la primera fase de realización se fijó audazmente en 2018-2023.

Fig. 3: Amplio interés por ERI en el Día del Proponente celebrado en septiembre de 2017

Fig. 3: Amplio interés por ERI en el Día del Proponente celebrado en septiembre de 2017

El debate de los participantes se basó en el objetivo de IDEA de crear un generador de diseños que sea capaz de finalizar los documentos de diseño para sistemas en chip, sistemas en paquetes y placas de circuitos impresos en 24 horas sin intervención humana ("sin humanos en el bucle"). A continuación se presenta una pequeña selección de diapositivas del documento básico, que pretende transmitir los aspectos fundamentales de IDEA. Las muchas otras diapositivas tratan detalles más específicos sobre ERI, así como IDEA y POSH, que excederían el objetivo y el alcance de este artículo.

Fig. 4: IDEA abarca las cuatro fases de creación de la electrónica: chips, módulos de chips, placas de circuitos impresos o conjuntos acabados, dispositivos finales en la carcasa

Fig. 4: IDEA abarca las cuatro fases de creación de la electrónica: chips, módulos de chips, placas de circuitos impresos o conjuntos acabados, dispositivos finales en la carcasa

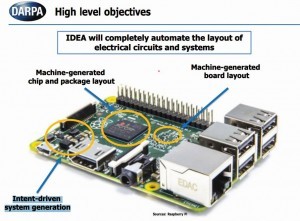

La figura 4 esboza el alcance de lo que se espera de IDEA. La pregunta es: ¿puede sustituirse el trabajo manual por máquinas? Según la figura 5, IDEA debería automatizar completamente el trazado de circuitos y sistemas eléctricos:

- Generación de sistemas basada en la intención

- Diseño de chips y paquetes generado por máquina

- Diseño de placas generado por máquina

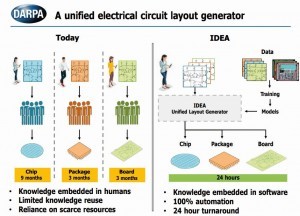

El objetivo es transferir los conocimientos de los desarrolladores de sistemas, circuitos, chips y placas al generador de trazado unificado IDEA (generador de trazado estandarizado) mediante la formación a través de modelos(Fig. 6). La base del sistema es, por tanto

- Conocimientos integrados en el software

- Automatización al 100

- Especificaciones de tiempo de procesamiento de 24 horas

Los siguientes factores(Fig. 6) actúan como freno a la necesaria aceleración significativa en la creación de nuevos sistemas electrónicos de alta complejidad:

- Conocimiento integrado en las personas

- Reutilización limitada de los conocimientos

- Dependencia de recursos escasos

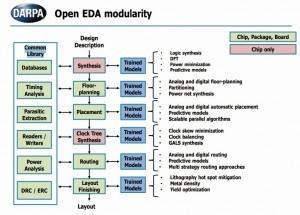

El objetivo final es la modularidad abierta de EDA y un proceso de diseño estandarizado, como se muestra en la Figura 7. Los pasos del proceso ecológico son básicamente los mismos para chips, módulos de chips y placas de circuitos impresos. La base es una biblioteca común estandarizada.

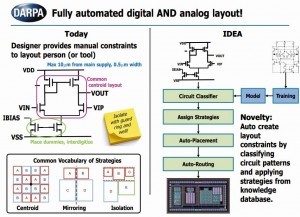

El objetivo es conseguir una maquetación digital y analógica totalmente automatizada. De acuerdo con el documento básico, hoy en día el desarrollador todavía realiza especificaciones de diseño (restricciones) manualmente al maquetador o al sistema CAD. En el futuro, las restricciones de diseño se crearán automáticamente clasificando el diagrama del circuito (patrones del circuito) en función de determinadas especificaciones estratégicas de la base de datos de conocimientos(Fig. 8).

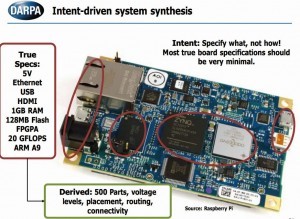

IDEA se basa en la síntesis de sistemas basada en la intención(Fig. 9). El objetivo es especificar qué debe hacerse y no cómo. Esto último es tarea del sistema. Las especificaciones de la placa deben ser mínimas. Ejemplo de especificaciones: 5 V, Ethernet, USB, HDMI, 1 GB de RAM, 128 MB de Flash, FPGPA, 20 GFLOPS, ARM A9.

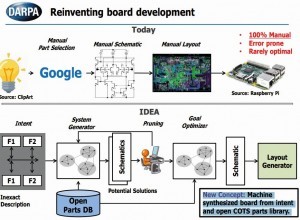

La figura 10 demuestra una vez más las diferencias entre la forma de trabajar anterior (100% manual, propensa a errores, rara vez óptima) y el nuevo enfoque (placa sintetizada por máquina basada en las especificaciones de intención y en la biblioteca de piezas COTS). La solución es reinventar el desarrollo de placas.

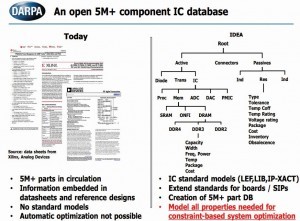

La figura 11 ilustra la situación actual de la base de componentes:

- Más de 5 millones de componentes en circulación

- La información está incorporada en hojas de datos y diseños de referencia

- No hay modelos estándar

- No es posible la optimización automática

Esto debe contrastarse con un enfoque diferente en IDEA:

- Modelos estándar IC (LEF, LIB, IP-XACT)

- Extensión de estándares para placas/SIPs

- Creación de una amplia base de datos de piezas 5M+

- Modelización de todas las propiedades necesarias para la optimización del sistema basada en restricciones

Los detalles del proyecto se describen en muchas otras diapositivas. El objetivo principal de la ERI es lograr un desarrollo más rápido, eficaz y seguro de nuevos productos electrónicos, lo que en sí mismo supondría un gran paso adelante. Ahora imaginemos que los datos de producción disponibles digitalmente se transfieren inmediatamente a la producción de una red de fábricas inteligentes que utilizan redes de datos 5G o 6G como parte de la Industria 4.0. El efecto global para la industria electrónica y, por tanto, también para la economía sería inconmensurablemente mayor. Cabe suponer que Darpa ya ha considerado esta construcción de puentes conceptuales o estratégicos. La cuestión es hasta qué punto las grandes y, en particular, las pequeñas empresas fabricantes están dispuestas o son capaces de aceptar estos nuevos procedimientos y formas de organización.

Proceso del proyecto hasta la fecha

Las empresas e instituciones pudieron presentar solicitudes para participar en IDEA con las correspondientes ofertas de servicios a Darpa a finales de enero de 2018. Es interesante señalar que Serge Leef ha asumido la gestión del proyecto para IDEA en la institución DoD. Leef es considerado un experimentado experto en EDA que se trasladó a Darpa tras la adquisición de Mentor Graphics por Siemens. ¿Por qué cree?

En junio de 2018, se lanzó OpenROAD (Fundamentos y realización de diseño abierto y accesible) como parte de ERI, otro proyecto destinado a ayudar a implementar IDEA con éxito.

La reunión general Darpa-ERI se celebró en San Francisco en julio de 2018. La participación de Cadence en IDEA también fue confirmada por Darpa. IBM, Intel, Nvidia, Qualcomm y otras empresas ya lo habían hecho.

Para cumplir la carta del programa durante los cuatro años de vigencia de su contrato, Cadence ha puesto en marcha el programa de investigación y desarrollo MAGESTIC (Machine Learning-driven Automatic Generation of Electronic Systems through Intelligent Collaboration). El objetivo de este programa es aumentar el rendimiento del diseño de sistemas introduciendo una mayor autonomía en el proceso de diseño y desarrollando productos verdaderamente orientados al diseño. El equipo dirigido por Cadence incluye a la Universidad Carnegie Mellon y a NVIDIA, dos de los líderes en aprendizaje automático más reconocidos del mundo [4].

Durante la reunión general de ERI en 2018, Darpa también anunció la primera financiación para los proyectos ERI. En una primera ronda, se anunciaron 1500 millones de dólares iniciales para los próximos cinco años. Cadence fue la primera en recibir una subvención de 24,1 millones de dólares para IDEA.

La Cumbre Darpa-ERI 2019 se celebró en Detroit a mediados de julio. Una sección de la sesión sobre IDEA se centró en el subproyecto 'MAGICAL: Machine Generated Analog IC Layout'. Un equipo de investigación de la Universidad de Texas (Austin) presentó los avances de su trabajo para su debate. Cabe destacar que el grupo de investigación MAGICAL, compuesto por 8 miembros, estaba formado exclusivamente por personas de origen chino, desde los profesores hasta los estudiantes de doctorado y ayudantes de investigación. En otra sección de la sesión, se debatió el tema del "Diseño Generativo de la Electrónica con Intención de Usuario", bajo la dirección de Northroop Grumman.

A pesar del coronavirus, la Cumbre Darpa-ERI 2020 se organizó para agosto en Seattle. Esto subraya la urgencia del proyecto desde la perspectiva gubernamental. La Cumbre Darpa-ERI 2021 se ha anunciado como un evento virtual para los días 19/21 de octubre [3]. Todas las presentaciones de pósters y demás material de las tres cumbres celebradas hasta la fecha pueden descargarse gratuitamente de la página web indicada en [3].

Mirando al futuro próximo

Si se combinan mentalmente los planes masivos en curso del gobierno estadounidense de construir numerosas fábricas nuevas de chips en EE.UU. para la gama inferior de nanómetros, de 28 a 5 nm, con el enorme proyecto ERI, cabe suponer que en los próximos años podría producirse en EE.UU. una especie de "revolución electrónica", siempre que ERI pueda llevarse realmente a la práctica de forma paralela. Aunque IDEA es ante todo un proyecto militar, cabe suponer que los resultados positivos también se aprovecharán para el ámbito civil, como es habitual en EE UU. Si a esto se añade la iniciativa CFX (Connected Factory Initiative) del IPC, en Estados Unidos se están sentando cada vez más las bases de una nueva industria electrónica de calidad. La norma IPC-2591 permite la comunicación IoT "plug-and-play" en todo el entorno de fabricación, en el que todos los dispositivos, procesos de fabricación y estaciones de transacción pueden comunicarse sin necesidad de software especial. Actualmente es válida la versión 1.3 de febrero de 2021. Este estándar también se está desarrollando sistemáticamente para la Industria 4.0 y la fábrica inteligente. La lista de empresas que admiten CFX crece constantemente [6].

En la siguiente parte 3 de este artículo se presentan otros proyectos europeos y estadounidenses en los que se está intentando anclar la IA en el diseño y la producción de placas de circuitos impresos.

Referencias

[1] https://de.wikipedia.org/wiki/K%C3%BCnstliche_Intelligenz#Begriffsherkunft_und_Definitionsversuche

[2] www.darpa.mil/program/intelligent-design-of-electronic-assets

[3] https://eri-summit.darpa.mil/

[4] www.linux.com/topic/embedded-iot/darpa-drops-35-million-posh-open-source-hardware-project/

[5] www.darpa.mil/attachments/eri_design_proposers_day.pdf

[6] www.ipc.org/cfx-supporters