The global focus on digitalization and the 'green deal' present the electronics sector with major challenges such as sustainable production, the use of innovative materials and the avoidance of bottleneck raw materials. As 'time to market' is a key success factor, shorter development times and parallel quality assurance measures for R&D, production and market performance are necessary. To this end, TU Wien has developed a highly efficient method for accelerated lifetime assessment of solder joints in a variety of multilayer electronic components. With this high-frequency, cyclic bending test system, the test times of conventional test procedures can be reduced from several months to just a few hours.

With the global focus on digitalization and the green deal, the electronics sector is facing major challenges, such as sustainable production, the use of innovative materials and the avoidance of bottleneck resources. With 'time to market' being a key success factor, shorter development times and concurrent quality assurance measures of R&D, production and market performance are necessary. To this end, a highly efficient method for accelerated lifetime evaluation of solder joints in a variety of multilayer electronic components has been developed at TU Wien. With this high-frequency cyclic bending test-system, the testing time can be reduced from several months required by conventional methods to just a few hours.

Introduction

The continuous development in the semiconductor industry has led to considerable technological progress in recent decades. Due to numerous emerging technologies, the industry expects strong growth and further innovations in IC technology, which in turn require increased complexity. Particularly in industries such as e-mobility and renewable energy, the increasing demand for high-performance semiconductor devices has led to the development of modules with higher power density, operating frequency and integration [1, 2]. The transition temperature of conventional leaded and lead-free solders and electrically conductive adhesives (ECAs) of around 150 °C is increasingly being exceeded [3-6]. Stresses already occur in multilayer electronic components during production and later operation, which are mainly due to the different coefficients of thermal expansion of the materials used. In the long term, the thermomechanical cyclic stresses induced as a result of temperature fluctuations and uneven heat distribution in the components lead to the formation and propagation of cracks and ultimately to fatigue and failure [7-10].

It is well known that large-area solder joints, which together with bonding wires are the most important electrical, mechanical and thermal connections between chips, substrate and base plate, represent the greatest weak point. In addition, the high homologous temperatures in the solder joints, which favor the diffusion processes, lead to major microstructural changes and creep effects, which contribute to a greater susceptibility of these connections. The increased emergence of wide bandgap semiconductor (WBG) technologies such as silicon carbide (SiC) and gallium nitride (GaN) with junction temperatures of 175 °C and above in many applications further exacerbates this problem and requires new interconnection technologies, materials and assembly methods [3, 4].

Alternative joining technologies

Lead-free alternatives to replace solders with high lead content (i.e. with more than 85% Pb by weight) are still at an early stage of development. New joining technologies such as Ag-sintering, low temperature transient liquid phase sintering (such as Sn-Cu, Au-Sn, Au-In, Ag-In, Ag-Sn, Cu-In and Ni-Sn) or high melting point solder alloy systems such as AuSn, AuGe, ZnAl, ZnSn, BiAg and SnSb are potential lead-free and RoHS compliant substitutes for PbSn and other lead-containing solders for high temperature applications [3, 4, 6]. Most alternatives are significantly more expensive in terms of material cost than Pb5Sn2.5Ag, one of the most common solders with high lead content. Some of these alternative technologies have not yet established themselves as suitable replacements for high-temperature Pb solders due to the limited data available on their long-term reliability. Due to the inhomogeneous microstructure and viscoplastic behavior of the solders at typical operating temperatures, identifying the failure mechanisms that occur and predicting product lifetime is not an easy task.

Most alternatives are significantly more expensive in terms of material costs than Pb5Sn2.5Ag, one of the most common solders with a high lead content

Because the potential lead-free high-temperature materials cannot be used as drop-in solutions without restrictions in terms of the three main criteria of performance, processing and cost, the exemption for the use of lead-containing solders with a high melting temperature has been extended again until at least 2024 [5]. In order to maintain and further improve current technologies, there is an urgent need to find and develop solder alloys that can completely replace high-temperature leaded solders. Extensive studies have therefore been initiated to develop alternative assembly and joining technologies for high-temperature applications. In order to drive this development process forward and keep pace with market trends, the development and application of highly accelerated and practical methods for reliability assessment is required, especially for high-performance components.

Reliability tests

In industrial practice, the reliability of electronic components is assessed using thermal cycling tests. Static shear and pull tests are used to determine the quality and adhesive strength of the chip/substrate connection. The temperature cycling tests are intended to simulate the thermomechanical operating conditions in an accelerated form, whereby a distinction is made between active power cycling (PC) tests in relation to the junction temperature (ΔTvj) and passive thermal cycling (TC) tests in relation to the solder joint and housing temperature (ΔTC). In the PC test, the temperature of the chip connections is raised and lowered in relatively short intervals of a few seconds. This mainly stresses the bonding wires on the chips and the solder joints under the chips. Typical accelerated PC tests for classic modules are performed with a temperature swing (ΔT) of around 90 K or more and heating/cooling cycles of around 30-60 seconds, whereby the temperature difference at the junction and the cycle duration can vary depending on the application.

At higher junction temperatures, failure of the wire bonds may occur, while lower temperature differences lead to degradation and failure of the solder layer under the silicon chip [8]. The reliability diagrams represent the lifetime of the entire module as ΔT versus the cycles to failure without distinguishing between the different failure modes. Due to the very long test times of up to several months, the fatigue life for high cycles (> 1e6 cycles) is usually determined by interpolating the fatigue data. In thermal cycling (TC), the housing temperature is increased and decreased in relatively long intervals within minutes. The solder joints between the ceramic substrate and the module base plate are particularly stressed. Numerous studies have shown that different test conditions can strongly influence the service life and the predominant failure modes of the devices [5, 6].

To ensure the required lifetimes of these connections and to meet the growing demand for virtualized qualification methods, it is essential to obtain detailed information about their behavior under cyclic loads. The creation of reliable service life prediction models therefore requires not only reliable experimental data, but also a sound knowledge and understanding of the time- and temperature-dependent deformation behavior of the solders and the stress-strain conditions in the joints. Knowledge of crack formation, propagation and degradation is crucial for understanding the fatigue mechanisms of materials. Therefore, the static and cyclic properties of the solder material and the solder joints are investigated in numerous studies. In many cases, isothermal mechanical fatigue tests are performed at low and medium test frequencies to obtain data for constitutive models, validate finite element simulations and create lifetime prediction models.

Knowledge of crack formation, propagation and degradation is crucial for understanding the fatigue mechanisms of materials

Ex-situ techniques such as ultrasonic microscopy (SAM), computed tomography (CT), thermal resistance measurements [11] or pulse-phase thermography [12] are available for analyzing delamination and detecting failures of electronic components. Nevertheless, the development of more effective and reliable methods for non-destructive in-situ detection and monitoring of delamination and cracking before final failure is urgently needed. This can provide necessary information for accurate lifetime prediction models that accurately reflect real-world conditions. Especially since it is important to be able to recognize the different failure modes caused by the clash of different technologies and material combinations at an early stage of a product's development.

To this end, our research group at TU Wien has developed a highly efficient method for the accelerated evaluation of electronic components [13-17]. With the help of a special high-frequency cyclic bending test system, the service life of solder joints in a large number of multilayer electronic structures could be determined in a very short time. As a result, the testing times of conventional test methods can be reduced from several months to just a few hours. Equipped with a novel, non-destructive in-situ method based on laser Doppler vibrometry (LDV), this test system can also be used to detect cracks and delamination in semiconductor structures before the end-of-life.

In the following, the applicability of this accelerated mechanical fatigue testing system for the reliability assessment of electronic interconnects is presented and discussed using examples of specially developed model test structures and samples from production.

Structure of the accelerated mechanical fatigue test systems

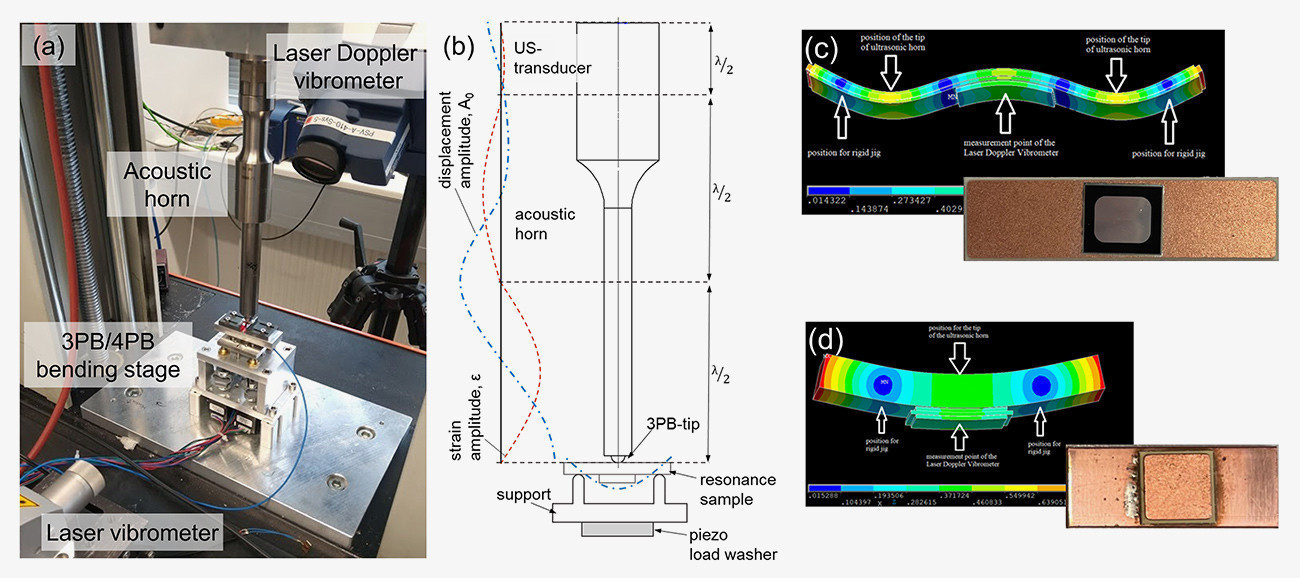

The accelerated fatigue tests were performed using an ultrasonic resonance testing system consisting of a power supply, a piezoelectric transducer, an acoustic horn with tip and the specimen as shown in Figure 1a. The excitation of a longitudinal vibration at 20kHz takes place in the piezoelectric transducer and is amplified by the horn or suitable coupling pieces. At the point of maximum deflection, the system is coupled to the sample by means of the three/four-point bending (3PB)/4PB tip of the horn(Fig. 1 b). This must be geometrically dimensioned in such a way that a standing transverse oscillating motion is formed at 20 kHz. Examples of sample geometries determined with the aid of FE simulations for large-area solder joints in multilayer semiconductor structures are shown in Fig. 1 c, d. The static and cyclic loads can be measured using a piezoelectric force transducer mounted under the supports of the 3PB/4PB device. A low test-dependent static preload is required to ensure constant contact of the tip with the sample during vibration excitation. The vibration modes and the deflection amplitude of the sample during excitation were determined using a laser Doppler vibrometer.

Fig. 1: (a) Setup of the ultrasonic fatigue system for the cyclic 3PB/4PB bending load test with (b) schematic representation of the test principle; (c, d) FEM simulations and specimen view of typical 4PB and 3PB specimens for large-area chip-plot and ceramic-substrate plumb joints, respectively. The arrows show the positions of the stress and the measuring points in the 3- and 4-point bending tests

Fig. 1: (a) Setup of the ultrasonic fatigue system for the cyclic 3PB/4PB bending load test with (b) schematic representation of the test principle; (c, d) FEM simulations and specimen view of typical 4PB and 3PB specimens for large-area chip-plot and ceramic-substrate plumb joints, respectively. The arrows show the positions of the stress and the measuring points in the 3- and 4-point bending tests

In-situ delamination measurement

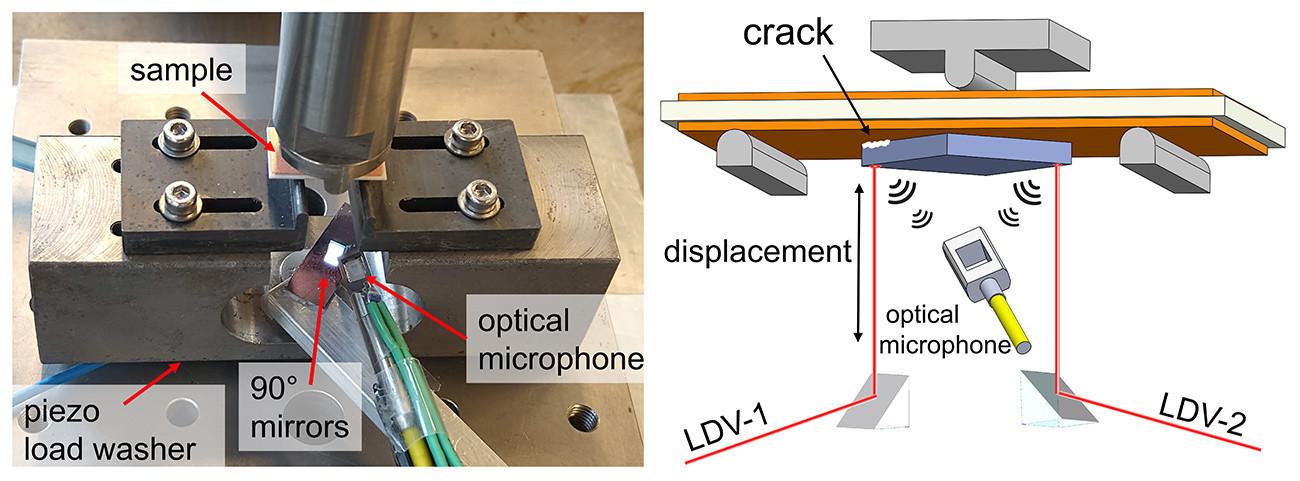

The setup of the non-destructive in-situ vibrometer measurement during the cyclic bending tests is shown in Figure 2 . The setup consists of a laser Doppler vibrometer to determine the deflection amplitude of the sample vibrating in a transverse resonance mode at 20 kHz. Two separate measuring points are directed to the corners of the chip by 90° deflection mirrors. As soon as cracks begin to grow at the corners of the chip due to the excess stress, the deflection amplitude of the vibrometer signal at the corresponding corner increases compared to the deflection or fundamental vibration of the substrate. This increase increases steadily as the crack propagates until the test is stopped or the chip is completely delaminated. In-situ delamination detection was applied to a selection of the sample systems described above to determine the time of crack initiation and the delamination rate. The fatigue tests can be performed under isothermal conditions up to about 200 °C to simulate the damage to the solder joints under the high stresses that power modules can be subjected to in operation. A hot air blower is used to heat the samples during the test. The samples can either be tested until 'end-of-life', i.e. until complete delamination, or with the in-situ method up to a certain degree of damage.

Fig. 2: (a) Setup and (b) schematic principle of non-destructive in-situ delamination measurement using laser Doppler vibrometry and acoustic emission measurement during cyclic ultrasonic bending load tests

Fig. 2: (a) Setup and (b) schematic principle of non-destructive in-situ delamination measurement using laser Doppler vibrometry and acoustic emission measurement during cyclic ultrasonic bending load tests

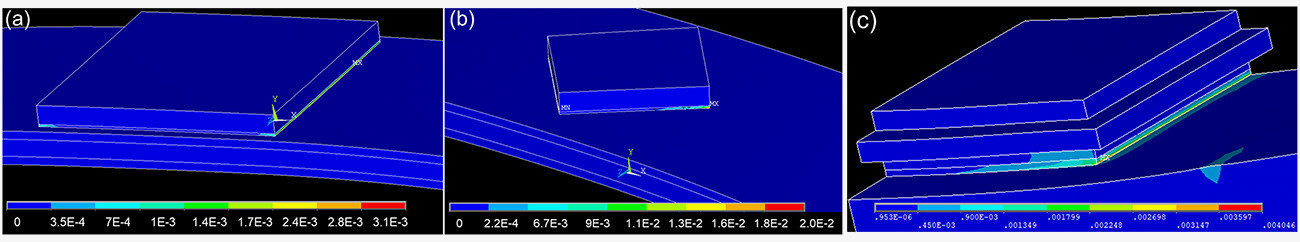

Fig. 3: Diagram of the accumulated plastic strain in the solder layers of the different sample configurations. The critical points of maximum plastic strain, where the first cracks are to be expected, are localized at the edges of the specimens

Fig. 3: Diagram of the accumulated plastic strain in the solder layers of the different sample configurations. The critical points of maximum plastic strain, where the first cracks are to be expected, are localized at the edges of the specimens

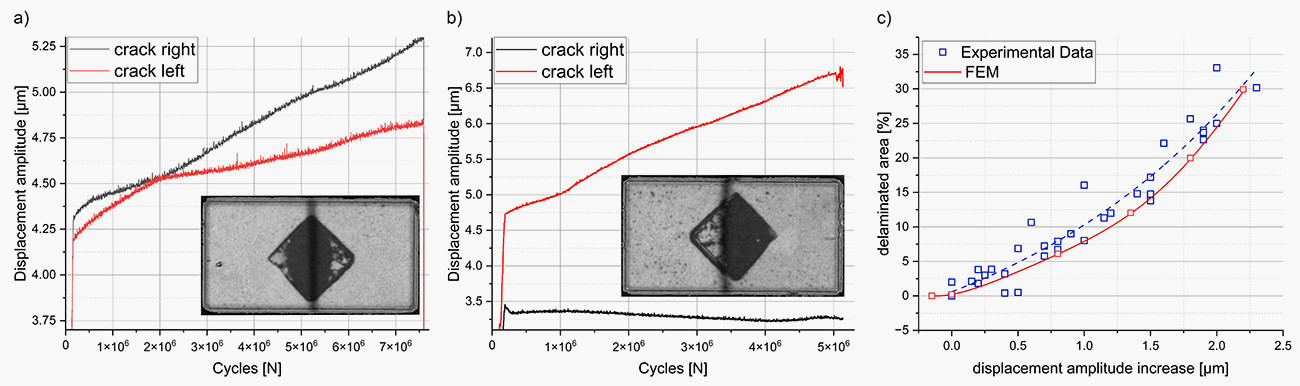

The results of the in-situ delamination measurements for a series of chip/solder/DCB (Direct Copper Bonded) samples in 3PB arrangement on 45° rotated chip geometry, which serve to additionally increase the stress concentration, are explained below. In Figure 4 a, b, two exemplary curves of the deflection amplitude versus the number of cycles are compared with the SAM (Scanning Acoustic Microscopy) images of the delaminated surfaces. In the first case, the increase in deflection amplitude on both sides is accompanied by symmetrical crack growth at both corners of the Si chip. The second example shows a one-sided delamination in the SAM image with a strong increase in the deflection amplitude of the corresponding vibrometer measurements, while the amplitude at the other corner remains constant during the test duration. Asymmetric delamination behavior can be attributed to process-related differences in the quality of the solder joints (pores, thickness, etc.) or small deviations from the central positioning of the Si chip.

Figure 4 c shows the experimentally determined dependence of the delaminated solder area on the measured change in the deflection amplitude of the chip for a defined model structure. An area of 50 % corresponds to complete delamination of the respective chip half. The correlation between the vibrometer signal and the delaminated area can be clearly identified. The calibration curve thus determined was confirmed by measuring numerous samples of different solders independently of the load cycles. The curve calculated alternatively from the vibration behavior of the sample geometry at different degrees of delamination using FEM agrees well with the experimental data. These curves can serve as a basis for the in-situ determination of crack initiation and the delamination rate for the respective test structure.

Fig. 4: Examples of (a) double-sided and (b) single-sided crack growth, SAM images (light areas show delamination) and the corresponding diagrams; (c) relationship between the delaminated area and the relative increase in deflection, calibration curves from experimentally determined data (blue) and from the FEM simulation (red).

Fig. 4: Examples of (a) double-sided and (b) single-sided crack growth, SAM images (light areas show delamination) and the corresponding diagrams; (c) relationship between the delaminated area and the relative increase in deflection, calibration curves from experimentally determined data (blue) and from the FEM simulation (red).

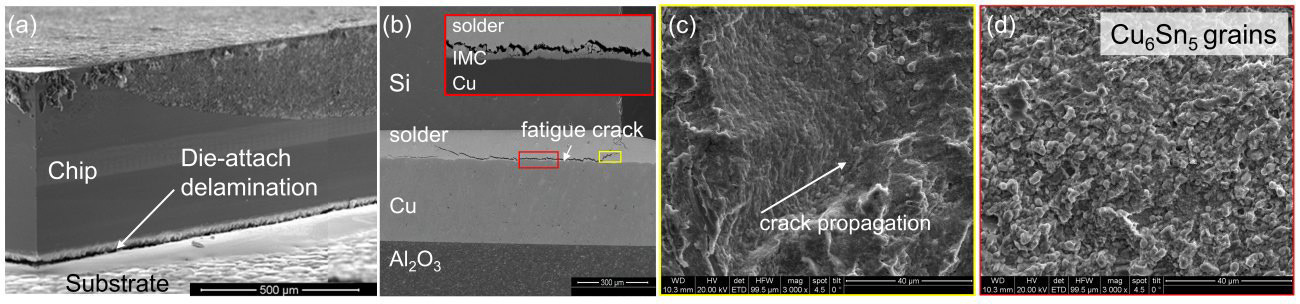

In order to evaluate the delamination behavior, metallographic examinations of the fatigued samples and fracture surface analysis using SEM are used. The visible crack length along the edge of the Si chip, starting at the corner, can be seen in SEM images(Fig. 5 a, b). The determination of the delamination length along the chip side edge can also be used to estimate the delaminated area with good agreement.

Our results, show a typical crack path originating near the corner of the chip/solder joint interface and propagating towards the DBC substrate (Fig. 5 a). The crack then mainly follows the interface between the solder joint and the Cu6Sn5 intermetallic phase (IMC)(Fig. 5 b).

The comparison of the delaminated area between the SAM measurements and the evaluation of the alternatively performed 'die-shear' tests also provided very similar results. Examples of the fatigue fracture surfaces of the solder joints after the shear tests, which are shown in Fig. 5 c, d, also show a fatigue crack path that first runs within the solder and then close to the IMC layer on the back of the chip.

Fig. 5: Typical fatigue cracking and delamination in chip plot (a) Fatigue cracking in the solder at the corner of the chip and along the interface. (b) Cross-section of the fatigue crack in the solder and along the interface to the intermetallic phase (IMC) with exemplary fracture patterns showing the fracture mode (c) at the IMC and (d) in the solder

Fig. 5: Typical fatigue cracking and delamination in chip plot (a) Fatigue cracking in the solder at the corner of the chip and along the interface. (b) Cross-section of the fatigue crack in the solder and along the interface to the intermetallic phase (IMC) with exemplary fracture patterns showing the fracture mode (c) at the IMC and (d) in the solder

Application examples

Reliability of high-temperature lead solder alloys

Although the current exemption allows the use of lead in refractory solders such as electronic devices for military and aerospace applications, the deadline for compliance with the RoHS Directive is fast approaching [5]. A current application example is the use of lead-rich Pb-Sn-Ag solders for die attach applications in high performance semiconductor devices with high reliability requirements [8, 10]. Typical binary and ternary Pb-rich solders with melting points in the range of 300 °C and above, containing 5 to 15 wt% tin and up to 5 wt% silver, exhibit a stable microstructure, slow growth of IMC interface layers and high thermomechanical fatigue resistance, and are also relatively inexpensive. The composition of the solders and the type of metallization of the chip backside play an important role, as can be seen from the following example.

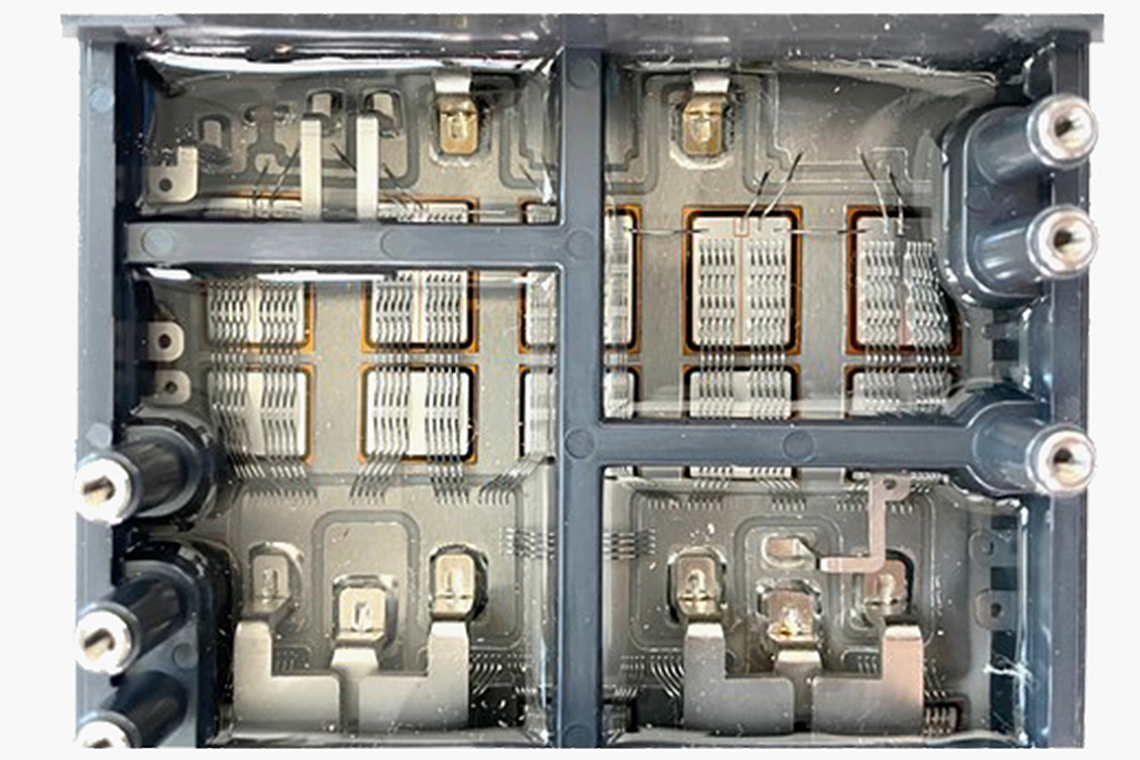

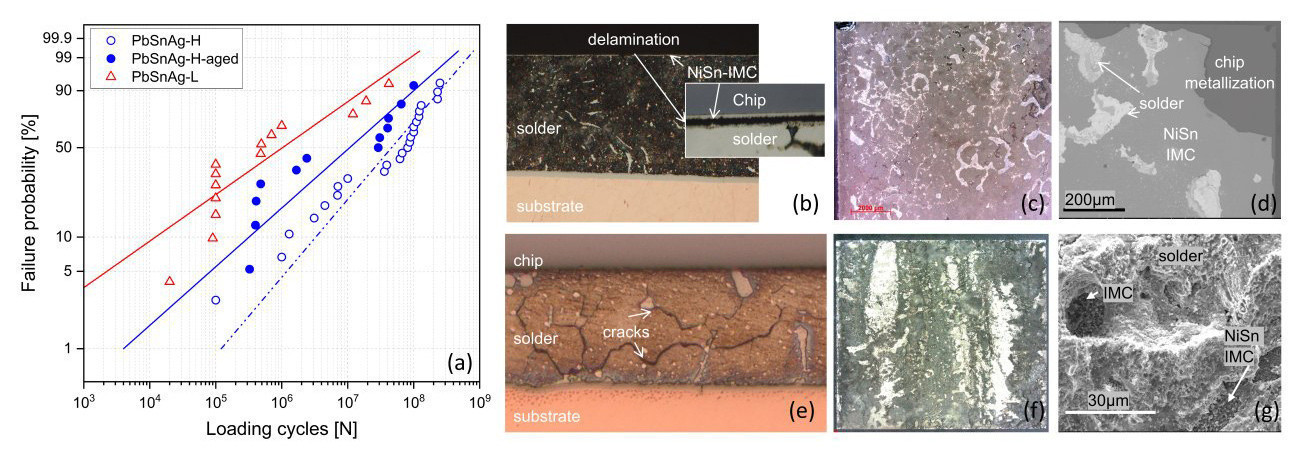

In the following studies, the accelerated cyclic bending test system presented here was used for the evaluation of high-temperature PbSnAg solders [13, 14]. To reproduce the typical semiconductor structures, commercial IGBT chips with Ni metallization were soldered onto the Ni-coated AMB substrates. Two different Pb solders with lower Sn content (PbSnAg-L) and higher Sn content (PbSnAg-H) were used as die attach. The geometries of the semiconductor model structures obtained correspond to the resonance conditions required for the cyclic bending system.

The fracture probability curves, determined at a constant bending load amplitude of approx. 5µm and 80 °C, are shown in Figure 6a. The results of the accelerated tests show that PbSnAg-L solder joints are less reliable than PbSnAg-H solder joints. Ageing the samples with a higher Sn content (PbSnAg-HA) at 250 °C for 250 hours leads to a reduction in service life. Failure analysis of the samples revealed that the dominant failure mode of the lower Sn solder joints was the complete or partial delamination of the chip from the substrate mainly at the interface between the Ni3Sn2 IMC and the Ni metallization(Fig. 6 b, c and d). This failure mode is similar to the 'spalling' failure commonly observed in flip-chip technology with PbSn and lead-free solders. The spalling of the intermetallic compounds from the UBM (under bump metallization) layers was explained by rapid reactions between the molten solders and thin UBM layers and the degradation of the wettable layer [18]. It is assumed that massive spalling occurs in solder joints where the reaction product is sensitive to the composition of the solder and the concentration of the reactive component in the solder is limited. In this case, the reduction of the Sn concentration at the Ni/solder interface and the continuous penetration of Pb into the Ni metallization leads to a weakening of the joint at the interface between the IMC and the metallization layer and to premature failure. A higher Sn content in the alloy contributes to the reliability of the solder joints by preventing severe delamination and interface failure even after long-term thermal exposure. The metallographic cross-section in Figure 6 e shows the formation of fatigue cracks within the solder of a PbSnAg-H through-hole sample. The fracture surfaces of the failed specimens show a failure mode caused by fatigue of the solder(Fig. 6 b, c, d with 6 e, f, g).

Fig. 6: a) Fracture probability curves of the PbSnAg die attach solder joints after high-frequency cyclic bending stress for PbSnAg solders with low and high Sn content; cross-sections of the joints (b, e) and c, d and f, g) Fracture surfaces of the chip backside after fatigue stress (top row for PbSnAg-L and bottom row for PbSnAg-H)

Fig. 6: a) Fracture probability curves of the PbSnAg die attach solder joints after high-frequency cyclic bending stress for PbSnAg solders with low and high Sn content; cross-sections of the joints (b, e) and c, d and f, g) Fracture surfaces of the chip backside after fatigue stress (top row for PbSnAg-L and bottom row for PbSnAg-H)

Comparison of lead-free and lead-containing solders

In general, high heat resistance to static and cyclic loads is an essential prerequisite for die-attach materials. Solders containing antimony are currently regarded as a potential replacement for lead solders for applications in the high-temperature range. Sn-5Sb (Sn-5wt%Sb) with a liquidus temperature of 245 °C, for example, exhibits only limited IMC growth, resulting in attractive creep and mechanical properties such as excellent thermal fatigue behavior and relatively high fracture strength. Further improvement of the mechanical properties of SnSb alloys can be achieved by adding additional elements such as Ag, Au, Ni. According to studies, the addition of Ag leads to a further increase in the tensile strength of the SnSb solder due to the formation of Ag3Sn and the refinement of the β-Sn grains.

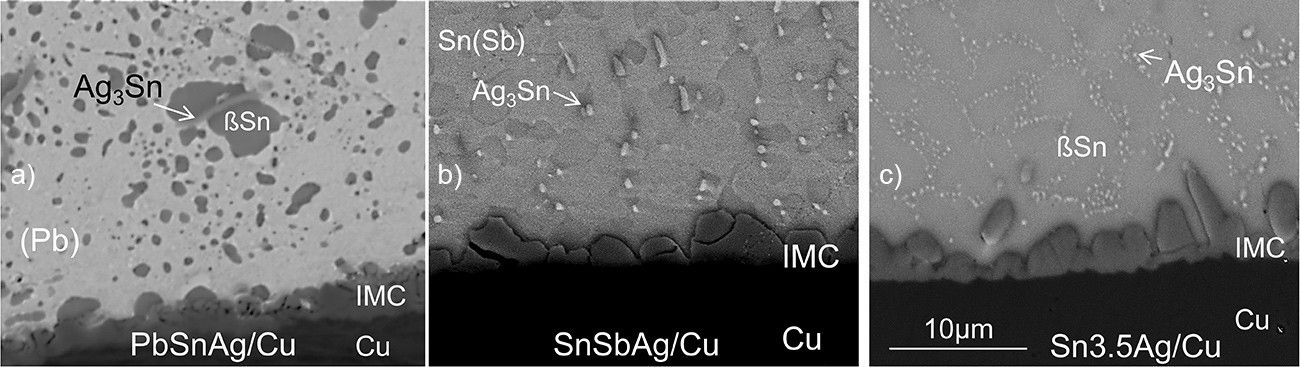

In the following study, the mechanical fatigue properties of SnSbAg solder joints are compared with those of the commonly used PbSnAg and Ag3.5Sn solders at temperatures up to 175 °C. The model test structures of chip/solder/DCB and DCB/solder/Cu were produced in three- and four-point bending configurations(Fig. 1 c, d). Representative microstructures of the solder joints are shown in Figure 7 .

Fig. 7: Typical microstructures of (a) high-lead PbSnAg and (b) lead-free SnSbAg and (c) Sn3.5Ag-Cu solder joints

Fig. 7: Typical microstructures of (a) high-lead PbSnAg and (b) lead-free SnSbAg and (c) Sn3.5Ag-Cu solder joints

Figure 8 a shows a comparison between the fatigue behavior of the Pb-rich solder joints and that of the SnSbAg solder joints at 80 °C in the form of load cycles to failure as a function of the deflection amplitudes in the cyclic bending test. To enable a comparison between the fatigue life curves of the Pb-rich and SnSbAg solder in terms of strain and stress values, the experimental fatigue life curves were plotted in Figure 8 a as a function of the total strain(8 b) and the average v. Mises stress(8 c) [15]. For this purpose, transient FEM simulations of the cyclic bending tests with elasto-plastic material models were carried out for the solders, taking into account the strain rate and temperature dependence of the yield stress. It should be noted that in this case the specified stress and strain values were calculated for the initiation of the cracks and vary with increasing crack length. The graphs show a remarkably higher fatigue strength for the SnSbAg solder material at high cycles, which is due to the high stiffness and creep resistance of the Sb-containing solder alloy [4, 15, 19].

![Abb. 8: Ermüdungskurven von PbSnAg- und SnSbAg-Lötstellen bei 80 °C, dargestellt als Gesamtlebensdauer in Abhängigkeit von der Auslenkungsamplitude (a) und der gesamten mechanischen Dehnung (b) und der volumengemittelten Spannung (c), die zur Rissentstehung (N0) führt [15]. Abb. 8: Ermüdungskurven von PbSnAg- und SnSbAg-Lötstellen bei 80 °C, dargestellt als Gesamtlebensdauer in Abhängigkeit von der Auslenkungsamplitude (a) und der gesamten mechanischen Dehnung (b) und der volumengemittelten Spannung (c), die zur Rissentstehung (N0) führt [15].](/images/stories/Abo-2023-09/plus-2023-09-099.jpg) Fig. 8: Fatigue curves of PbSnAg and SnSbAg solder joints at 80 °C, shown as total life as a function of deflection amplitude (a) and total mechanical strain (b) and volume-averaged stress (c) leading to crack initiation (N0) [15].

Fig. 8: Fatigue curves of PbSnAg and SnSbAg solder joints at 80 °C, shown as total life as a function of deflection amplitude (a) and total mechanical strain (b) and volume-averaged stress (c) leading to crack initiation (N0) [15].

A comparison of the reliability curves of the three solder alloys tested under identical conditions can be seen in Figures 9 a and 9 b. It can be seen that the lead-free solder joints have a longer service life. The tests in three-point bending mode were carried out at temperatures of 25 °C, 80 °C and 125 °C, while four-point bending was used at 175 °C. The trends are in very good agreement with the results of the PC and TC tests.

It is well known that the lifetime of solders under thermomechanical or isothermal mechanical loading conditions is due to a complex material behavior that depends on the accumulated plastic strain, AC stress and mean stress at the critical points of the components. Therefore, the lifetime model proposed here estimates the time to crack initiation in the solder joint by combining the Coffin-Manson-Basquin model with a multiaxial treatment of the Goodman relation, which also describes the effects of mean stress.

The lifetime model with the temperature-dependent material parameters α0, β, γ and δ is shown below, whereSeƒƒ is the effective equivalent stress and Nf is the number of cycles to failure.

The shares of the service life resulting from the various failure mechanisms are added according to the Miner rule of linear damage accumulation. In addition, the strain rate and temperature dependence of the inelastic deformation was described by the viscoplastic Anand model. The exemplary curve in Figure 9 c shows that the experimental lifetimes of the PbSnAg solder joints are well described by the damage accumulation model, which was used to determine the optimized values for the lifetime parameters. Details of the simulations can be found in [16].

The shares of the service life resulting from the various failure mechanisms are added according to the Miner rule of linear damage accumulation. In addition, the strain rate and temperature dependence of the inelastic deformation was described by the viscoplastic Anand model. The exemplary curve in Figure 9 c shows that the experimental lifetimes of the PbSnAg solder joints are well described by the damage accumulation model, which was used to determine the optimized values for the lifetime parameters. Details of the simulations can be found in [16].

![Abb. 9: Weibull-Diagramm der PbSnAg, Sn3.5Ag und SnSbAg Chip/Lot/DCB Verbindungen bis zum Ausfall bei einer Auslenkungsamplitude von 5,2 µm (a) 3PB-Versuch bei 125 °C (b), 4PB-Versuch bei 175 °C, (c) die durch das Modell bestimmten Lebensdauern im Vergleich zu den gemittelten experimentellen Lebensdauern für PbSnAg, dargestellt in einer doppelt logarithmischen Skala [16] Abb. 9: Weibull-Diagramm der PbSnAg, Sn3.5Ag und SnSbAg Chip/Lot/DCB Verbindungen bis zum Ausfall bei einer Auslenkungsamplitude von 5,2 µm (a) 3PB-Versuch bei 125 °C (b), 4PB-Versuch bei 175 °C, (c) die durch das Modell bestimmten Lebensdauern im Vergleich zu den gemittelten experimentellen Lebensdauern für PbSnAg, dargestellt in einer doppelt logarithmischen Skala [16]](/images/stories/Abo-2023-09/plus-2023-09-071.jpg) Fig. 9: Weibull diagram of the PbSnAg, Sn3.5Ag and SnSbAg chip/solder/DCB joints until failure at a deflection amplitude of 5.2 µm (a) 3PB test at 125 °C (b), 4PB test at 175 °C, (c) the lifetimes determined by the model compared to the averaged experimental lifetimes for PbSnAg, shown on a double logarithmic scale [16]

Fig. 9: Weibull diagram of the PbSnAg, Sn3.5Ag and SnSbAg chip/solder/DCB joints until failure at a deflection amplitude of 5.2 µm (a) 3PB test at 125 °C (b), 4PB test at 175 °C, (c) the lifetimes determined by the model compared to the averaged experimental lifetimes for PbSnAg, shown on a double logarithmic scale [16]

Evaluation of TLP (transient liquid phase) and Ag sintering compounds

Transient liquid phase (TLP) bonding and sintering are joining processes in which low melting temperatures are used to produce compounds with a high melting temperature. TLP bonds are achieved by solid-liquid interdiffusion of a low melting metal or alloy (e.g. Sn, Sn, In) with a high melting metal (e.g. Cu, Ag, Au, Ni) as a substrate. The complete transformation of the entire low-melting metal results in a compound consisting only of high-melting intermetallic compounds (IMCs). Depending on the compound used, the processing temperatures are around max. 350 °C.

In low-temperature sintering of Ag or Cu, a paste of metal particles of different sizes (micrometers to nanometers) is printed in a viscous state similar to solder pastes, dried and then sintered at approx. 230 °C without pressure or under increased pressure. The sintering process is based on solid-state diffusion, in which silver or copper particles are bonded to each other and to the metallization of the chip and substrate. A significant difference to soldering processes is that the formation and growth of brittle intermetallic interface phases in the Ag-Cu system is not possible when joining Cu substrates with silver. Since there is often an increased risk of flux inclusions, particularly in the case of large-area connections, such as in the assembly of power semiconductors, the use of flux-free processes such as sintering is of great advantage.

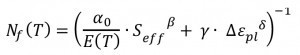

In the following example, the long-term reliability of TLP and Ag-sintered connections is examined. TLP joints were produced using Cu substrates and a 97Sn3Cu solder alloy as an intermediate layer under different conditions (temperature, pressure, time). Depending on the process parameters, the solder was partially or completely converted to intermetallic phases (IMC) to obtain three different compounds consisting of i) three phases (Cu3Sn/Cu6Sn5/solder), ii) two phases (Cu3Sn/Cu6Sn5) and iii) one phase (Cu3Sn)(Fig. 10 a, b, c).

The fracture probability plots of 3-PB cyclic tests at room temperature shown in Figure 10 e indicate that the highest reliability was obtained for the single-phase Cu3Sn compounds. The two-phase joints (Cu3Sn/Cu6Sn5) showed a slightly lower lifetime than the three-phase system with IMCs and residual solder. Failure analysis of the samples shows that in the two-phase system, the Cu3Sn/Cu6Sn5 interface is a weak point, while the crack in the Cu3Sn joint propagates either intergranularly or in the Cu substrate. These results are in good agreement with the higher shear and flexural strength values obtained for the Cu3Sn phase [20].

To enable a comparison between the service life of TLP compounds and Ag sintering, a series of tests was carried out with Ag-sintered Cu/Cu compounds(Fig. 10 d) [21]. The samples, which exhibited a static shear strength of about 30MPa, showed lower values than Cu3Sn TLPs, but still relatively good cyclic mechanical strength, as shown in Figure 10 e.

Although TLP and sintering are already recognized as processes for producing high-strength and temperature-resistant interconnects for power electronics applications, the long-term reliability and durability of these interconnects has not yet been sufficiently investigated. The presented method offers an effective way to evaluate such high-temperature joints where the temperature-dependent microstructural changes and creep effects are not dominant factors.

Fig. 10: (a) Overview and grain size distribution of the three types of TLP compounds consisting of Cu3Sn/ Cu6Sn5/97Sn3Cu solder (b), Cu3Sn/Cu6Sn5 (c), Cu3Sn (d) and overview and detail of the porous Ag-sintered compound (e) Failure probability of the Cu-Sn TLP compounds (deflection amplitude 5.3μm) and the Cu/Ag/Cu sintered compounds (deflection amplitude 5 μm) at 20 kHz / RT

Fig. 10: (a) Overview and grain size distribution of the three types of TLP compounds consisting of Cu3Sn/ Cu6Sn5/97Sn3Cu solder (b), Cu3Sn/Cu6Sn5 (c), Cu3Sn (d) and overview and detail of the porous Ag-sintered compound (e) Failure probability of the Cu-Sn TLP compounds (deflection amplitude 5.3μm) and the Cu/Ag/Cu sintered compounds (deflection amplitude 5 μm) at 20 kHz / RT

Summary

As part of the 'Christian Doppler Laboratory for Reliability of Interfaces in Electronics' at the Vienna University of Technology, a high-frequency isothermal cyclic bending test was developed to evaluate large-area interconnects in semiconductor test structures, with wide-ranging applications in research and development (R&D). The system successfully fulfilled the main requirements, such as the testing capability of relevant multilayer structures (chip/solder/ceramic substrate or SMD interconnects), defined failure criteria and a real-time method for failure evaluation.

In addition, a non-destructive in-situ method based on laser Doppler vibrometry for accelerated mechanical fatigue testing was introduced to detect crack formation and crack growth in semiconductor structures. The results demonstrated the applicability of this technique for the evaluation of large area solder joints in multilayer electronic devices and make it a promising alternative for the rapid evaluation and screening of solder materials or other electronic interconnects.

The excellent suitability of the method for damage assessment and reliable detection of crack formation was confirmed by tests on classic, high-lead and lead-free solders as well as sintered and TLP compounds used in high-temperature semiconductor elements. On the one hand, life curves up to complete failure ('end of life') or a defined failure criterion can be created in a very short time. On the other hand, in combination with FE simulations, the method enables a quantitative real-time determination of the degree of delamination of the respective structures.

Accelerated mechanical fatigue testing has proven to be a reliable and accurate method for determining key material properties required for the development of robust life prediction models. In addition, the method's versatility in application offers the potential for lifetime assessment for various electronic components (e.g. SMD interconnects).

These innovative techniques provide valuable tools for research and development and have the potential to accelerate development processes while improving the overall reliability of electronic devices and systems.

Literature

[1] 17th annual KPMG Global Semiconductor Industry Outlook, 2022

[2] M. Pecht: Product Reliability, Maintainability, and Supportability, J. of Electr. Pack, 8, (2009), doi:10.1115/1.279215

[3] T. Behrens: Infineon DA5 Consortiumm Customer Consumer Presentation from 6.4.2023, https://www.infineon.com/dgdl/DA5+Customer+Presentation+06042023.pdf?fileId=5546d4616102d26701610905cfde0005 (Retrieved: 14.08.2023)

[4] K. Siow: Die-Attach Materials for High Temperature Applications in Microelectronics Packaging, Springer (2019)

[5] EU RoHS Pack-23 Exemption Recommendations

[6] S. Menon; E. Georg; M. Osterman; M. Pecht: Overview of high lead solder (over 85 %) in the electronics in-dustry, J. Mater. Sci. Mater. Electron., Vol. 26, (2015), 4021-4030

[7] N. Heuck; R. Bayerer; S. Krasel; F. Otto; R. Speckels; K. Guth: Lifetime analysis of power modules with new packaging technologies (2015), 321-324,10.1109/ISPSD.2015.7123454

[8] T. Hunger; R. Bayerer: Reliability of Substrate Solder Joints from Power Cycling Tests PCIM (2009), 713-16

[9] M. Junghaenel; U. Scheuermann: Microelectron Reliab. 76-77, (2017), 480-84

[10] H. Wang; K. Ma; F. Blaabjerg: Design for reliability of power electronic systems, IECON 2012 - 38th Annual Conference on IEEE Industrial Electronics Society, (2012), 33-44

[11] Z. Li; K. Fushinobu; H. Haketa; R. Yasui; T. Shinoda: In-situ diagnosis of solder joint failure by means of thermal resistance measurement, Microelectronics Reliability, Vol. 123, (2021)

[12] D. May; B. Wunderle; R. Schacht; B. Michel: Transient thermal analysis as failure analytical tool in electronic packaging, Proc. 13th Eurosime Conf., (2012)

[13] A. Betzwar Kotas; G. Khatibi: Isothermal bending fatigue response of solder joints in high power semiconductor test structures, Microelectronics Reliability, Vol. 76-77, (2017), 357-361, https://doi.org/10.1016/j.microrel.2017.06.095 (Retrieved: 14.08.2023)

[14] G. Khatibi; A. Betzwar Kotas; M. Lederer: Effect of aging on mechanical properties of high temperature Pb-rich solder joints, Microelectron. Reliab, 85 (2018) 1-11

[15] M. Lederer; A. Betzwar Kotas; G. Khatibi: A lifetime assessment and prediction method for large area solder joints, Microelectronics Reliability, Volume 114, (2020), https://doi.org/10.1016/j.microrel.2020.113888 (Retrieved: 14.08.2023)

[16] M. Lederer; A. Betzwar Kotas; G. Khatibi: Lifetime modeling of solder joints based on accelerated mechanical test-ing and Finite Element Analysis, Power Electronic Devices and Components,Volume 4, (2023), https://doi.org/10.1016/j.pedc.2023.100034 (Retrieved: 14.08.2023)

[17] T. Walter; A. Betzwar Kotas; N. Kretschy; G. Khatibi: In-situ delamination detection in multi-layered semiconductor packages, Microelectronics Reliability (2023) - in press

[18] S.C. Yang; C.E. Ho; C.W. Chang; C.R. Kao: Massive spalling of intermetallic compounds in solder-substrate re-actions due to limited supply of the active element, Journal of Applied Physics, 101 (2007) 8, 084911, https://doi.org/10.1063/1.2717564 (accessed: 14.08.2023)

[19] A. Morozumi; H. Hokazono; Y. Nishimura; E. Mochizuki: Influence of Antimony on Reliability of Solder Joints Us-ing Sn-Sb Binary Alloy for Power Semiconductor Modules, Transactions of The Japan Institute of Electronics Packaging, 8, 1, 8-17, DOI:10.5104/jiepeng.8.8

[20] A. Betzwar Kotas; G. Khatibi; A. Steiger-Thrisfeld: High cycle fatigue behavior of Cu/Sn intermetallic compounds prepared by transient liquid phase bonding process, Materials Science Forum, 1016, 268-273, DOI: www.scientific.net/MSF.1016.268 (Retrieved: 14.08.2023)

[21] Z. Gökdeniz; G. Khatibi; J. Nicolics; C. Gierl-Mayer: Temperature Dependent Mechnical Properties of Sintered Sil-ver-Copper Joints, ISSE 2018 41st Int. Spring Seminar on Electronics Technology, https://doi.org/10.1109/ISSE.2018.8443659 (Retrieved: 14.08.2023)