Brief report CICMT 2024 and Symposium ESI 2024

This year, the Ceramic Interconnect and Ceramic Microsystems Technologies Conference (CICMT 2024) was held jointly with the 3rd Global Forum on Smart Additive Manufacturing, Design & Evaluation (Smart-MADE 2024) from April 10 to 12 in Osaka, Japan. By combining the two conferences, the breadth of the range of topics was also increased. In order to maintain the focus, the afternoon sessions for both sub-conferences ran parallel to each other. The structure of the event was somewhat unusual for the European participants: the joint plenary sessions offered two plenary lectures and four somewhat shorter keynote presentations each day. In the afternoon sessions, the presentations were quite tightly timed at 20 minutes, and the relatively high proportion of invited presentations, at around 40%, was also not quite typical. As expected, the majority of presentations were given by colleagues from Japan (23), Korea (5), China (4) and Taiwan (3), while the European participation of 10 presentations was dominated by Germany (7).

The Electronics and Systems Integration Symposium (ESI 2024), which was organized by the Microsystems Technology Cluster at Landshut University of Applied Sciences and supported by IMAPS Germany, took place on 17 April. Over 90 delegates took part in the event with 25 presentations and 7 posters, and seven exhibitors presented their products and services. The organizers were once again praised for the high quality of the organization, and the strong participation of students and doctoral candidates was also positive.

At the 2023 autumn conference in Munich, Rasched Sankari from Robert Bosch GmbH presented very interesting research results on the service life of wire bond connections on SiC power semiconductors. We would like to make the results available to a wider audience here:

Lifetime modeling of the top side contacts of SiC power semiconductors

Abstract

The ongoing electrification of automotive powertrains poses new challenges in terms of function and reliability. Therefore, SiC is used as a new generation of power semiconductors to meet the increasing requirements. With the establishment of highly reliable connection technologies, the aluminum wire bond for the top contact has proven to be the weakest element in terms of a failure mechanism. The aim of current work is to investigate the copper wire bond as a top contact for copper-plated SiC, which has been insufficiently researched to date. The test devices are stressed by an active temperature cycling test.

Introduction

The advancing electrification of the automobile places ever higher demands on function and reliability. The power modules of the inverter are a core element of the electrified powertrain. Power modules are known from the past, which were generally designed according to the same principle: The silicon power semiconductors are soldered onto a ceramic power substrate (DBC or AMB) and contacted on the top side using Al wire bonds. The module is then soldered onto a base plate or directly onto a cooler. In this process, the entire module is either hard encapsulated, transfer molded or alternatively soft encapsulated. The reliability-limiting system components are usually the lead-free solder joints. With the establishment of highly reliable connection technologies, such as Ag sintering, the Al wire bond has recently come into focus as a failure-determining element. The underlying failure mechanism has been investigated many times in experiments and simulations [1,2,3]. In order to improve the reliability of top-side contacts, especially on SiC, we propose copper wire bonding on copper-coated chips. This connection system, which has been little described so far, was investigated by means of active temperature load cycling tests.

Test setups

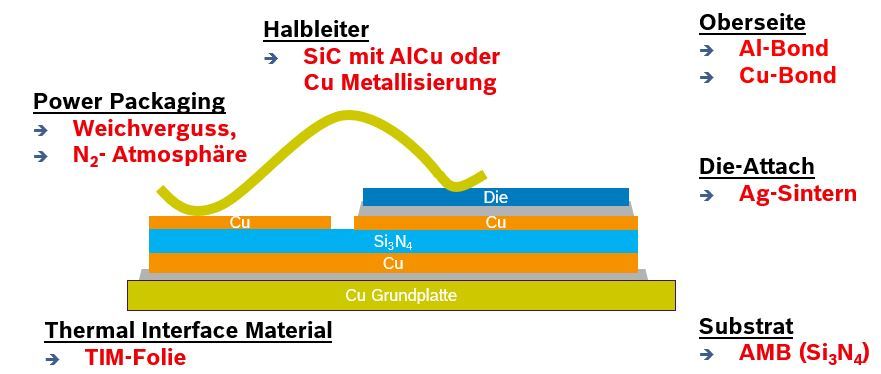

To ensure that the interaction between bonding wire and metallization can be investigated unaffected by damage in other parts of the assembly, a robust interconnection technique below the chip is required. The test device presented here fulfills this requirement and is based on current product designs. The structure shown in Figure 1 consists of a chip that is connected to the AMB using silver sintering. This consists of a stack of copper layers and a Si3N4 ceramic. 300 µm thick bonding wires made of aluminum and copper are used for the top side contacting. The AMB is soldered onto a copper base plate. To limit oxidation during the tests, the chips are soft potted with silicone or locally protected with an N2 atmosphere. The setups in Figure 2 show two different construction variants. The left setup shows a chip with 4 µm sputtered AlCu metallization and Al wire bonds. The right image shows a SiC chip with thicker electroplated Cu metallization and Cu bonding wires.

Fig.1: General structure of the test samples

Fig.1: General structure of the test samples

Fig. 2: Structure of the test devices, with 4 μm sputtered AlCu (left) and 30 μm electrodeposited Cu (right)

Fig. 2: Structure of the test devices, with 4 μm sputtered AlCu (left) and 30 μm electrodeposited Cu (right)

Active Power Cycling (APC)

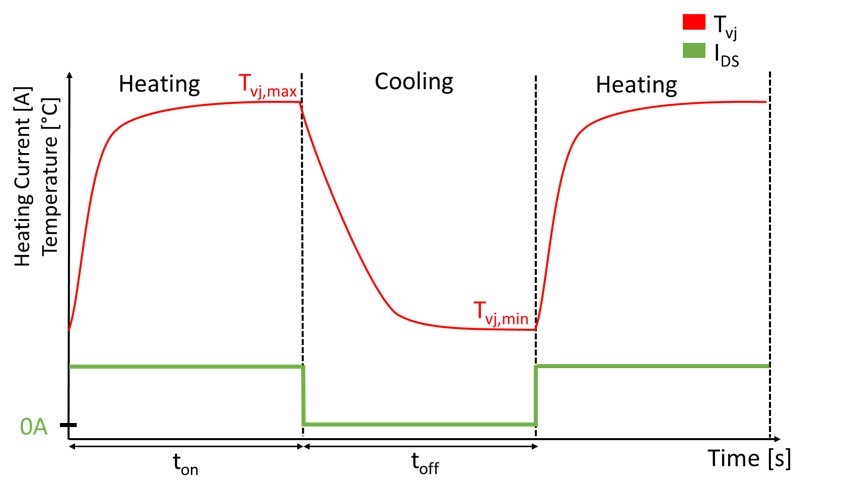

Figure 3 shows the schematic of an APC. The test devices are first heated to the desired maximum temperature by applying an active load current. After switching off the load current, the assembly cools down again to the temperature of the heat sink. This process is repeated cyclically, which leads to a thermomechanical load on the structure.

Fig. 3: Active power cycling test as a function of its parameters and the depiction of the temperature stroke

Fig. 3: Active power cycling test as a function of its parameters and the depiction of the temperature stroke

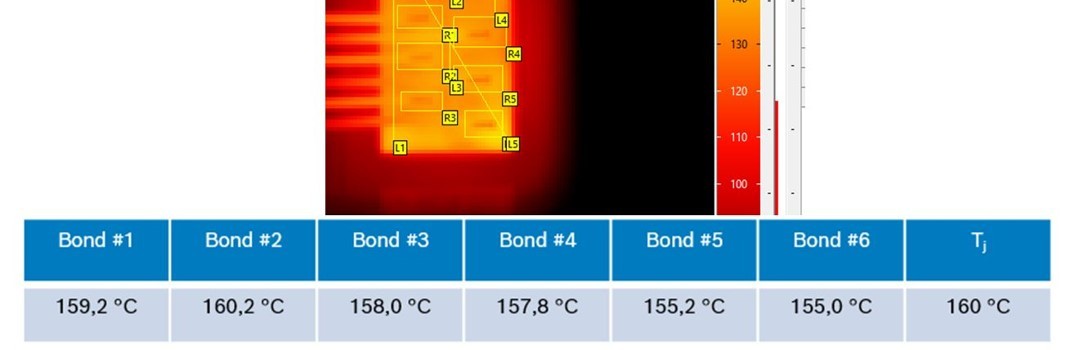

The degradation of the joints in the module is always accompanied by changes in the electrical parameters. According to [4,5], failure during the APC is defined by an increase in the drain-source voltage Uds by 5 % or the thermal resistance Rth by 20 %. Infrared measurements were carried out to visualize the temperature distribution on the chip surface during APC. The measurement in Figure 4 clearly shows that there is a slightly inhomogeneous temperature distribution on the SiC chip. There is a temperature difference of up to 5 K between the individual bond feet. This can be taken into account when evaluating the failure mechanisms.

Fig. 4: APC - IR measurement at 80 K stroke at 80 °C heat sink temperature of the bond feet in comparison to the virtually averaged Tj

Fig. 4: APC - IR measurement at 80 K stroke at 80 °C heat sink temperature of the bond feet in comparison to the virtually averaged Tj

Test methodology

The Cu assembly and connection technology (AVT) tends to oxidize easily. In order to reduce or eliminate the influence of oxidation, soft silicone encapsulation or the application of a local N2 atmosphere is used. A special silicone was used, which is compatible with the high requirements in the APC. The local N2 atmosphere was implemented using an additively manufactured cap system. The latter achieves oxidation-free Cu surfaces in the APC.

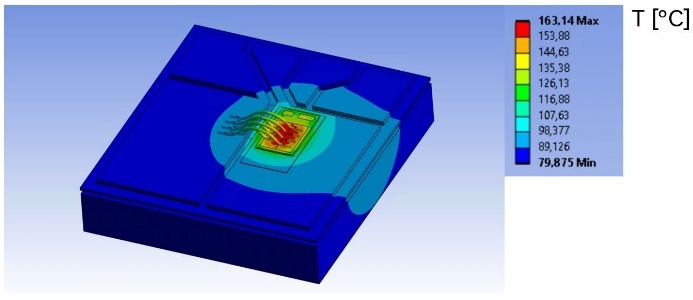

Fig. 6: Calculated temperature field at t=3s with ΔT=80 K

Fig. 6: Calculated temperature field at t=3s with ΔT=80 K

Results and discussion

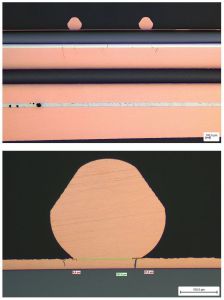

Fig. 5: Cross-sections of a tested SiC-Cu with ΔT=150 K after 51,000 cyclesThemodules with Al wire bonds showed a classic lift-off after 32,000 cycles after APC with ΔT 130 K. The crack ran along the zone between the bond feet and the metallization. This defect pattern is known from the literature [6]. The modules with Cu-AVT showed a different defect pattern. Damage in the form of vertical cracks was observed in the zone between the bond foot and metallization, as shown in Figure 5. However, even after more than 51,000 cycles at ΔT 150 K, the vertical cracks on the top do not initially provoke an electrical failure. The exact relationship between failure pattern and damage is currently being investigated in more detail. A thermomechanical simulation running in parallel serves to support the experimentally determined service life data from the APC. First, the thermal situation in the structure is simulated, as shown in Figure 6. This thermal load is then fed into the static thermomechanical calculation as a boundary condition.

Fig. 5: Cross-sections of a tested SiC-Cu with ΔT=150 K after 51,000 cyclesThemodules with Al wire bonds showed a classic lift-off after 32,000 cycles after APC with ΔT 130 K. The crack ran along the zone between the bond feet and the metallization. This defect pattern is known from the literature [6]. The modules with Cu-AVT showed a different defect pattern. Damage in the form of vertical cracks was observed in the zone between the bond foot and metallization, as shown in Figure 5. However, even after more than 51,000 cycles at ΔT 150 K, the vertical cracks on the top do not initially provoke an electrical failure. The exact relationship between failure pattern and damage is currently being investigated in more detail. A thermomechanical simulation running in parallel serves to support the experimentally determined service life data from the APC. First, the thermal situation in the structure is simulated, as shown in Figure 6. This thermal load is then fed into the static thermomechanical calculation as a boundary condition.

Summary

In this work, the degradation phenomenon of 300 µm thick Al and Cu wire bonds on SiC power semiconductors with AlCu and Cu metallizations in the APC was investigated. In the first step, the temperature distribution on the SiC surface was investigated during the test. An oxide protection chamber was developed for oxidation-free testing of the SiC modules with Cu-AVT. The investigation of the Al-AVT shows a standard failure due to classic lift-off of the bond feet in the interface. Vertical cracks appeared as a new failure pattern in the Cu-AVT on SiC. We are currently investigating how these cracks can lead to module failure.

Acknowledgments

Parts of this work are supported by the H2020 KDT JU program of the European Union within the TRANSFORM project "Trusted European SiC Value Chain for a greener Economy" - KDT grant no. 101007237 - and the German Federal Ministry of Education and Research grant no. 16MEE0127K. The authors would like to thank all supporting institutions and all Transform project partners.

Calendar of events

Venue | Period | Event name | Organizer |

Berlin | September 11 - 13, 2024 | Electronics System-Integration Technology Conference (ESTC) | IEEE, IMAPS |

Boston, USA | Sept. 30 - Oct. 3, 2024 | 57th International Symposium on Microelectronics | IMAPS USA |

Munich, Germany | October 17-18, 2024 | Fall Conference | IMAPS DE |

Tours, France | November 28, 2024 | Power Electronics and Packaging European Workshop | IMAPS France |

Phoenix, USA | March 3 - 6, 2025 | Device Packaging Conference | IMAPS USA |

IMAPS Germany - Your association for packaging technology

IMAPS Germany, part of the International Microelectronics and Packaging Society (IMAPS), has been the forum in Germany for all those involved in microelectronics and packaging technology since 1973. With almost 300 members, we essentially pursue three important goals:

- we connect science and practice

- we ensure the exchange of information among our members and

- we represent the point of view of our members in international committees.

Imprint

IMAPS Germany e. V.

Kleingrötzing 1, D-84494 Neumarkt-St. Veit

1st Chairman: Prof. Dr.-Ing. Martin Schneider-Ramelow, Director of the Fraunhofer Institute for Reliability and Microintegration (IZM),

Treasurer

(for questions about membership and contributions):

Ernst G. M. Eggelaar,

You can find detailed contact information for the members of the Executive Board at www.imaps.de

(Executive Board)

Sources

[1] M.S. Broll and U. Geissler and J. Höfer and S. Schmitz and O. Wittler and M. Schneider-Ramelow and K.D. Lang, "Correlation between mechanical properties and microstructure of different aluminum wire qualities after ultrasonic bonding", in Microelectronics Reliability, 55 (2015) 1855-1860

[2] U. Geissler and M. Schneider-Ramelow and H. Reichl, "Hardening and softening in AlSi1 bond contacts during ultrasonic wire bonding", in IEEE Trans. Compon. Packag. Technol., 32 (4) (2009) 794-799

[3] M. Schneider-Ramelow and C. Ehrhardt, "The reliability of wire bonding using Ag and Al", in Microelectronics Reliability, 63 (2016) 336-341

[4] J. Lutz and T. Herrmann and M. Feller and R. Bayerer and T. Licht, "Power cycling induced failure mechanisms in the viewpoint of rough temperature environment", in European Conference on Power Electronics and Applications (2007)

[5] M. Held and P. Jacob and G. Nicoletti and P. Scacco and M. -. Poech, "Fast power cycling test of IGBT modules in traction application", in Proceedings of Second International Conference on Power Electronics and Drive Systems (1997)

[6] J. Goehre and M. Schneider-Ramelow and U. Geissler and K.D. Lang, "Interface Degradation of Al Heavy Wire Bonds on Power Semiconductors during Active Power Cycling measured by the Shear Test", in CIPS (2010), Paper 3.4