Siemens Digital Industries Software announces new certifications and collaborations with longtime partner TSMC, including the qualification of several Siemens EDA product lines for the foundry's latest processes.

Dan KochpatcharinAccording toDan Kochpatcharin (Head of Design Infrastructure Management Division, TSMC), collaboration with ecosystem partners such as Siemens supports joint customers. This offers design solutions that "better leverage the benefits of our process technologies in terms of performance and energy efficiency."

Dan KochpatcharinAccording toDan Kochpatcharin (Head of Design Infrastructure Management Division, TSMC), collaboration with ecosystem partners such as Siemens supports joint customers. This offers design solutions that "better leverage the benefits of our process technologies in terms of performance and energy efficiency."

Calibre for TSMC's N2 process

Siemens' Calibre nmPlatform tool for IC verification is now fully certified for TSMC's N2 process. This includes Calibre nmDRC software, Calibre YieldEnhancer software, Calibre PERC software and Calibre nmLVS software. TSMC and Siemens have also jointly certified Siemens' mPower analog software for transistor-level electromigration and IR drop (EM/IR) for TSMC's N4P process. This enables mPower's EM/IR signoff solution to be applied to next-generation analog or high-frequency designs.

Solido Design Environment and Analog FastSPICE

TSMC's N4P, N3E and N2 Custom Design Reference Flow (CDRF) now works with Siemens' Solido Design Environment software. This enables variant-aware verification at high sigma. In addition, Siemens' Analog FastSPICE platform for circuit verification of nanoscale analog, RF, mixed-signal, memory and custom digital circuits now has certification for the foundry's N5A, N3E, N3P and N2 processes. As part of the CDRF flow for the N4P, N3E and N2 processes, the Analog FastSPICE platform supports TSMC's Reliability Aware Simulation technology. It also considers IC aging and self-heating in real time.

Place and Route with N3 certifications for Aprisa

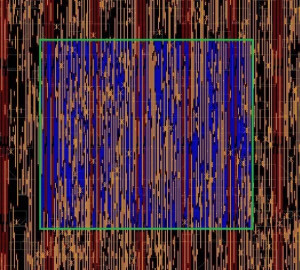

Aprisa supports methods to better solve IR drop issues on advanced nodes. The Power Grid Enhancement is shown for one level (M3 in blue) above the marked hotspot region (green square)Siemensunderscores its commitment to digital implementation and announces another milestone for its Aprisa Place and Route solution: TSMC has certified the tool for the N3E process. This accelerates the migration to this node with Aprisa's ease of use.

Aprisa supports methods to better solve IR drop issues on advanced nodes. The Power Grid Enhancement is shown for one level (M3 in blue) above the marked hotspot region (green square)Siemensunderscores its commitment to digital implementation and announces another milestone for its Aprisa Place and Route solution: TSMC has certified the tool for the N3E process. This accelerates the migration to this node with Aprisa's ease of use.

TSMC certifies 3DIC solutions from Siemens

Siemens has made significant progress with TSMC in certifying several 3DIC solutions for TSMC's 3D fabric technologies. TSMC has certified 3Dblox 2.0 with Calibre 3DSTACK software for analysis and circuit verification. This includes DRC (design rule check) and LVS (layout versus schematic) checks within chiplets for TSMC 3DFabric technologies.

In addition, TSMC has certified several Tessent 3DIC solutions, including Tessent Hierarchical DFT, Tessent Multi-Die with enhanced IEEE 1838 test access ports (TAPs), support for native flexible parallel ports (FPP) with streaming scan networks (SSN) and IJTAG networking technologies according to IEEE 1687. Both partners are strengthening their commitment to 3DIC test ecosystems within TSMC 3Dblox. This includes the KGD loopback test (known good die) and physical die-to-die fault detection according to BMAP and PMAP standards.

Siemens Digital Industries Software supports companies in their digital transformation with the Xcelerator business platform. This software and the digital twin make it possible to optimize design, engineering and manufacturing processes to turn today's ideas into sustainable products of the future.