Un libro publicado en 2024 por John H. Lau, de Unimicron Technology Taiwan, aclara los requisitos del embalaje en el entorno tecnológico del ensamblaje de componentes y módulos electrónicos.

En 491 páginas, John Lau presenta estudios teóricos y prácticos sobre diseño, materiales, procesos, fabricación y fiabilidad de una amplia gama de tecnologías de ensamblaje y conexión. El libro cubre los aspectos clave del empaquetado, centrándose en el diseño, los materiales, los procesos, la fabricación y la fiabilidad de la tecnología flip-chip, la unión híbrida y la tecnología fan-in y fan-out. También se tratan los principios y la tecnología de ensamblaje y embalaje (AVT), con mayor énfasis en la AVT. John Lau presenta estudios detallados que profundizan en los siguientes aspectos: Wafer bumping, tecnología flip-chip, underfill y fiabilidad, chip-to-wafer, wafer-to-wafer, unión híbrida, WLCSP, WLCSP moldeado por 6 lados, FOWLP en sustratos híbridos con PID, ABF y grandes intercaladores orgánicos, comunicación entre chiplets e integración heterogénea AVT, óptica a bordo, óptica near-package y óptica co-package.

Tecnología flip-chip

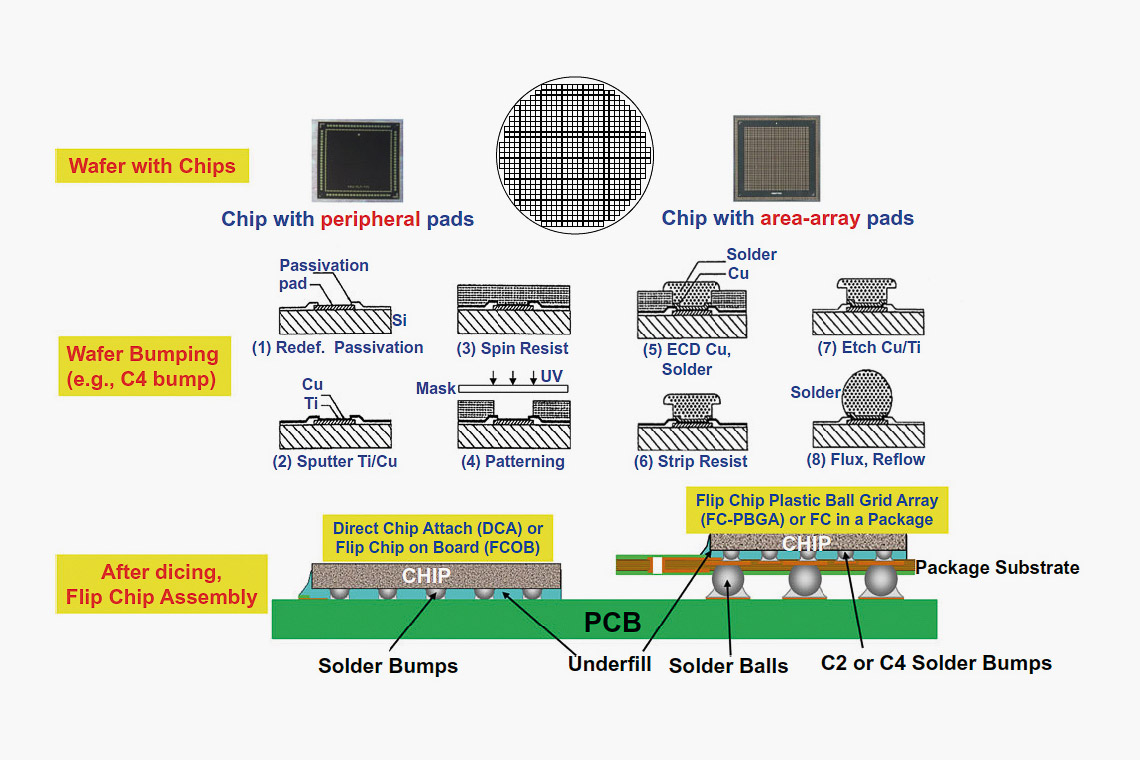

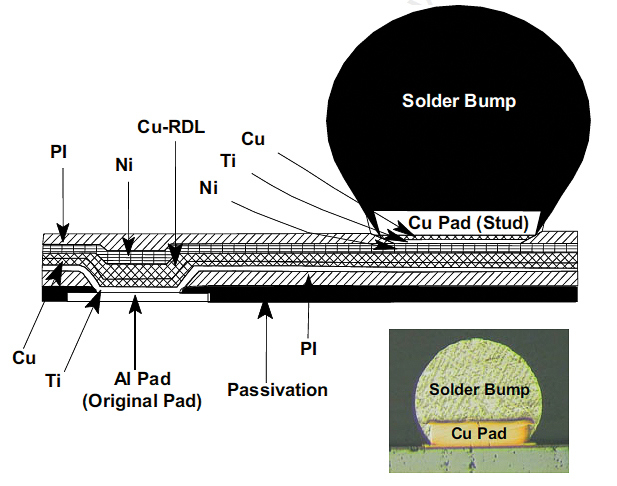

John Lau describe en detalle la tecnología flip-chip, la unión híbrida Cu-Cu, la tecnología fan-in y fan-out, la comunicación entre chiplets (puentes) y la óptica co-packaged. La tecnología flip-chip (FC) se subdivide en el flujo de procesos con fijación directa del chip (DCA) o flip-chip sobre sustratos BGA para montaje en PCB. La tecnología FC se define además por el montaje en sustratos cerámicos, orgánicos y de silicio. El bumping de obleas mediante impresión por estarcido se considera un requisito previo básico. Lau enumera los principales factores que influyen en la impresión de pasta de soldadura (operario, entorno, parámetros de impresión, impresora, esténcil, oblea, rasqueta y pasta de soldadura) y los factores de control (Taguchi DOE para experimentos L8 y L4 con determinación del volumen de soldadura). El volumen de bump de soldadura en la matriz se determina utilizando el análisis Taguchi con factores principales (Análisis de Varianza, ANOVA). También se presenta el bumping de obleas por galvanoplastia, y se comparan los métodos de bumping de obleas por ECD o galvanoplastia para bumps C4 por Cu con bumps C4 y bumps C2 (Cu Pillar y Solder Cap).

A continuación, John Lau presenta los sustratos de flip-chip (Printed Cicuit Board, Built-Up Package Substrates, Coreless Package Substrate, Bond on Lead, Embedded Trace Substrates, Thin Film Layers on Build-Up Package Substrates). También se tratan los sustratos de paquetes FC, EMC/RDL en fan-out, intercaladores TSV activos y pasivos, paquetes FC-puente Si, incrustados en sustratos orgánicos, y sustratos de paquetes FC-puente Si, incrustados en EMC en fan-out con RDL. John Lau también presenta el montaje flip-chip. La unión directa Cu-Cu TCB, la unión directa Cu-Cu a temperatura ambiente (híbrida), la soldadura por reflujo C4 con relleno, la soldadura por reflujo C2 con relleno, la TCB con baja fuerza de unión y relleno y la TCB C2 con alta fuerza de unión (NCP y NCF) completan los procesos de unión. A continuación, se enumeran los materiales y las aplicaciones y se analiza su fiabilidad.

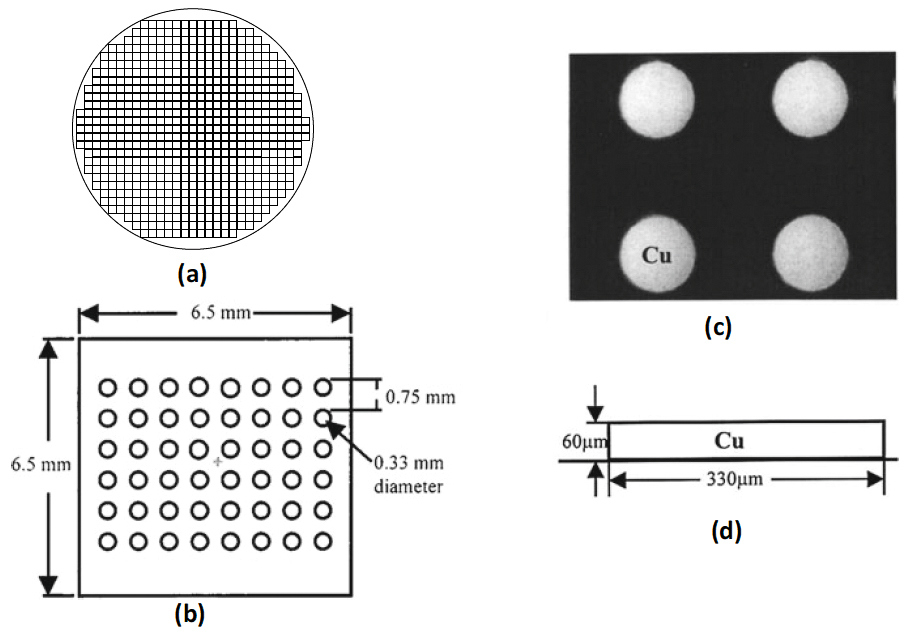

Fig. 2:

Fig. 2:

a: Disposición de una oblea de 200 mm

b: Dimensiones y espaciado de chips y pads

c: Pads de cobre -

d: Geometría de los pads de cobre

Unión híbrida

Recientemente, la unión híbrida ha cobrado cada vez más importancia. En el segundo capítulo, se presenta desde el punto de vista tecnológico y procedimental y se hace referencia a él basándose en el ECTC 2023 con un total de 80 artículos. La unión híbrida sin bultos también se conoce como interconexión de unión directa (DBI). Fue patentada por el Research Triangle Institute de EE.UU. en 2000. DBI se utiliza en la producción a gran escala en Sony desde 2026 y en Yangtze Memory Technology desde 2021.

A continuación, se describe la unión híbrida Cu-Cu bumpless de última generación y se presenta la unión híbrida de Samsung como una tecnología de unión híbrida Cu multipila (HCB), en la que el método multipila 16H se caracteriza por el reflujo de soldadura TCB flip-chip. La unión híbrida puede realizarse como D2D (Die to Die), D2W (Die to Wafer) y W2W (Wafer to Wafer). El pegado híbrido de Cu (HCB) se realiza con chips bumpless y Cu sobre pads de Cu. La altura del paquete es menor que con TCB y chips bumped flip y sin huecos entre los chips (gapless). El mecanismo HCB se pone en marcha después del CMP (pulido químico-mecánico). El CMP se lleva a cabo en las superficies de unión, por ejemplo, de un troquel de memoria después del corte en cubos y de la oblea intermedia. La rugosidad obtenida es decisiva para la aproximación de las superficies de Cu y la adaptación esperada de las superficies.

Tras la unión previa con pilas completas, la unión entre los óxidos se refuerza mediante recocido a alta temperatura. Las almohadillas de Cu de los chips superior e inferior se expanden y forman una conexión eléctrica tras la difusión. Uno de los retos del HCB es la gestión térmica. Al no haber huecos entre los chips, la resistencia térmica vertical es menor que en la variante flip-chip con huecos entre los microbumps. A continuación se comparan las tecnologías y diseños de varios competidores (Samsung, SK Hynix, Micron, Mitsui, Sony, CEA-Leti, TEL, Applied Materials, Intel, TSMC, MKS, Resonac, Adeia, TU Dresden, EVG, Ieme, UCLA). Esto demuestra el alcance con el que se sigue desarrollando y evaluando el HCB.

Tecnología Fan-in

En el tercer capítulo se analizan las ventajas e inconvenientes de la tecnología Fan-in (WLCSP). La característica especial de la mayoría de los WLCSP es el uso de RDL (capas de redistribución) metálicas (normalmente de Cu) para conectar las almohadillas periféricas de paso fino de los chips en la oblea con pasos mucho mayores de almohadillas planas. Las propiedades de fluencia de los WLCSP sin Pb van acompañadas de análisis estructurales, caracterización de las propiedades de los materiales, propiedades de las interfaces, análisis de deformación y tensión, propiedades de envejecimiento cíclico, tensión de cizallamiento dependiente del tiempo y deformación de fluencia dependiente del tiempo de las estructuras de interconexión.

Fig. 3: Fan-in de los pads periféricos originales

Fig. 3: Fan-in de los pads periféricos originales

Tecnología Fan-out

En el cuarto capítulo se analiza la tecnología fan-out. El uso de un RDL en fan-out lleva el circuito desde la almohadilla metálica del chip, en la oblea y las bolas de soldadura hasta las almohadillas metálicas de la placa de circuito impreso (eWLB). Las ventajas de FOWLP en comparación con PBGA con un flip chip con protuberancias de soldadura son un menor coste, un perfil de paquete más bajo, la eliminación del sustrato, la eliminación de las protuberancias de la oblea, la eliminación del reflujo del flip chip, la eliminación del relleno, un mejor rendimiento eléctrico, un mejor rendimiento térmico, un camino más fácil hacia el sistema en paquete y el empaquetado de CI en 3D, y una mayor fiabilidad a nivel de placa. Existen básicamente dos opciones para un FOWLP: chip-first o chip-load. A su vez, existen dos opciones para el método chip-first: Cara abajo (Die Down) y Cara arriba (Die Up). El método chip-load (RDL primero) sólo permite die-face-down.

Puentes

John H. Lau, 'Flip Chip, Hybrid Bonding, Fan-In, and Fan-Out Technology',

John H. Lau, 'Flip Chip, Hybrid Bonding, Fan-In, and Fan-Out Technology',

Springer Nature Scientific Publishing Services,

Singapore 2024

ISBN 978-981-97-2139-9.El quinto capítulo trata de la comunicación entre chiplets (puentes). La diferencia más importante entre chiplet e integración heterogénea es que el chiplet es un método de diseño de chips, mientras que la integración heterogénea es un método de empaquetado de chips. Existen al menos cinco diseños diferentes de chiplet e integración heterogénea:

- División de chips e integración heterogénea (impulsada por la optimización de costes y tecnología.

- División de chips e integración heterogénea (impulsada por el coste y el rendimiento de la fabricación de semiconductores)

- Sistemas múltiples e integración heterogénea con tecnología de capa fina directamente sobre sustratos de encapsulado (integración de CI 2.1D).

- Sistemas múltiples e integración heterogénea con intercaladores sin TSV (integración de CI 2.3D)

- Sistemas múltiples e integración heterogénea con intercaladores TSV (integración de CI en 2,5D y 3D).

Además, se tratarán los temas Puente de unión híbrido con protuberancias C4 en el sustrato del paquete y la oblea de chiplet, Puente Ridge incrustado en Fan-Out EMC con RDL, el proceso Bridge-First and Face-Up de Applied Material, el proceso Bridge-First and Face-Down de Unimicron y el proceso Bridge-Last de IME.

Tecnología de envasado impulsada por la inteligencia artificial (IA)

Una de las tecnologías avanzadas de envasado más populares es la integración de circuitos integrados en 2,5D o 3D. La unidad central de procesamiento (CPU), la unidad de procesamiento gráfico (GPU) y la memoria de gran ancho de banda se apoyan en intercaladores pasivos (2,5D) o activos (3D) a través de vías de silicio (TSV) sobre un sustrato de embalaje de acumulación. Por último, todo el módulo se monta en una placa de circuito impreso con matriz de rejilla de bolas (BGA), bolas de soldadura y pasta de soldadura. Este sistema de chiplet múltiple y paquete integrado heterogéneo está impulsado por el alto rendimiento y el factor de forma. Está diseñado para aplicaciones HP de muy alta densidad. CEA-Leti publicó el primer artículo sobre integración de CI en 2,5D en IEEE/ECTC 2005 e IEEE/ECTC 2006. El primer producto 2,5D (Virtex-7 HT Family) fue entregado por Xilinx y TSMC en 2013. AMD distribuyó la GPU Radeon R9 FuryX, Nvidia la GPU Pascal 100, Fujitsu la Fugaku (CPU A64FX) y Graphcore la Bow (una unidad de procesador inteligente). Recientemente, Nvidia presentó su GPU A100 (826 mm2) con seis intercaladores HBM2 y TSV y la GPU H100 para aplicaciones de IA.

Óptica coempaquetada

Las ópticas coempaquetadas (CPO) son métodos de empaquetado heterogéneamente integrados del motor óptico (OE), que consta de un CI fotónico (PIC) y el motor eléctrico (EE), y éste a su vez consta del CI electrónico (EIC) y el ASIC. La fotónica de silicio es la integración de EIC y PIC en el sustrato de silicio (oblea) con tecnología CMOS complementaria. Las aplicaciones incluyen centros de datos y diversas integraciones heterogéneas, que Lau trata en detalle.

Conclusión

En general, el libro de John H. Lau es una excelente referencia para los procesos y tecnologías avanzados de ensamblaje de dispositivos y módulos en ingeniería y para los estudiantes de tecnología de envasado y ensamblaje. Cada capítulo está vinculado a una extensa bibliografía.