Convocatoria de ponencias para CICMT 2022 - Tecnologías de interconexión cerámica y microsistemas cerámicos

Viena, 13 al 15 de julio de 2022

La conferencia "Ceramic Interconnect and Ceramic Microsystems Technologies" (CICMT) reúne una gran variedad de disciplinas. Se centra en el intercambio de experiencias y la promoción de oportunidades para acelerar la investigación, el desarrollo y la aplicación de tecnologías de interconexión y microsistemas cerámicos. Lanzada originalmente por IMAPS Norteamérica, la conferencia se ha celebrado en varios lugares de EE.UU., Europa y Asia desde 2008. Después de que IMAPS Alemania ya coorganizara las conferencias de Múnich, Erfurt y Dresde, la sede de este año es Viena.

Esta conferencia internacional ofrece tecnología cerámica tanto para microsistemas como para aplicaciones de interconexión en un programa técnico multipista.

El tema de interconexión cerámica se centra en productos cerámicos de interconexión de alto rendimiento, rentables y fiables, para entornos extremos en los sectores de automoción, aeroespacial, iluminación, solar y comunicaciones.

El tema de los microsistemas cerámicos se centra en las nuevas aplicaciones y los nuevos productos que aprovechan la capacidad de las estructuras cerámicas tridimensionales para integrar envases con funciones microfluídicas, ópticas, de microrreactores y sensores.

Imagen: Oficina de Turismo de Viena/Christian Stemper

Imagen: Oficina de Turismo de Viena/Christian Stemper

Las tecnologías de cerámica multicapa, película fina, colado en cinta, híbrido de película gruesa, escritura directa y prototipado rápido son comunes a ambos temas, con especial atención a los materiales, procesos, prototipado, diseño avanzado y oportunidades de aplicación. Las sesiones y los temas de presentación previstos incluyen

1. materiales funcionales para dispositivos pasivos/activos y sus propiedades

1. materiales funcionales para dispositivos pasivos/activos y sus propiedades

- Materiales dieléctricos LTCC/ULTCC para microondas/ondas milimétricas

- Compuestos dieléctricos/ferroeléctricos/piezoeléctricos

- Materiales ferroeléctricos/piezoeléctricos/piroeléctricos/ferríticos/multiferroicos

- Cerámicas sensibles/materiales termoeléctricos/electrocalóricos

- Pastas/tintas/lechadas para electrónica

2. tecnologías de procesamiento de materiales y fabricación de dispositivos

- LTCC/HTCC y procesamiento de cerámica y vidrio multicapa

- Procesado emergente a temperatura ultrabaja, temperatura ambiente y sinterizado en frío

- Fabricación aditiva/impresión 3D/escritura directa

- Procesado avanzado de películas gruesas

- Tecnologías de estructuración fina

- Tecnologías emergentes de incrustación/integración

3. diseño, modelización, simulación, caracterización y fiabilidad

3. diseño, modelización, simulación, caracterización y fiabilidad

- Diseño, realización y caracterización de metamateriales

- Diseño, modelización y simulación de dispositivos de alta frecuencia

- Caracterización de materiales y dispositivos

- Fiabilidad, vida útil y estimación de fallos de materiales y dispositivos

- Gestión térmica/simulación de transferencia térmica

4. dispositivos y sistemas para aplicaciones emergentes

- Circuitos, antenas y filtros para MHz, GHz y THz para comunicaciones

- Automoción/aeroespacial/electrónica médica/optoelectrónica

- Electrónica flexible/usable

- Sensores y actuadores físicos, químicos y biológicos integrados

- Embalaje e integración de dispositivos MEMS y BioMEMS

- Baterías/células de combustible/sistemas de conversión de energía

- Microrreactores/dispositivos microfluídicos

Exposición de acompañamientoLas ponencias completas deben enviarse antes del 15 de mayo de 2022 y deben cargarse por separado después de que se hayan aceptado los resúmenes. Todas las ponencias se presentarán y publicarán en inglés. En caso de problemas con el sistema en línea, póngase en contacto con la oficina de la conferencia por correo electrónico

Exposición de acompañamientoLas ponencias completas deben enviarse antes del 15 de mayo de 2022 y deben cargarse por separado después de que se hayan aceptado los resúmenes. Todas las ponencias se presentarán y publicarán en inglés. En caso de problemas con el sistema en línea, póngase en contacto con la oficina de la conferencia por correo electrónico

Se espera que la CICMT 2022 vuelva a ser un evento presencial. Como expositor, tendrá la oportunidad única de mostrar sus productos y servicios a un público interesado de usuarios, desarrolladores e investigadores influyentes. Los horarios de la exposición están organizados para maximizar la exposición de los expositores. Las pausas para el café están previstas en la zona de exposición para que todos los asistentes puedan reunirse formal e informalmente según les convenga. Los asientos se asignarán por orden de llegada. Haremos todo lo posible por satisfacer sus necesidades y peticiones especiales.

En breve dispondremos de información detallada sobre opciones y tarifas.

Presidencia general:

Ulrich Schmid, TU Viena

Vicepresidente general:

Markus Eberstein, TDK Sensors

Comité organizador técnico:

- Simon Ang, Centro de Electrónica de Alta Densidad, Universidad de Arkansas

- Heli Jantunen, Universidad de Oulu

- Eung Soo Kim, Universidad de Kyonggi

- Soshu Kirihara, Joining and Welding Research Institute, Universidad de Osaka

- Daniel Krueger, Honeywell

- Zhifu Liu, Instituto de Cerámica de Shanghai de la Academia China de Ciencias

- Jens Müller, Universidad Tecnológica de Ilmenau

- Uwe Partsch, Fraunhofer IKTS

- Steve Dai, Laboratorios Nacionales Sandia

- Michael Schneider, TU Viena

Patrocinadores técnicos:

- IMAPS Alemania e. V.

- IMAPS Sociedad Internacional de Microelectrónica y Embalaje

- ACerS - Sociedad Americana de Cerámica

Tecnología de interconexión en entornos hostiles para envases tridimensionales

J. Bickel [1,3], Joachim Scherer [4], M. Schneider Ramelow [2,3], K.-D. Lang [2,3], H.-D. Ngo [1,2]

Ha Duong Ngo puede presumir de haber concluido con éxito un proyecto sobre "Metalización 3D mediante pulverización catódica a presión atmosférica para carcasas de sensores en entornos difíciles (hilo 3D)".

Se desarrolló una tecnología que utiliza la pulverización catódica a presión atmosférica para aplicar conductores de película fina a piezas cerámicas en bruto para carcasas de sensores con el fin de crear la conexión eléctrica entre el sensor y el exterior de la carcasa. El sistema metálico de alta temperatura depositado se estructuró con éxito mediante tecnología de grabado fotoelectroquímico. Las primeras muestras demuestran la flexibilidad del proceso, que permite adaptar la geometría cerámica a las condiciones ambientales y al sistema utilizado.

1. Motivación

En el campo de la electrónica de SiC, en los últimos años se han realizado cada vez más mejoras en el ámbito de los entornos agresivos. Especialmente en términos de resistencia a altas temperaturas. Mientras que al principio sólo se utilizaban transistores sencillos (P. G. Neudeck, 2008), ahora son posibles los primeros circuitos más complejos en 6H-SiC (M. Shakir, 2019). También en el sector de los sensores micromecánicos existen desde hace varios años soluciones para temperaturas de 500 °C (L. Y. Chen, 2013) (A. A. Ned, 1998). Sin embargo, el factor limitante hoy en día suele ser la circunstancia de una tecnología de interconexión (TIC) y una tecnología de embalaje fiables y económicas. Debido a las altas temperaturas y a los diferentes CET de los distintos materiales que se utilizan, solo se pueden considerar unas pocas materias primas para las TIC de alta temperatura. Los materiales obvios son la cerámica y, para los sistemas de bajo coste, especialmente el Al2O3. La unión de hilos finos de platino y oro es adecuada para el nivel de interconexión entre el chip y el sustrato (L. Coppola, 2007).

2 Estado de la técnica

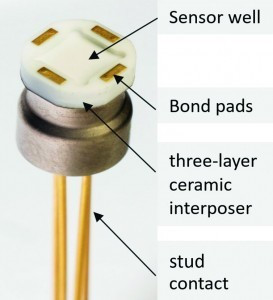

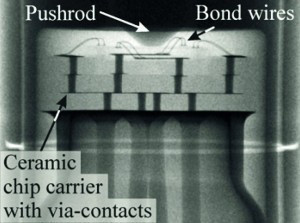

Dado que el Al2O3, al igual que otras cerámicas, es difícil de modelar por métodos microtecnológicos, las posibilidades de las TIC son muy limitadas. Por lo general, se utilizan pastas de película gruesa de oro y platino sobre sustratos planares (R. Zeiser, 2015). Las desventajas son el mayor consumo de recursos debido a los límites tecnológicos y no físicos, así como el hecho de que no se pueden realizar vías de agujeros pasantes ni estructuras 3D. En la actualidad, para establecer conexiones eléctricas en tres dimensiones desde el nivel del chip hasta el entorno, se suele utilizar un proceso de unión de espárragos a través de orificios. Con este sistema, se necesita un gran número de pasos para colocar el perno de metal sólido a través del orificio de la cerámica. Después, capa por capa, hay que apilar los materiales unos sobre otros. Un sistema apilado de este tipo se muestra en las figuras 1 y 2 y se utiliza desde hace varios años para su aplicación en sistemas de medición de sensores de presión (H. D. Ngo, 2012).

3 Enfoque técnico

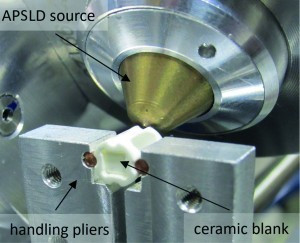

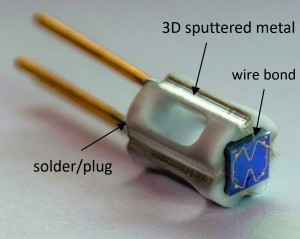

Para superar los inconvenientes de las tecnologías existentes, hemos desarrollado una solución que utiliza la tecnología de deposición de capas por pulverización catódica a presión atmosférica (APSLD) (J. Bickel, 2019) para permitir el enrutamiento de señales en sustratos cerámicos especiales impresos en 3D utilizando metalización de platino y oro. La tecnología APSLD se utiliza para depositar aditivamente el metal directamente y en un proceso estructurado en muescas que se encuentran a lo largo del lateral de un cilindro. El metal sólo cubre la superficie en la muesca, como puede verse en las figuras 3 y 4. Además, el recubrimiento de metalización se aplica sobre las caras extremas del cilindro. Esto permite enmarcar y soldar posteriormente la cerámica según sea necesario, incluso con materiales conductores como el Invar o el Kovar, y ponerla en contacto desde las superficies superior e inferior. La unión por hilo delgado es muy adecuada como solución de contacto a nivel de chip. En este sistema, se pueden utilizar contactos de soldadura SMD en la parte inferior, o se puede acoplar un intercalador FR4, ya que la tensión térmica en la parte inferior ya no se encuentra en el rango crítico y puesto que aquí ya no existen altas temperaturas.

4 Discusión

Debido a la gran flexibilidad del proceso, la geometría de la cerámica puede adaptarse según se requiera a las condiciones ambientales y al sistema utilizado. Cuando se aplica platino puro como material conductor, se pueden utilizar espesores de capa de platino de 200 a 300 nm para conductores de 10 mm de longitud con una resistencia de 10 Ohm, con lo que se pueden conseguir unos costes de consumo de tecnología y de material para la metalización de tan sólo unos céntimos por conductor. Se trata de importantes reducciones de costes en comparación con las conexiones de metal sólido de los sistemas estándar actuales. El conductor puede aplicarse de forma totalmente automática a cualquier material sólido, eliminando la necesidad de más pasos de montaje y manipulación para la fabricación del propio envase.

Empresas:

[1] University of Applied Sciences, Berlín, Alemania

[2] Fraunhofer IZM, Berlín, Alemania

[3] Technische Universität Berlin, Berlín, Alemania

[4] Aurion Anlagentechnik GmbH, Seligenstadt, Alemania

Referencias:

A. A. Ned, R. S. (1998), 6H-SiC pressure sensor operation at 600 °C, Fourth International High Temperature Electronics Conference. HITEC

H.D. Ngo, (2012), Liquid-free SOI-based piezoresistive pressure sensor for measurement up to 400 °C, IEEE Sensors, pp. 100-114, Taiwán

J. Bickel, H.-D. N.-D, (2019), Increasing the productivity of the novel atmospheric pressure sputtering technology for 3D chip interconnection, Pisa: IEEE

L. Coppola, D.H. (2007), Survey on High-Temperature Packaging Materials for SiC-Based Power Electronics Modules, Conferencia de especialistas en electrónica de potencia del IEEE

L.Y. Chen, G.W. (2013), Tecnologías de envasado para la electrónica de alta temperatura y sensores, Conferencia Conjunta sobre la tecnología de prevención de fallos de maquinaria 67a

M. Shakir, S.H. (2019), Shakir, Muhammad et al, 555-Timer y comparadores operativos a 500 ° C, IEEE Transactions on Electron Devices

P. G. Neudeck, e. a. (2008), 6H-SiC Transistor Integrated Circuits Demonstrating Prolonged Operation at 500 °C, IMAPS HiTEC

R. Zeiser, P. W. (2015), Paquete flip-chip para sensores de presión con temperaturas de funcionamiento de hasta 500 °C, AMA Conferences

El pasado mes de octubre volvió a celebrarse en Múnich la conferencia de otoño de IMAPS, tal y como informamos en el número de diciembre. También hubo otro "Premio a la mejor presentación". La decisión recayó en la presentación de Kathrin Reinhardt, del Fraunhofer IKTS de Dresde. En su presentación y en el debate posterior, impresionó al público con sus profundos conocimientos y su formulación objetiva. La presentación se preparó de forma muy clara y estructurada. Presentó un tema conocido pero recientemente revitalizado: las pastas fotoestructuradas. Esto podría llenar el vacío existente entre el proceso de serigrafía, técnicamente "sencillo", y la microestructuración, tecnológicamente compleja. La Sra. Reinhardt ha tenido la amabilidad de preparar un resumen del tema presentado para PLUS.

Pastas fotoestructuradas: las últimas innovaciones en la tecnología de película gruesa fineline

Fig. 1: Ilustración de los dos pasos adicionales del proceso: a) capa después de la serigrafía, b) exposición a la luz UV mediante una fotomáscara negativa, c) desarrollo mediante soluciones acuosas y d) estructuras desarrolladas antes de la sinterizaciónLos avancesen los campos de la comunicación móvil (5G, 6G), la movilidad (autónoma) y el Internet de las cosas (ciudades inteligentes, wearables, seguimiento de objetos, redes inteligentes, videoseguridad) son de gran actualidad en el panorama industrial y de investigación europeo. Esto requiere anchos de banda de transmisión cada vez mayores y, por tanto, frecuencias de funcionamiento cada vez más altas > 60 GHz. Para explotar este potencial, se necesitan nuevas tecnologías que generen los circuitos de alta frecuencia, con los que se pueden realizar tramos de conductores cada vez más finos con espaciamientos cada vez más estrechos en el rango de 10-30 µm cada uno. Para alcanzar este objetivo, el Fraunhofer IKTS ha desarrollado pastas de capa gruesa que pueden fotoestructurarse con luz ultravioleta y permiten alcanzar las resoluciones geométricas deseadas. La empresa DuPont - FODELTM - ya aplicó en el pasado un enfoque tecnológico similar, pero debido a la limitada variedad de materiales (oro, plata, dieléctricos) y a las insuficientes resoluciones geométricas (40 µm de anchura de línea; 50 µm de espaciado) nunca pudo llevarse a la aplicación industrial. En el campo de la comunicación inalámbrica, las pastas fotoestructuradas IKTS de nuevo desarrollo (plata, oro, platino, resistencias) representan por tanto un enorme valor añadido que, en comparación con FODEL, son además más robustas (procesamiento bajo luz blanca), más respetuosas con el proceso (tiempos de proceso muy cortos) y más respetuosas con el medio ambiente (compatibles con RoHS/REACH). Para una mejor comprensión, en la figura 1 se describe el proceso de fotoestructuración. En comparación con la tecnología convencional de película gruesa, se requieren dos pasos adicionales (exposición y revelado) para la estructuración tras la serigrafía. Estos pasos adicionales del proceso sólo requieren entre 5 y 20 segundos cada uno y pueden integrarse fácilmente en las líneas de proceso de producción establecidas. La exposición puede lograrse utilizando fotomáscaras o procesos de imagen directa láser (LDI) sin máscara. Esta nueva característica es posible gracias a la adaptación específica del aglutinante fotosensible y contribuye a la digitalización de la tecnología de proceso y a una mayor mejora de la precisión estructural.

Fig. 1: Ilustración de los dos pasos adicionales del proceso: a) capa después de la serigrafía, b) exposición a la luz UV mediante una fotomáscara negativa, c) desarrollo mediante soluciones acuosas y d) estructuras desarrolladas antes de la sinterizaciónLos avancesen los campos de la comunicación móvil (5G, 6G), la movilidad (autónoma) y el Internet de las cosas (ciudades inteligentes, wearables, seguimiento de objetos, redes inteligentes, videoseguridad) son de gran actualidad en el panorama industrial y de investigación europeo. Esto requiere anchos de banda de transmisión cada vez mayores y, por tanto, frecuencias de funcionamiento cada vez más altas > 60 GHz. Para explotar este potencial, se necesitan nuevas tecnologías que generen los circuitos de alta frecuencia, con los que se pueden realizar tramos de conductores cada vez más finos con espaciamientos cada vez más estrechos en el rango de 10-30 µm cada uno. Para alcanzar este objetivo, el Fraunhofer IKTS ha desarrollado pastas de capa gruesa que pueden fotoestructurarse con luz ultravioleta y permiten alcanzar las resoluciones geométricas deseadas. La empresa DuPont - FODELTM - ya aplicó en el pasado un enfoque tecnológico similar, pero debido a la limitada variedad de materiales (oro, plata, dieléctricos) y a las insuficientes resoluciones geométricas (40 µm de anchura de línea; 50 µm de espaciado) nunca pudo llevarse a la aplicación industrial. En el campo de la comunicación inalámbrica, las pastas fotoestructuradas IKTS de nuevo desarrollo (plata, oro, platino, resistencias) representan por tanto un enorme valor añadido que, en comparación con FODEL, son además más robustas (procesamiento bajo luz blanca), más respetuosas con el proceso (tiempos de proceso muy cortos) y más respetuosas con el medio ambiente (compatibles con RoHS/REACH). Para una mejor comprensión, en la figura 1 se describe el proceso de fotoestructuración. En comparación con la tecnología convencional de película gruesa, se requieren dos pasos adicionales (exposición y revelado) para la estructuración tras la serigrafía. Estos pasos adicionales del proceso sólo requieren entre 5 y 20 segundos cada uno y pueden integrarse fácilmente en las líneas de proceso de producción establecidas. La exposición puede lograrse utilizando fotomáscaras o procesos de imagen directa láser (LDI) sin máscara. Esta nueva característica es posible gracias a la adaptación específica del aglutinante fotosensible y contribuye a la digitalización de la tecnología de proceso y a una mayor mejora de la precisión estructural.

|

Pasta PI sobre Al2O3 |

Resistencia de la lámina1[ mOhm/sq] |

Espesor de la capa quemada [µm] |

Resolución línea / distancia [µm/µm] |

|

Plata2 (PI1101) |

≤ 3,5 |

8-12 |

20/20 |

|

Oro2 (PI2101) |

≤ 6 |

8-15 |

20/20 |

|

Platino3 (PI6101) |

≤ 40 |

6-12 |

20/30 |

|

RuO22 (W20024) |

3500 k |

11-17 |

40/35 |

1 Resistividad de la lámina, calculada para un espesor de cocción de 10±1 μm.

2 Perfil de cocción: 10 min a 850 °C

3 Perfil de cocción: 10 min a 1200 °C

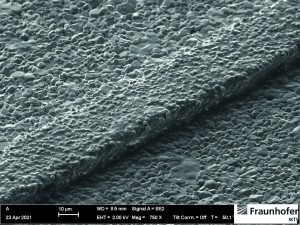

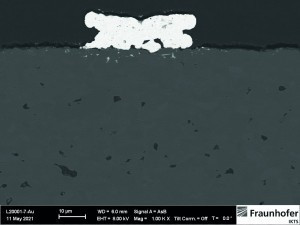

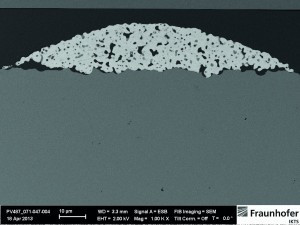

En comparación con las pistas conductoras impresas convencionalmente, las secciones transversales realizadas de las pistas conductoras tienen una forma casi rectangular, con espesores de capa sinterizada en el rango de 8-12 µm relevantes para aplicaciones de alta frecuencia(Fig. 2).

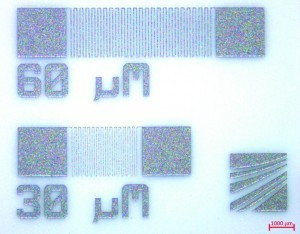

Fig. 2: Estructuras producidas en el IKTS utilizando pastas fotoestructuradas con una resolución de líneas de 60 y 30 µm, cada una separada 30 µm (arriba a la izquierda) y micrografías electrónicas del flanco del conductor sin sinterizar (20 µm) (arriba a la derecha), una sección transversal de un conductor fotoestructurado sinterizado (20 µm) (abajo a la izquierda) y producido convencionalmente (100 µm) (abajo a la derecha).

Los desarrollos actuales en pastas PI en el IKTS se centran en pastas de metalización como plata, oro, platino y cobre. Sin embargo, también se están desarrollando pastas dieléctricas y de resistencia PI. Tomando como ejemplo las pastas de plata PI, se demostró que pueden utilizarse para sustratos de óxido de aluminio, así como para cerámica de cocción a baja temperatura (LTCC). De este modo, las pastas de plata desarrolladas permiten construir LTCC tanto en el proceso de postcocción como en el de cocción. Se han conseguido anchuras de línea de 10 µm y anchuras de intersticio de 16 µm en el estado co-sinterizado. Las pruebas iniciales también han demostrado que las pastas IKTS-PI son adecuadas para la exposición directa al láser. La tabla 1 resume las propiedades de las pastas PI de plata, oro, platino y RuO2 en cuanto a resolución geométrica y conductividad eléctrica sobre sustratos de Al2O3.

Los resultados de las pastas PI del Fraunhofer IKTS muestran un prometedor proceso masivo e industrial con bajos costes de inversión y un tiempo de producción sólo ligeramente superior, que puede utilizarse para producir componentes que permitan un rendimiento de RF significativamente mejor a frecuencias más altas que antes y permitan una miniaturización significativa para el futuro.

IMAPS Alemania - Su asociación para la tecnología de ensamblaje y conexión

IMAPS Alemania, parte de la Sociedad Internacional de Microelectrónica y Embalaje (IMAPS), ha sido el foro en Alemania para todos los implicados en la microelectrónica y la tecnología de embalaje desde 1973. Con casi 300 miembros, perseguimos esencialmente tres objetivos importantes:

- conectamos la ciencia y la práctica

- garantizamos el intercambio de información entre nuestros miembros y

- representamos las opiniones de nuestros miembros en los comités internacionales.

Calendario de actos

|

Lugar |

Periodo |

Nombre del acto |

Organizador |

|

Fellbach |

2/3 marzo 2022 |

Montajes eléctricos y circuitos impresos EBL 2022 |

DVS / GMM |

|

Fountain Hills, AZ |

7-10 marzo 2022 |

Conferencia sobre embalaje de dispositivos |

IMAPS US |

|

Grenoble, FR |

10-11 marzo 2022 |

MiNaPad 2022 |

IMAPS Francia |

|

Landshut |

6 abril 2022 |

Simposio de Electrónica e Integración de Sistemas |

HS Landshut |

|

Gotemburgo, S |

12-14 de junio de 2022 |

NordPac 2022 |

IMAPS Nórdico |

|

Viena, AT |

13-15 julio 2022 |

CICMT 2022 |

IMAPS |

|

Sibiu, RO |

13-16 de septiembre de 2022 |

ESTC 2022 |

IEEE-CPMT IMAPS Europa IEEE-CPMT IMAPS Europa |

|

Berlín |

26-29 septiembre 2022 |

ESREF 2022 |

IZM / TU |

|

Boston, MA |

3-6 octubre 2022 |

Simposio internacional |

IMAPS US |

|

Munich, Alemania |

Oct. 2022 |

Conferencia de otoño |

IMAPS D |

|

Múnich, Alemania |

Nov. 2022 |

SEMICON EUROPA |

SEMI Europa |

Pie de imprenta

IMAPS Alemania e. V.

Kleingrötzing 1

D-84494 Neumarkt-St. Veit

1er Presidente:

Prof. Dr. Martin Schneider-Ramelow,

Director Adjunto del Instituto Fraunhofer de Fiabilidad y Microintegración (IZM),

Tesorero

(para cuestiones sobre afiliación y contribuciones):

Ernst G. M. Eggelaar,

Encontrará información de contacto detallada de los miembros de la Junta Directiva en www.imaps.de

(Junta Directiva)