Kurzbericht CICMT 2024 und Symposium ESI 2024

In diesem Jahr wurde die Ceramic Interconnect and Ceramic Microsystems Technologies Conference (CICMT 2024) gemeinsam mit dem 3rd Global Forum on Smart Additive Manufacturing, Design & Evaluation (Smart-MADE 2024) vom 10. bis 12. April in Osaka, Japan, ausgetragen. Durch eine Verbindung beider Konferenzen wurde auch die Breite des Themenspektrums erhöht. Um die Fokussierung trotzdem zu erreichen, sind die Nachmittagssessions für beide Teilkonferenzen parallel zueinander gelaufen. Etwas ungewöhnlich für die europäischen Teilnehmer war die Struktur der Veranstaltung: Die gemeinsamen Plenarsessions boten jeden Tag jeweils zwei Plenarvorträge und vier etwas kürzere Keynote-Präsentationen an. In den Nachmittagssessions waren die Vorträge recht straff mit 20 Minuten durchgetaktet, nicht ganz typisch war auch die relativ hohe Quote an eingeladenen Präsentationen, die bei etwa 40 % lag. Erwartungsgemäß wurde die Mehrzahl der Vorträge von Kollegen aus Japan (23), Korea (5), China (4) und Taiwan (3) gehalten, die europäische Beteiligung von 10 Präsentationen wurde von Deutschland dominiert (7).

Das Symposium Elektronik und Systemintegration (ESI 2024), das vom Cluster Mikrosystemtechnik der Hochschule Landshut organisiert und von IMAPS Deutschland unterstützt wurde, fand am 17. April statt. An der Veranstaltung mit 25 Präsentationen und 7 Postern nahmen über 90 Delegaten teil, sieben Aussteller haben ihre Produkte und Dienstleistungen vorgestellt. Den Veranstaltern wurde wieder eine hohe Qualität der Organisation bescheinigt, positiv fiel auch eine starke Beteiligung von Studierenden und Promovierenden auf.

Zur Herbstkonferenz 2023 in München stellte Rasched Sankari von der Robert Bosch GmbH sehr interessante Untersuchungsergebnisse zur Lebensdauerbetrachtung von Drahtbondverbindungen auf SiC-Leistungshalbleitern vor. Wir wollen hier die Ergebnisse einem breiteren Interessentenkreis zugänglich machen:

Lebensdauermodellierung der Oberseitenkontaktierungen von SiC-Leistungshalbleitern

Abstract

Die fortschreitende Elektrifizierung automobiler Antriebsstränge stellt neue Herausforderungen an Funktion und Zuverlässigkeit dar. Daher wird SiC als neue Generation von Leistungshalbleitern eingesetzt, die den steigenden Anforderungen gerecht wird. Mit der Etablierung hochzuverlässiger Verbindungstechnologien hat sich der Aluminium-Drahtbond für den Top-Kontakt als das schwächste Element in Bezug auf einen Ausfallmechanismus herausgestellt. Das Ziel derzeitiger Arbeiten ist es, den bisher unzureichend erforschten Kupferdrahtbond als Top-Kontakt für verkupfertes SiC zu untersuchen. Die Test-Devices werden dazu durch einen aktiven Temperaturwechseltest gestresst.

Einleitung

Die fortschreitende Elektrifizierung des Kfz stellt immer höhere Anforderungen an Funktion und Zuverlässigkeit. Ein Kernelement des elektrifizierten Antriebsstrangs sind die Leistungsmodule des Inverters. Aus der Vergangenheit sind Leistungsmodule bekannt, die in der Regel nach dem gleichen Prinzip konstruiert wurden: Die Silicium-Leistungshalbleiter werden auf ein keramisches Leistungssubstrat (DBC oder AMB) gelötet und auf der Oberseite mittels Al-Drahtbonds kontaktiert. Die Baugruppe wird dann auf eine Grundplatte oder direkt auf einen Kühler gelötet. Bei diesem Verfahren wird das gesamte Modul entweder hartvergossen, transfergemoldet oder alternativ weichvergossen. Die zuverlässigkeitsbegrenzenden Systemkomponenten sind dabei in der Regel die bleifreien Lötstellen. Mit der Etablierung hochzuverlässiger Verbindungstechnologien, wie z. B. dem Ag-Sintern, rückt seit einiger Zeit der Al-Drahtbond als ausfallbestimmendes Element in den Fokus. Der dahinterliegende Versagensmechanismus wurde vielfach in Experimenten und Simulationen untersucht [1,2,3]. Um die Zuverlässigkeit von Oberseitenkontaktierungen besonders auf SiC zu verbessern, wird von uns Kupferdrahtbonden auf kupferbeschichteten Chips vorgeschlagen. Dieses bisher wenig beschriebene Verbindungssystem wurde von uns mittels aktiven Temperaturlastwechseltests untersucht.

Testaufbauten

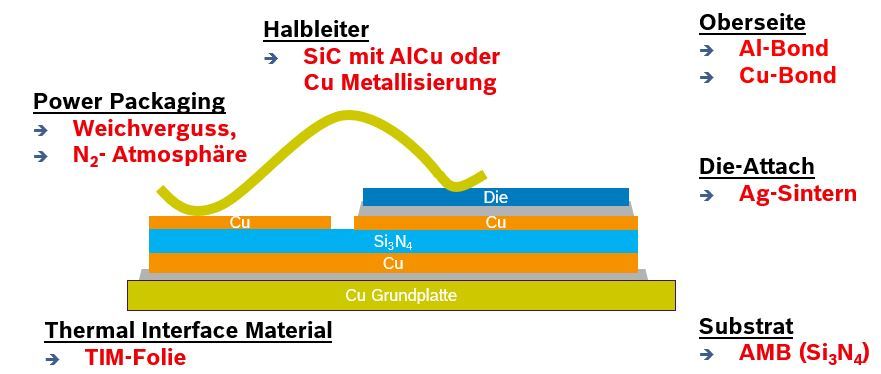

Um sicherzustellen, dass die Wechselwirkung zwischen Bonddraht und Metallisierung unbeeinflusst von Schädigungen in anderen Teilen des Aufbaus untersucht werden kann, wird eine robuste Verbindungstechnik unterhalb des Chips benötigt. Das hier vorgestellte Test-Device erfüllt diesen Anspruch und ist an aktuelle Produktdesigns angelehnt. Der in Abbildung 1 gezeigte Aufbau besteht aus einem Chip, der mittels Silbersintern mit der AMB verbunden wird. Diese besteht aus einem Stack von Kupferschichten und einer Si3N4 Keramik. Für die Oberseitenkontaktierung werden 300 µm dicke Bonddrähte aus Aluminium und Kupfer eingesetzt. Die AMB wird auf eine Cu-Grundplatte gelötet. Um Oxidation während der Tests einzuschränken, werden die Chips mit Silikon weichvergossen oder lokal mit einer N2-Atmosphäre geschützt. Die Setups in Abbildung 2 zeigen zwei unterschiedliche Aufbauvarianten. Im linken Aufbau ist ein Chip mit 4 µm gesputterter AlCu-Metallisierung und Al-Drahtbonds zu sehen. Das rechte Bild zeigt einen SiC-Chip mit dickerer galvanisch abgeschiedener Cu-Metallisierung und Cu-Bonddrähten.

Abb.1: Allgemeiner Aufbau der Messproben

Abb.1: Allgemeiner Aufbau der Messproben

Abb. 2: Aufbau der Test-Devices, mit 4 μm gesputtertem AlCu (links) und 30 μm galvanisch abgeschiedenem Cu (rechts)

Abb. 2: Aufbau der Test-Devices, mit 4 μm gesputtertem AlCu (links) und 30 μm galvanisch abgeschiedenem Cu (rechts)

Active Power Cycling (APC)

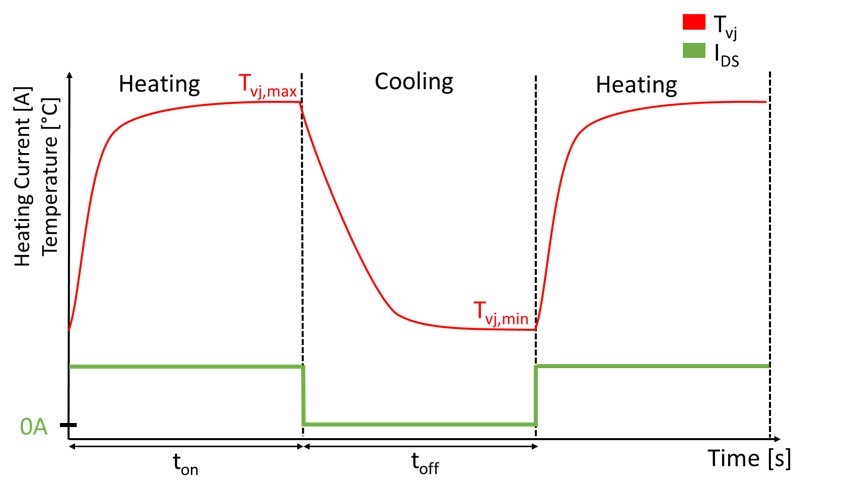

Abbildung 3 zeigt das Schema eines APC. Die Test-Devices werden zunächst durch das Anlegen eines aktiven Laststroms auf die gewünschte maximale Temperatur erwärmt. Nach Abschalten des Laststroms kühlt der Aufbau wieder auf die Temperatur des Kühlkörpers ab. Dieser Vorgang wird zyklisch wiederholt, was zu einer thermomechanischen Belastung des Aufbaus führt.

Abb. 3: Active Power Cycling Test in Abhängigkeit seiner Parameter und dem Darstellen des Temperaturhubes

Abb. 3: Active Power Cycling Test in Abhängigkeit seiner Parameter und dem Darstellen des Temperaturhubes

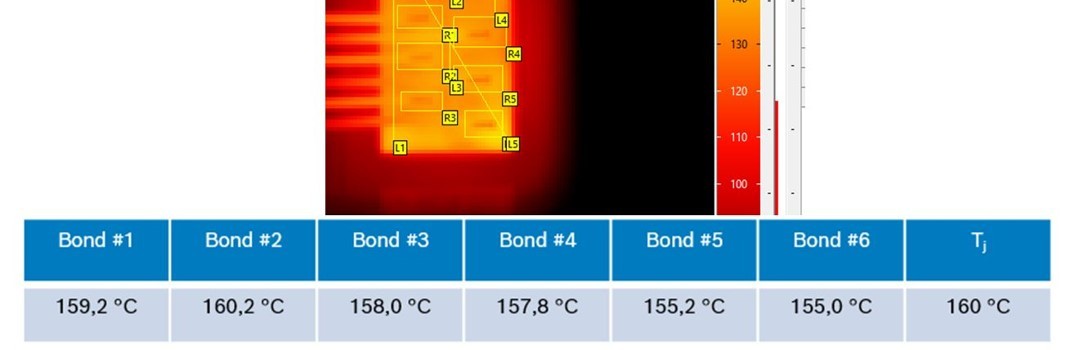

Die Degradation der Verbindungsstellen im Modul geht dabei immer mit Änderungen der elektrischen Parameter einher. Nach [4,5] wird das Versagen während des APC durch eine Erhöhung der Drain-Source Spannung Uds um 5 % bzw. des thermischen Widerstandes Rth um 20 % definiert. Um die Temperaturverteilung auf der Chipoberfläche während des APC sichtbar zu machen, wurden Infrarotmessungen durchgeführt. Durch die Messung in Abbildung 4 wird deutlich, dass auf dem SiC-Chip eine leicht inhomogene Temperaturverteilung herrscht. Es besteht ein Temperaturunterschied von bis zu 5 K zwischen den einzelnen Bondfüßen. Dies kann bei der Bewertung der Ausfallmechanismen berücksichtigt werden.

Abb. 4: APC - IR Messung bei 80 K Hub bei 80 °C Kühlkörpertemperatur von den Bondfüßen im Vergleich zur virtuell gemittelten Tj

Abb. 4: APC - IR Messung bei 80 K Hub bei 80 °C Kühlkörpertemperatur von den Bondfüßen im Vergleich zur virtuell gemittelten Tj

Untersuchungsmethodik

Die Cu Aufbau- und Verbindungstechnik (AVT) neigt dazu, leicht zu oxidieren. Um den Oxidationseinfluss zu verringern oder zu eliminieren, wird auf einen Silikonweichverguss oder das Anlegen einer lokalen N2-Atmosphäre zurückgegriffen. Es wurde ein spezielles Silikon verwendet, welches mit den hohen Anforderungen im APC kompatibel ist. Die lokale N2-Atmosphäre wurde mittels eines additiv gefertigten Kappensystems umgesetzt. Durch Letzteres werden oxidationsfreie Cu-Oberflächen im APC erreicht.

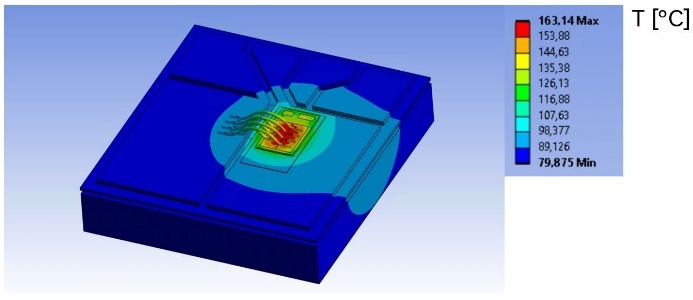

Abb. 6: Gerechnetes Temperaturfeld bei t=3s mit ΔT=80 K

Abb. 6: Gerechnetes Temperaturfeld bei t=3s mit ΔT=80 K

Ergebnisse und Diskussion

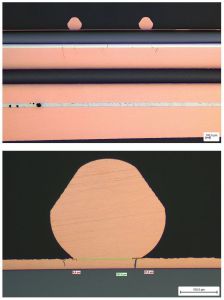

Abb. 5: Schliffe eines erprobten SiC-Cu mit ΔT=150 K nach 51.000 ZyklenDie Module mit Al-Wirebonds zeigten nach APC mit ΔT 130 K einen klassischen Lift-Off nach 32.000 Zyklen. Der Riss verlief entlang der Zone zwischen den Bondfüßen und der Metallisierung. Dieses Fehlerbild ist so aus der Literatur bekannt [6]. Bei den Modulen mit Cu-AVT zeigt sich ein anderes Fehlerbild. Es konnten Schädigungen in Form von senkrechten Rissen in der Zone Bondfuß-Metallisierung beobachtet werden, wie in der Abbildung 5 dargestellt. Die senkrechten Risse an der Oberseite provozieren dabei aber selbst nach mehr als 51.000 Zyklen bei ΔT 150 K zunächst keinen elektrischen Ausfall. Der genaue Zusammenhang zwischen Ausfallbild und Schädigung wird derzeit detaillierter untersucht. Eine parallel laufende thermomechanische Simulation dient der Unterstützung der experimentell ermittelten Lebensdauerdaten aus dem APC. Zunächst wird die thermische Situation im Aufbau simuliert, wie in der Abbildung 6 dargestellt. Diese thermische Last wird dann als Randbedingung in die statische thermomechanische Berechnung eingespielt.

Abb. 5: Schliffe eines erprobten SiC-Cu mit ΔT=150 K nach 51.000 ZyklenDie Module mit Al-Wirebonds zeigten nach APC mit ΔT 130 K einen klassischen Lift-Off nach 32.000 Zyklen. Der Riss verlief entlang der Zone zwischen den Bondfüßen und der Metallisierung. Dieses Fehlerbild ist so aus der Literatur bekannt [6]. Bei den Modulen mit Cu-AVT zeigt sich ein anderes Fehlerbild. Es konnten Schädigungen in Form von senkrechten Rissen in der Zone Bondfuß-Metallisierung beobachtet werden, wie in der Abbildung 5 dargestellt. Die senkrechten Risse an der Oberseite provozieren dabei aber selbst nach mehr als 51.000 Zyklen bei ΔT 150 K zunächst keinen elektrischen Ausfall. Der genaue Zusammenhang zwischen Ausfallbild und Schädigung wird derzeit detaillierter untersucht. Eine parallel laufende thermomechanische Simulation dient der Unterstützung der experimentell ermittelten Lebensdauerdaten aus dem APC. Zunächst wird die thermische Situation im Aufbau simuliert, wie in der Abbildung 6 dargestellt. Diese thermische Last wird dann als Randbedingung in die statische thermomechanische Berechnung eingespielt.

Zusammenfassung

In dieser Arbeit wurde das Degradationsphänomen von 300 µm dicken Al- und Cu-Drahtbonds auf SiC-Leistungshalbleitern mit AlCu- und Cu-Metallisierungen im APC untersucht. Im ersten Schritt wurde die Temperaturverteilung auf der SiC-Oberfläche während des Tests untersucht. Für die oxidationsfreie Erprobung der SiC-Module mit Cu-AVT wurde eine Oxidschutzkammer entwickelt. Die Untersuchung der Al-AVT zeigt ein Standardversagen durch klassisches Lift-Off der Bondfüße im Interface. Als neues Fehlerbild bei der Cu-AVT auf SiC traten vertikale Risse auf. Derzeit wird untersucht, wie diese Risse zum Versagen von Modulen führen können.

Danksagung

Teile dieser Arbeit werden durch das H2020 KDT JU-Programm der Europäischen Union unterstützt im Rahmen des TRANSFORM-Projekts „Trusted European SiC Value Chain for a greener Economy“ - KDT-Stipendium Nr. 101007237 - und dem Bundesministerium für Bildung und Forschung Förderkennzeichen 16MEE0127K. Die Autoren bedanken sich bei allen unterstützenden Institutionen und allen Transform-Projektpartnern.

Veranstaltungskalender

|

Ort |

Zeitraum |

Name |

Veranstalter |

|

Berlin |

11. - 13. September 2024 |

Electronics System-Integration Technology Conference (ESTC) |

IEEE, IMAPS |

|

Boston, USA |

30. Sept. - 3. Okt. 2024 |

57th International Symposium on Microelectronics |

IMAPS USA |

|

München |

17./18. Oktober 2024 |

Herbstkonferenz |

IMAPS DE |

|

Tours, Frankreich |

28. November 2024 |

Power Electronics and Packaging European Workshop |

IMAPS France |

|

Phoenix, USA |

3. - 6. März 2025 |

Device Packaging Conference |

IMAPS USA |

IMAPS Deutschland – Ihre Vereinigung für Aufbau- und Verbindungstechnik

IMAPS Deutschland, Teil der ‚International Microelectronics and Packaging Society' (IMAPS), stellt seit 1973 in Deutschland das Forum für alle, die sich mit Mikroelektronik und Aufbau- und Verbindungstechnik beschäftigen, dar. Mit fast 300 Mitgliedern verfolgen wir im Wesentlichen drei wichtige Ziele:

- wir verbinden Wissenschaft und Praxis

- wir sorgen für den Informationsaustausch unter unseren Mitgliedern und

- wir vertreten den Standpunkt unserer Mitglieder in internationalen Gremien.

Impressum

IMAPS Deutschland e. V.

Kleingrötzing 1, D-84494 Neumarkt-St. Veit

1. Vorsitzender: Prof. Dr.-Ing. Martin Schneider-Ramelow, Institutsleiter Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration (IZM),

Schatzmeister

(bei Fragen zu Mitgliedschaft und Beitrag):

Ernst G. M. Eggelaar,

Ausführliche Kontaktinformationen zu den Vorstandsmitgliedern finden Sie unter www.imaps.de

(Vorstand)

Quellen

[1] M.S. Broll and U. Geissler and J. Höfer and S. Schmitz and O. Wittler and M. Schneider-Ramelow and K.D. Lang, “Correlation between mechanical properties and microstructure of different aluminum wire qualities after ultrasonic bonding”, in Microelectronics Reliability, 55 (2015) 1855-1860

[2] U. Geissler and M. Schneider-Ramelow and H. Reichl, “Hardening and softening in AlSi1 bond contacts during ultrasonic wire bonding”, in IEEE Trans. Compon. Packag. Technol., 32 (4) (2009) 794-799

[3] M. Schneider-Ramelow and C. Ehrhardt, “The reliability of wire bonding using Ag and Al”, in Microelectronics Reliability, 63 (2016) 336-341

[4] J. Lutz and T. Herrmann and M. Feller and R. Bayerer and T. Licht, “Power cycling induced failure mechanisms in the viewpoint of rough temperature environment”, in European Conference on Power Electronics and Applications (2007)

[5] M. Held and P. Jacob and G. Nicoletti and P. Scacco and M. -. Poech, “Fast power cycling test of IGBT modules in traction application”, in Proceedings of Second International Conference on Power Electronics and Drive Systems (1997)

[6] J. Goehre and M. Schneider-Ramelow and U. Geissler and K.D. Lang, “Interface Degradation of Al Heavy Wire Bonds on Power Semiconductors during Active Power Cycling measured by the Shear Test”, in CIPS (2010), Paper 3.4