Silvaco, ein US-amerikanischer Entwickler von TCAD-, EDA- und SIP-Software, hat eine strategische F&E-Zusammenarbeit mit dem Fraunhofer-Institut für Siliciumtechnologie ISIT in Itzehoe bekannt gegeben. Ziel ist die beschleunigte Entwicklung von Galliumnitrid-Bauelementen.

Das amerikanische Unternehmen mit Hauptsitz in Santa Clara, Kalifornien (USA), und mehreren internationalen Standorten bietet mit seinen Lösungen für das Halbleiterdesign u. a. die Modellierung des digitalen Zwillings durch KI-Software. Das Itzehoer Fraunhofer ISIT wiederum entwickelt und fertigt kundenspezifische Komponenten für die Leistungselektronik und Mikrosystemtechnik.

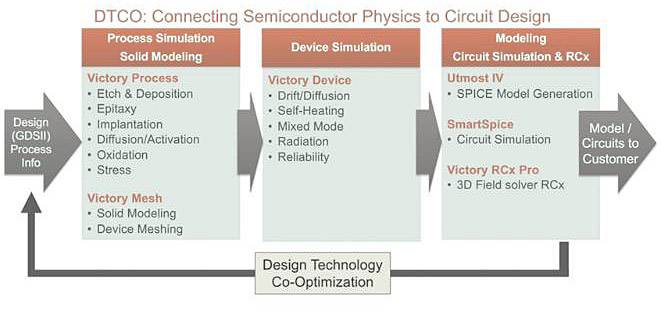

Erklärtes Ziel der Partnerschaft ist die beschleunigte Entwicklung von Galliumnitrid-Bauelementen (GaN) der nächsten Generation. Fraunhofer ISIT wird Designtools von Silvaco – darunter die Victory TCAD-Plattform, Utmost IV und SmartSpice – nutzen, um die Design Technology Co-Optimization (DTCO) für die Entwicklung von Leistungs- und Sensorgeräten durchzuführen. Die DTCO-Plattform ermöglicht schnelleres Prototyping in der Post-CMOS-Prozessumgebung des Fraunhofer ISIT. Sie wurde für die Erforschung neuer Prozesse für GaN- und MEMS-Technologien auf 8″-Wafern eingerichtet.

DTCO-Optimierungsfluss am Fraunhofer ISIT unter Verwendung der Silvaco-Tools

DTCO-Optimierungsfluss am Fraunhofer ISIT unter Verwendung der Silvaco-Tools

Vom Einsatz der TCAD-Lösungen von Silvaco erhofft sich Fraunhofer ISIT, die Leistung von GaN-Bauelementen mit größerer Tiefe und Effizienz untersuchen, verstehen und optimieren zu können. Insbesondere bei der Entwicklung lateraler und vertikaler Hochspannungs-GaN-Bauelemente, die auf technischen Substraten wie der Qromis Substrate Technology basieren, sieht man physikalische Effekte, die genau kalibrierte Prozess- und Bauelementmodelle erfordern.

Neben der Nutzung der Silvaco-Tools in F&E- und Industriekundenprojekten wird das Fraunhofer ISIT Studenten an lokalen Universitäten in der Nutzung der Victory TCAD-Plattform schulen, um die kommende Generation Halbleiterbauelement-Ingenieure zu unterstützen.

Post-CMOS-Reinraum am Fraunhofer ISIT für die Entwicklung von GaN- und MEMS-Bauelementen

Post-CMOS-Reinraum am Fraunhofer ISIT für die Entwicklung von GaN- und MEMS-Bauelementen