Ein 2024 erschienenes Buch von John H. Lau, Unimicron Technology Taiwan, verdeutlicht die Anforderungen an das Packaging im technologischen Umfeld des Aufbaus von elektronischen Komponenten und Modulen.

Auf 491 Seiten werden von John Lau in Theorie und Praxis Studien in Design, Material, Prozessen, Herstellung und Zuverlässigkeit einer Variantenvielfalt der Aufbau- und Verbindungstechnik vorgestellt. Das Buch behandelt wesentliche Schwerpunkte des Packagings und nimmt dabei Design, Materialien, Prozesse, Herstellung und Zuverlässigkeit der Flip-Chip-Technologie, des Hybrid-Bondings und der Fan-In- und Fan-Out-Technologie in den Blick. Prinzipien und Aufbau- und Verbindungstechnik (AVT), werden behandelt, mit stärkerem Gewicht auf der AVT. Ausführlich stellt John Lau Studien vor, die folgende Aspekte vertiefen: Wafer Bumping, Flip-Chip-Technologie, Underfill und Zuverlässigkeit, Chip-to-Wafer, Wafer-to-Wafer, Hybrid Bonding, WLCSP, 6-side gemoldeten WLCSP, FOWLP auf hybriden Substraten mit PID, ABF und großen organischen Interposern, die Kommunikation zwischen Chiplets und AVT-heterogener Integration, On-board-Optics, Near-package-Optics und Co-packaged-Optics.

Flip-Chip-Technologie

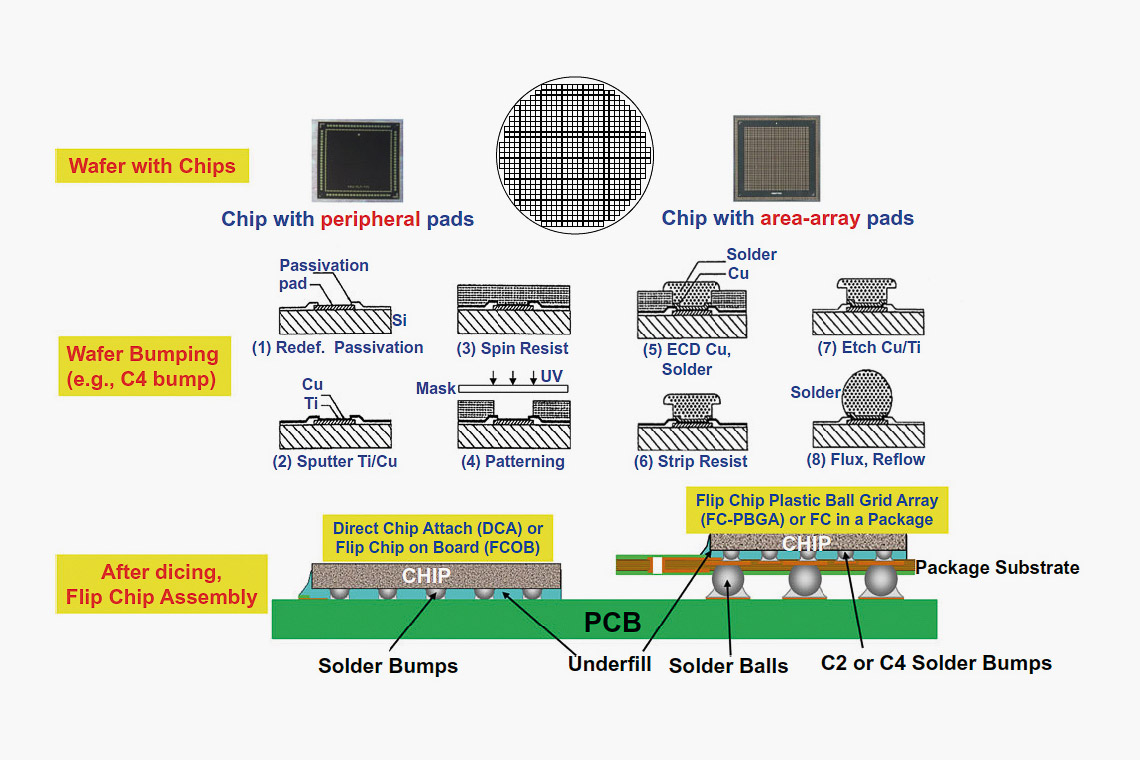

Ausführlich bechreibt John Lau die Flip-Chip-Technologie, Cu-Cu-Hybrid-Bonden, die Fan-In- und die Fan-Out-Technologie, die Chiplet-Kommunikation (Bridges) und die Co-packaged-Optics. Die Flip-Chip-Technologie (FC) wird im Prozess-Flow unterteilt mit Direkt-Chip-Attach (DCA) oder Flip Chip auf BGA-Substraten für die Leiterplattenmontage. Weiterführend wird die FC-Technologie definiert über die Montage auf keramischen, organischen und Silicium-Substraten. Als eine Grundvoraussetzung wird das Wafer Bumping über Stencil Printing diskutiert. Lau nennt wesentliche Einflussfaktoren für das Solder Paste Printing (Operator, Environment, Print Parameter, Drucker, Schablone, Wafer, Rakel und Lotpaste) und Kontrollfaktoren (Taguchi DOE für L8- und L4-Experimente mit Bestimmung des Lotvolumens). Das Solder-Bump-Volumen im Array wird mittels Taguchi-Analyse mit Hauptfaktoren (Analysis of Variance, ANOVA) bestimmt. Vorgestellt wird auch das Wafer Bumping mittels Electroplating, und das Wafer Bumping durch ECD oder Electroplating-Methoden für C4-Bumps werden verglichen durch Cu mit C4-Bumps und C2-Bumps (Cu Pillar und Solder Cap).

Nachfolgend stellt John Lau Flip-Chip-Substrate (Printed Cicuit Board, Built-Up Package Substrates , Coreless Package Substrate, Bond on Lead, Embedded Trace Substrates, Thin Film Layers auf Build-Up Package Substraten) vor. Besprochen werden auch FC-Package-Substrate, Fan-Out EMC/RDL, active und passive TSV-Interposer, FC-Packages-Si-Bridge, embedded in organischen Substraten, und FC-Package-Substrate -Si Bridge, embedded in Fan-Out EMC mit RDL. Auch stellt John Lau die Flip-Chip-Assembly vor. Die Kontaktierung über Cu-Cu TCB Direkt Bonding, Cu-to-Cu Room Temperatur Direkt (Hybrid) Bonding, C4 Solder Reflow mit Underfill, C2 Solder Reflow mit Underfill, TCB mit niedriger Bondkraft und Underfill sowie C2 TCB mit hoher Bondkraft (NCP und NCF) ergänzen die Bondverfahren. Anschließend werden Materialien und Applikationen aufgelistet und die Zuverlässigkeit analysiert.

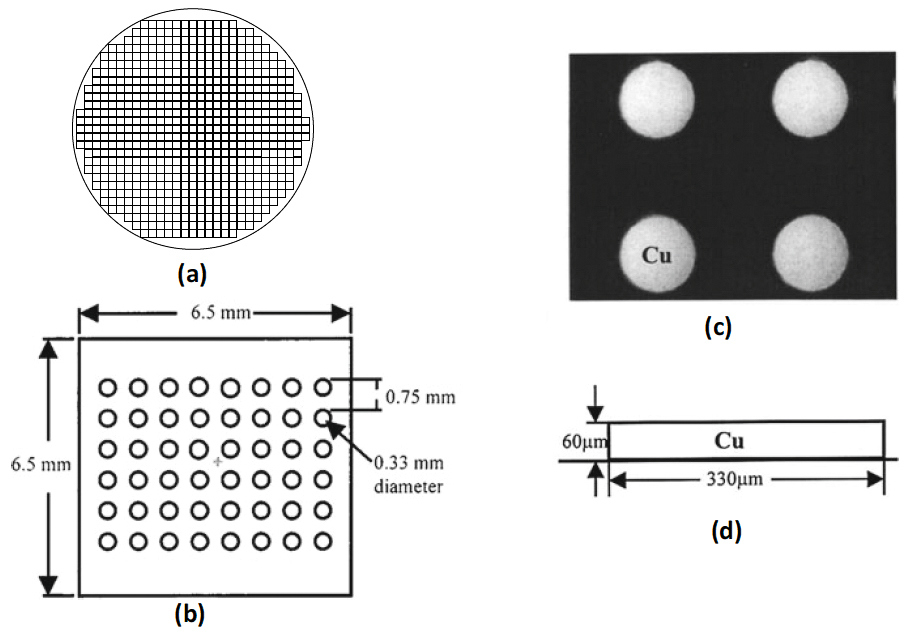

Abb. 2:

Abb. 2:

a: Das Layout eines 200-mm-Wafers

b: Chip – und Padabmessungen sowie Abstand

c: Kupferpads –

d: Geometrie der Kupferpads

Hybrid Bonding

Hybrid Bonding hat vor Kurzem stark an Bedeutung zugenommen. Im zweiten Kapitel wird es technologisch und verfahrenstechnisch vorgestellt und u. a. basierend auf der ECTC 2023 mit insgesamt 80 Papers referenziert. Das Bumpless-Hybrid-Bonding wird auch als Direkt-Bond-Interconnect (DBI) bezeichnet. 2000 wurde es durch das Research Triangle Institut in den USA patentiert. Das DBI ist in hochvolumiger Fertigung bei Sony seit 2026 und seit 2021 bei Yangtze Memory Technology in der Anwendung.

Nachfolgend wird das State-of-the-Art Cu-Cu bumpless Hybrid Bonding beschrieben und Samsungs Hybrid Bonding als Multi-stack-Hybrid-Cu-Bonding-(HCB)-Technologie präsentiert, wobei die 16H-Multi-Stack-Methode durch Flip-Chip-TCB-Solder-Reflow gekennzeichnet ist. Hybrid Bonding kann als D2D (Die to Die), D2W (Die to Wafer) und W2W (Wafer to Wafer) ausgeführt werden. Das Hybrid-Cu-Bonding (HCB) wird mit Bumpless-Chips und Cu auf Cu-Pads gebondet. Die Package-Höhe ist kleiner als die mit TCB und gebumpten Flip Chips und ohne Spalten zwischen den Chips (gapless). Der HCB-Mechanismus wird nach dem CMP (chemisch-mechanisches Polieren) gestartet. CMP wird durchgeführt für Bondoberflächen z. B. eines Memory-Dies nach dem Dicing und dem Puffer-Wafer. Die erarbeitete Rauheit ist entscheidend für die Annäherung der Cu-Oberflächen und die zu erwartende Anpassung der Oberflächen.

Nach dem Pre-Bonding mit kompletten Stacks wird die Verbindung zwischen den Oxiden durch ein Hochtemperatur-Annealing verstärkt. Die Cu-Pads des Top- und Bottom-Chips expandieren und formen eine elektrische Verbindung nach der Diffusion. Eine Herausforderung des HCBs ist das thermische Management. Weil keine Gaps zwischen den Chips sind, ist der vertikale thermische Widerstand geringer als bei der Flip-Chip-Variante mit Gaps zwischen den Mikrobumps. Ein Vergleich der Technologien und Ausführungen verschiedener Wettbewerber schließt sich an (Samsung, SK Hynix, Micron, Mitsui, Sony, CEA-Leti, TEL, Applied Materials, Intel, TSMC, MKS, Resonac, Adeia, TU Dresden, EVG, Ieme, UCLA). Die zeigt, mit welcher Spannweite das HCB weiterentwickelt und evaluiert wird.

Fan-In Technologie

Im dritten Kapitel werden Vor- und Nachteile der Fan-In-Technologie (WLCSP) diskutiert. Die Besonderheit der meisten WLCSP ist die Verwendung metallischer (meistens Cu) RDL (Redistribution Layer), um die Fine-Pitch-peripher angeordneten Pads der Chips auf dem Wafer mit viel größeren Pitches flächig angeordneter Pads zu verbinden. Kriecheigenschaften von Pb-freien WLCSP sind begleitet von Strukturanalysen, der Kennzeichnung der Materialeigenschaften, der Grenzflächeneigenschaften, Dehnungen und Stressanalysen, der zyklischen Alterungseigenschaften, des zeitabhängigen Scherstresses und der zeitabhängigen Kriechdehnung der Anschlussstrukturen.

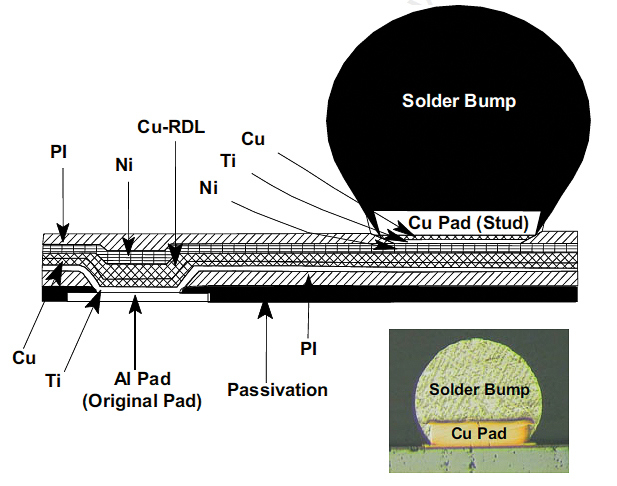

Abb. 3: Fan-In der ursprünglichen peripheren Pads

Abb. 3: Fan-In der ursprünglichen peripheren Pads

Fan-Out-Technologie

Im vierten Kapitel wird die Fan-Out-Technologie besprochen. Die Verwendung einer RDL in Fan-Out bringt die Schaltung vom Metal Pad auf dem Chip, auf dem Wafer und den Solder-Balls zu den Metal-Pads auf der Leiterplatte (eWLB). Die Vorteile von FOWLP im Vergleich zu PBGA mit einem Solder-Bumped-Flip-Chip sind geringere Kosten, Lower-Package-Profil, Beseitigung des Substrates, Beseitigung des Wafer Bumpings, Beseitigung des Flip-Chip-Reflows, Beseitigung des Underfills, bessere elektrische Performance, bessere thermische Performance, der leichtere Weg zu System-in-Package und 3D-IC-Packaging sowie höhere Board-Level-Reliability. Grundsätzlich gibt es zwei Möglichkeiten für einen FOWLP: Chip-First oder Chip-Last. Für die Chip-First-Methode gibt es wiederum zwei Möglichkeiten: Face-Down (Die Down) und Face-Up (Die Up). Die Chip-Last-Methode (RDL first) lässt nur Die-Face-Down zu.

Bridges

John H. Lau, ‚Flip Chip, Hybrid Bonding, Fan-In, and Fan-Out Technology‘,

John H. Lau, ‚Flip Chip, Hybrid Bonding, Fan-In, and Fan-Out Technology‘,

Springer Nature Scientific Publishing Services,

Singapur 2024

ISBN 978-981-97-2139-9.Im fünften Kapitel wird die Chiplet-Kommunikation (Bridges) besprochen. Wichtigster Unterschied zwischen Chiplet und heterogener Integration ist, dass das Chiplet eine Chipdesignmethode ist, während die heterogene Integration eine Chip-Packaging-Methode ist. Dort gibt es mindestens fünf verschiedene Chiplet Designs und heterogene Integration:

- Chip-Partitionierung und heterogene Integration (getrieben durch Kosten und Technologie-Optimierung

- Chip-Split und heterogene Integration (getrieben durch Kosten and Semiconductor Herstellungsausbeute)

- Multiple Systeme und heterogene Integration mit Dünnfilmtechnik direkt on top der Build-up-Package-Substrate (2.1D IC Integration)

- Multiple Systeme und heterogene Integration mit TSV-freien Interposern (2.3D IC Integration)

- Multiple Systeme und heterogene Integration mit TSV-Interposern (2.5D- und 3D-IC-Integration)

Weiterhin werden die Themen Hybrid Bonding Bridge mit C4-Bumps auf dem Package Substrate und dem Chiplet Wafer, Ridge Bridge Embedded in Fan-Out EMC mit RDLs, der Bridge-First und Face-Up-Prozess von Applied Material, der Bridge-First und Face-Down-Prozess von Unimicron und der Bridge-Last-Prozess von IME behandelt.

Packaging Technology getrieben durch künstliche Intelligence (AI)

Eine der populärsten Advanced-Packaging-Technologien ist die 2.5D- oder 3D-integrierte Circuit-Integration. Die zentrale Recheneinheit (CPU), die Grafikverarbeitungseinheit (GPU) und die hohe Bandbreiten-Memory werden unterstützt durch passive (2.5D) oder aktive (3D) Through-Silicon-Vias (TSV)-Interposer auf einem Build-Up-Package-Substrat. Final ist das gesamte Modul auf einer Leiterplatte mit Ball-Grid-Array (BGA), Solder-Balls und Solder-Paste befestigt. Dieses multiple Chiplet-System und heterogen-integrierte Package wird getrieben durch hohe Leistung und den Formfaktor. Ausgelegt ist es für extrem hochdichte HP-Applikationen. Das erste Paper zur 2.5D-IC-Integration wurde durch CEA-Leti auf der IEEE/ECTC 2005 und auf der IEEE/ECTC 2006 veröffentlicht. Das erste Product (Virtex-7 HT Family) der 2.5D wurde 2013 von Xilinx und TSMC geliefert. AMD vertrieb die Radeon-R9-FuryX-GPU, Nvidia die Pascal-100-GPU, Fujitsu das Fugaku (A64FX CPU) und Graphcore die Bow (eine intelligente Prozesssorunit). Kürzlich lieferte Nvidia seine A100 GPU (826 mm2) mit sechs HBM2 und TSV-Interposern und die H100 GPU für KI-Applikationen.

Co-packaged-Optics

Co-packaged-Optics (CPO) sind heterogen integrierte Packaging-Methoden der optischen Engine (OE), welche aus einem Photonic-IC (PIC) und der elektrischen Engine (EE) bestehen, und diese wiederum aus dem elektronischen IC (EIC) und dem ASIC. Silicon Photonics ist die Integration von EIC und PIC auf dem Silicon Substrate (Wafer) mit komplementärer CMOS-Technologie. Die Anwendungen liegen u. a. bei Data-Centern und verschiedenen heterogenen Integrationen, die Lau umfassend behandelt.

Fazit

Insgesamt ist John H. Laus Buch ein hervorragendes Nachschlagewerk für Prozesse und Technologien der fortgeschrittenen Bauelemente- und Modulmontage im Bereich der Ingenieurwissenschaften und für Studierende im Bereich Packaging und der Baugruppentechnologie. Jedes Kapitel ist mit einer umfangreichen Literatursammlung verbunden.