Die ECTC 2025 in Dallas, Texas (USA), positionierte Ende Mai Advanced Substrates als Schlüssel zur KI-Skalierung und führte die Diskussion über die Zukunft der Trägersysteme für Hochleistungselektronik.

Auf der weltweit bedeutendsten Konferenz für Packaging-Technologien, die vom 27.-30. Mai 2025 im Gaylord Texan Resort & Convention Center von Dallas stattfand, rückten Advanced Substrates in den Mittelpunkt eines Branchendialogs. Mit über 2.500 Teilnehmern, einer ausgebuchten Ausstellung mit 138 Ständen und elf Sonderpanels zeigte sich, dass die Wahl des Substrats zum Taktgeber für die nächste Generation hochintegrierter Systeme geworden ist [1].

Technologische Weichenstellung bei Glas- und RDL-Substraten

Im Zentrum des Interesses stand die Sonderveranstaltung ‚Glass Core vs. RDL Interposer Substrates: Ready for Prime-Time?', die mit über 350 Zuhörern bis auf den letzten Platz besetzt war [1, 2]. Experten von Samsung, Intel, TSMC, AMD, FICT, Toppan sowie Zeiss und Yield Engineering Systems beleuchteten die unterschiedlichen Entwicklungslinien der beiden dominierenden Substratkonzepte [1, 2].

Während RDL-basierte Interposer bereits in Volumenproduktion sind und sich in AI-Inferencing, Netzwerk-Switches oder Edge-Systemen bewährt haben, treiben Forschungseinrichtungen und Industrieakteure wie Imec, Fraunhofer IZM oder Toppan den Übergang zu Glass-Core-Substraten voran [2, 5]. Entscheidend sind hierbei Parameter wie Dimensionsstabilität bei hohen Temperaturen, geringe elektrische Verluste, definierte Warpage-Eigenschaften sowie der zunehmende Bedarf an planaren Trägern für Co-Packaged Optics und Chiplet-Architekturen [1]. Samsung präsentierte die Fortschritte bei der Integration laserstrukturierter Through-Glass-Vias (TGVs) in 800µm dicken Glaskernen mit acht Layern und 80 × 80 mm Kantenlänge [1]. Für das laufende Jahr ist ein Package im Format 105 × 105 mm mit 840 µm Dicke in der Validierung, das bis Ende 2027 in Serienfertigung überführt werden soll. Intel zeigte seine TGV-Technologie mit einem Aspect Ratio von 1:20 auf Glas, ergänzt durch den Aufruf, ein robustes Ökosystem für Glass Packages zu etablieren [1]. Toppan und FICT stellten Lösungsansätze zur Stressreduktion und thermomechanischen Entkopplung im Stack vor [1]. TSMC verwies auf ihre hohe Yield-Stabilität bei RDL-Packages mit bis zu elf Layern und die Skalierbarkeit ihres CoWoS-R-Stacks, sowohl für High Performance Computing als auch bei Edge Devices [1]. AMD bestätigte zudem die Eignung von Glaspanels für großflächige, verzugsarme Trägerlösungen [1].

Glas gewinnt Funktionstiefe

Parallel zur Paneldiskussion lieferte Imec mit der Demonstration einer 300-mm-RF-Interposerplattform auf Silicium einen zentralen Impuls [5]. Die Kombination aus CMOS- und III/V-Chiplets auf einem Träger mit nur 0,73dB/mm Einfügedämpfung bei bis zu 325GHz adressiert Anwendungen in Rechenzentrumsfunk, Sub-THz-Kurzstrecken oder optischen Transceivern [5]. Die Plattform nutzt Cu-Damascene-BEOL für die digitalen Leitungsnetze, ergänzt um mmWave-Pfade auf RF-Polymer, und integriert passive Bauteile direkt in das Substrat [5]. Die Struktur erlaubt 40µm Flip-Chip-Pitch und soll in einem nächsten Schritt auf 20µm skaliert werden [5].

Neben der Entwicklung glasbasierter Substrate für RF-Integration zeigten mehrere Beiträge, dass die Mechanik des Glases selbst optimierbar ist: Mit gezieltem Stress Engineering, lithografischen Adjustments und Backside Redistribution Layers (RDL) lassen sich nicht nur CTE-Profile anpassen, sondern auch Packaging-Herausforderungen wie Die-Ausrichtung, Warpage oder Layer-to-Layer-Kopplung adressieren. In Summe entsteht eine Materialklasse, die sich zunehmend vom optischen Träger zum funktionalen Interposer weiterentwickelt.

Thermomanagement und Strompfade auf der Rückseite

Ein weiteres Highlight der ECTC war die Session zur Rückseiten-Stromversorgung (Backside Power Delivery, BPD), bei der IBM, imec, Georgia Tech und Purdue neue Konzepte zur Integration von Mikrokanälen, TSVs und eingebetteten Heatspreadern vorstellten [1]. Die zentralen Herausforderungen lagen in der Thermal Resistance bei 3D-Architekturen und im Verhalten komplexer Heatmaps bei unterschiedlichen Packaging-Tiefen [1]. Glas wurde mehrfach als geeignetes Substrat für den thermomechanischen Basisträger genannt, insbesondere im Hinblick auf hochpräzise Strukturierbarkeit, planare Via-Geometrien und die Möglichkeit zur Kombination mit Kupfer-Microbumps oder diamantbasierten Kühlstrukturen [1].

Das Koh Young-Team auf der ECTC (v.l.n.r.): JD Shin, Brent Fischthal, Allen Phung und Joel Scutchfield

Das Koh Young-Team auf der ECTC (v.l.n.r.): JD Shin, Brent Fischthal, Allen Phung und Joel Scutchfield

Koh Young: Inline-Metrologie als Schlüssel zur Substratqualität

Mit True3D und KI-gestützter Fehlerklassifikation adressierte das Unternehmen Koh Young das Problem der Warpage-Kontrolle und Fehlerdetektion in der Mehrlagenstruktur von Glassubstraten [3]. Die vorgestellten Systeme ermöglichen eine lückenlose Inline-Erfassung von Planarität, Mikrorissen, Lotvolumen oder Via-Füllungen – wichtige Parameter, um bei niedrigen Fehlertoleranzen eine hohe Yield-Quote im Advanced Packaging zu sichern [3]. Koh Young trat nicht nur als exklusiver Sponsor des Galaabends auf, sondern stellte am eigenen Messestand konkrete Closed-Loop-Lösungen zur Prozessregelung und Substratvalidierung vor [3].

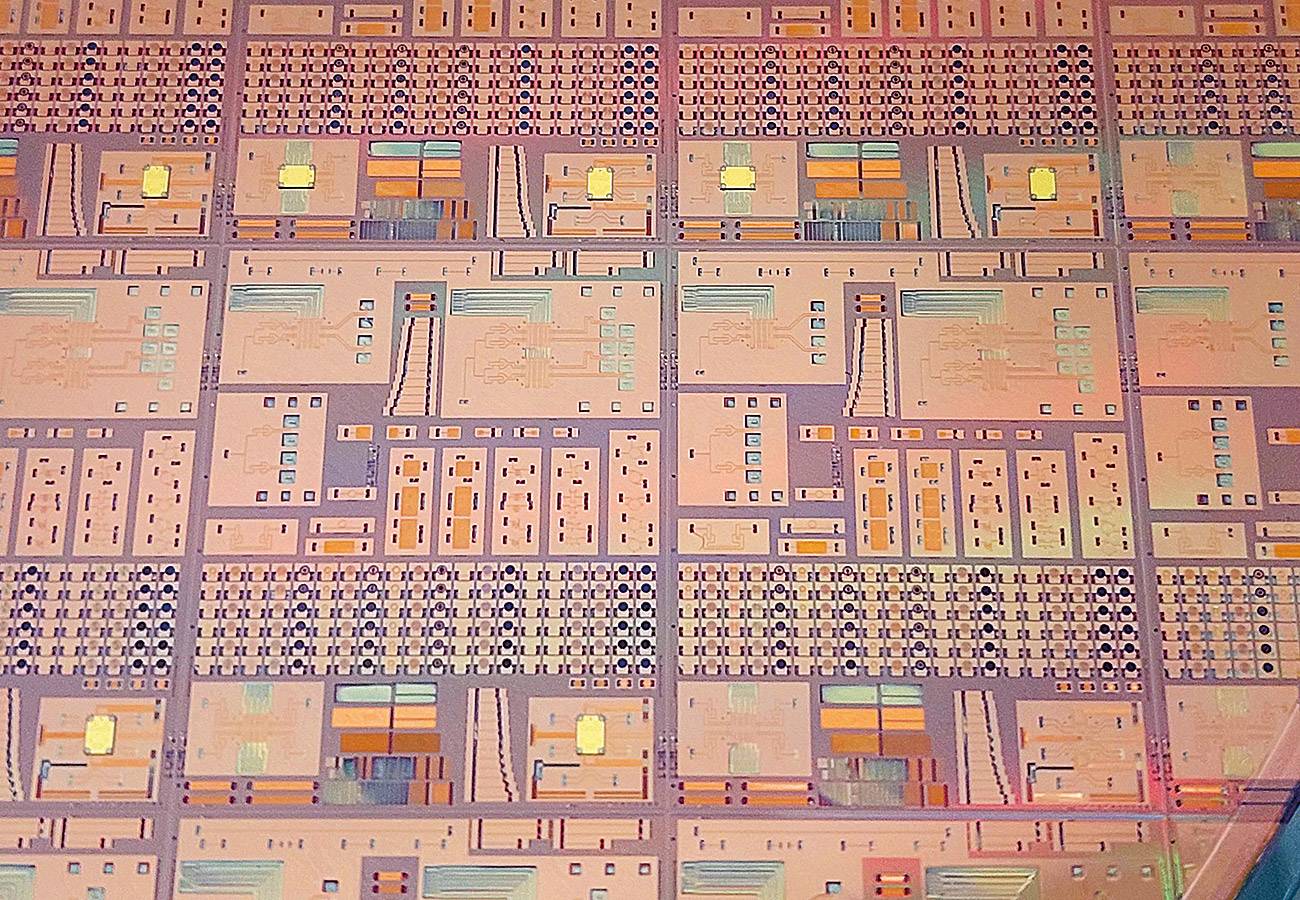

Koh Young präsentierte Inspektionslösungen für die Halbleiterfertigung auf der ECTC 2025 in Texas

Koh Young präsentierte Inspektionslösungen für die Halbleiterfertigung auf der ECTC 2025 in Texas

Glas etabliert sich als Interposer und Substratmaterial

Die texanische ECTC 2025 dokumentierte eindrucksvoll, dass die Diskussion um Substratmaterialien nicht länger akademisch geführt wird. Die Roadmaps der großen Halbleiter- und Packaging-Hersteller zeigen, dass Glas in den nächsten Jahren verstärkt als Interposer und Substratmaterial etabliert wird – zunächst in Co-Packaged-Optics, später auch im Mixed-Signal- und RF-Bereich [1]. Die industrielle Skalierung ist eingeleitet, erste Pilotlinien stehen, erste Module sind in der Qualifizierung. Molded RDL bleibt für viele Anwendungen ein verlässlicher Standard, stößt jedoch bei Layerdichte, Pitch und thermischer Kopplung zunehmend an Grenzen [2]. Die Zukunft gehört der Kombination aus beidem – Glas mit RDL-Aufbau – dort, wo Packaging nicht nur Verbindung, sondern Systemplattform ist.

300-mm-RF-Silizium- Interposer-Plattform des imec für Chiplet-basierte heterogene Integration

300-mm-RF-Silizium- Interposer-Plattform des imec für Chiplet-basierte heterogene Integration

Referenzen

[1] www.pcbdirectory.com/news/special-session-at-ieee-ectc-2025-explores-future-of-glass-core-and-rdl-interposer-substrates-technologies (Abruf: 29.07.2025).

[2] timestech.in/glass-core-vs-rdl-interposer-substrates-ready-for-prime-time/ (Abruf: 29.07.2025).

[3] iconnect007.com/article/145219/koh-young-invites-you-to-the-2025-ieee-electronic-components-and-technology-conference/145216/smt (Abruf: 29.07.2025).

[4] www.eletimes.com/a-record-year-for-the-75th-annual-ieee-electronic-components-and-technology-conference-ectc (Abruf: 29.07.2025).

[5] electronics360.globalspec.com/article/22381/ectc-2025-imec-demo-s-300-mm-rf-silicon-interposer-platform (Abruf: 29.07.2025).

Information

Die kommende ECTC findet vom 26.-29. Mai 2026 im JW Marriott Grande Lakes, Orlando (USA), statt. Abstracts für Vorträge können bereits jetzt eingereicht werden. Der Call for Papers endet am 12. Dezember 2025.