Die vorliegende Publikation unterstützt die Erforschung und Anwendung von Glass-Core-Substraten im Packaging elektronischer und elektro-mechanischer Komponenten und Module. Die thermischen und mechanischen Vorteile – etwa niedriger CTE, einstellbarer E-Modul, hohe Temperaturbeständigkeit und geringe Verformung – ermöglichen deren Einsatz als Substitut für herkömmliche Interposer. Anhand der Hetero-Integration über mehrere Package-Levels wird das Potenzial für nachhaltige, zuverlässige Systeme gezeigt.

This publication supports research into and application of glass core substrates in the packaging of electronic and electromechanical components and modules. Their thermal and mechanical benefits – such as low CTE, tunable modulus, high temperature resistance and minimal warpage – enable substitution for conventional interposers. Heterointegration across multiple package levels demonstrates the potential for sustainable, reliable systems.

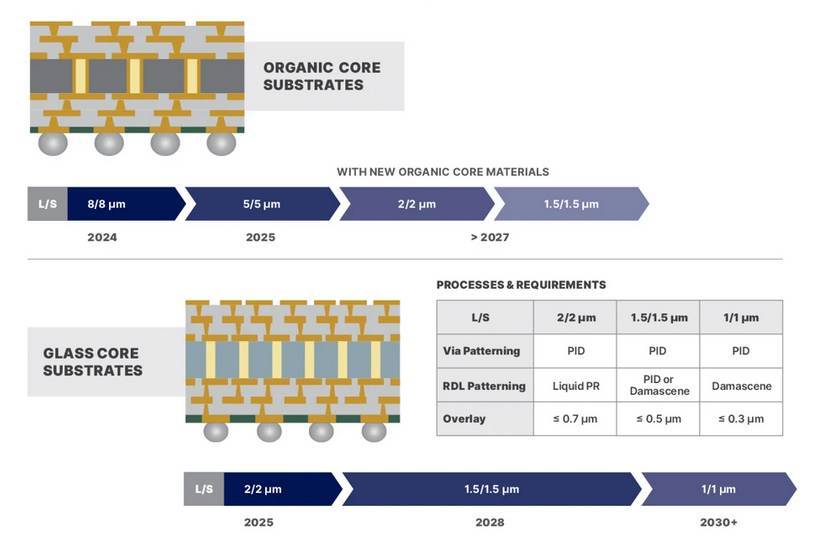

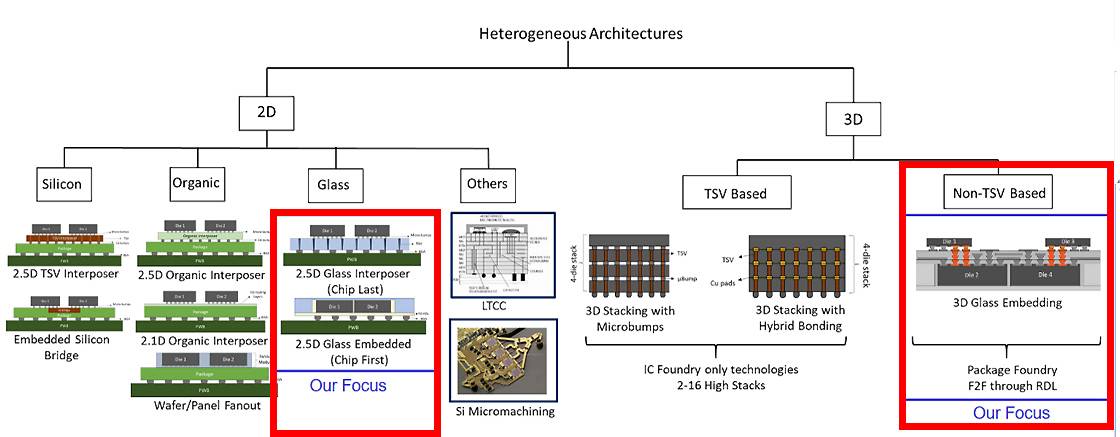

Gerade die thermischen und thermomechanischen Vorteile von Glass-Core-Substraten, wie niedriger CTE, einstellbarer E-Modul, Fähigkeit minimaler L/S, höhere Temperaturbeständigkeit und Warpage nahe Null, sollen beitragen, ein Substitut für organische, Silicium-, Mold- und optische Interposer bereitzustellen. Unter Berücksichtigung der Industrie- und Automotive-Prüfnormen kann am Beispiel der Hetero-Integration ein weiterer Baustein der Digitalisierung und Nachhaltigkeit erarbeitet werden, der die Systemfähigkeit von Glass-Core-Substraten im technischen Umfeld nachweist. Die Hetero-Integration umfasst ein großes Technologieportfolio über die verschiedenen Package-Levels, die sich gegenüber den letzten Jahren in Richtung des Chips verschoben haben: Level 0 ist der Chip, Level 1 ist hier nunmehr die Integration der Chips auf einen Wafer oder das Stapeln der Chips übereinander, Level 2 ist die Integrationslage mit organischen Interposern oder Glas-Interposern mit den Anschlüssen für die späteren Systemkomponenten, Level 3 ist das Substrat als Systemträger mit erweiterten Funktionalitäten [1]. Das Chipdesign beeinflusst entscheidend, wie zuverlässig, langlebig und ökologisch nachhaltig Elektronikprodukte sind [2]. In Abbildung 1 ist eine Industrie-Roadmap zum Einsatz von Glass-Core-Substraten im Vergleich mit organischen Core-Substraten dargestellt. Sie verdeutlicht den prinzipiellen Aufbau und die Prozessanforderungen. Die L/S- Möglichkeiten sind gleichfalls integriert.

Abb.1: Industrie-Roadmap für den Übergang von organischen Substraten (oben) zu Glas- Substraten (unten) und

Abb.1: Industrie-Roadmap für den Übergang von organischen Substraten (oben) zu Glas- Substraten (unten) und

Advanced IC Substrates (AICS) zeichnen sich durch eine definierte Line/Space-Charakteristik aus, wobei die Frage nach der Fähigkeit der Erfüllung der Forderungen bleibt. Hier sind die technologischen Möglichkeiten von Glass-Core-Substraten neu zu berücksichtigen. Eine Option wäre die Erhöhung der Integrationsdichte auf den Substraten.

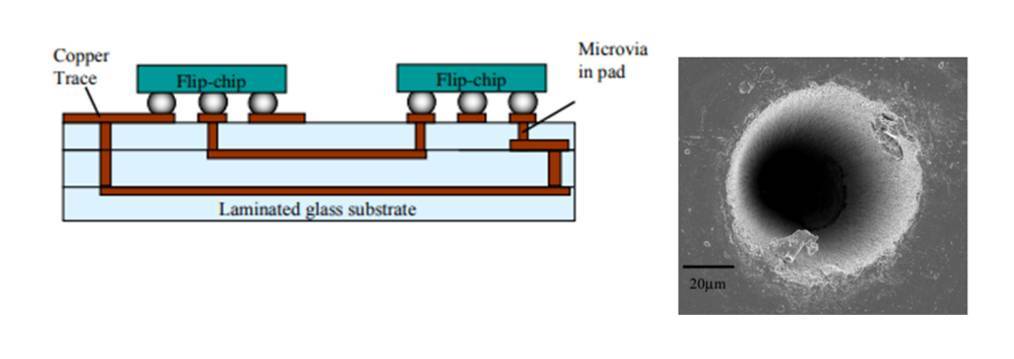

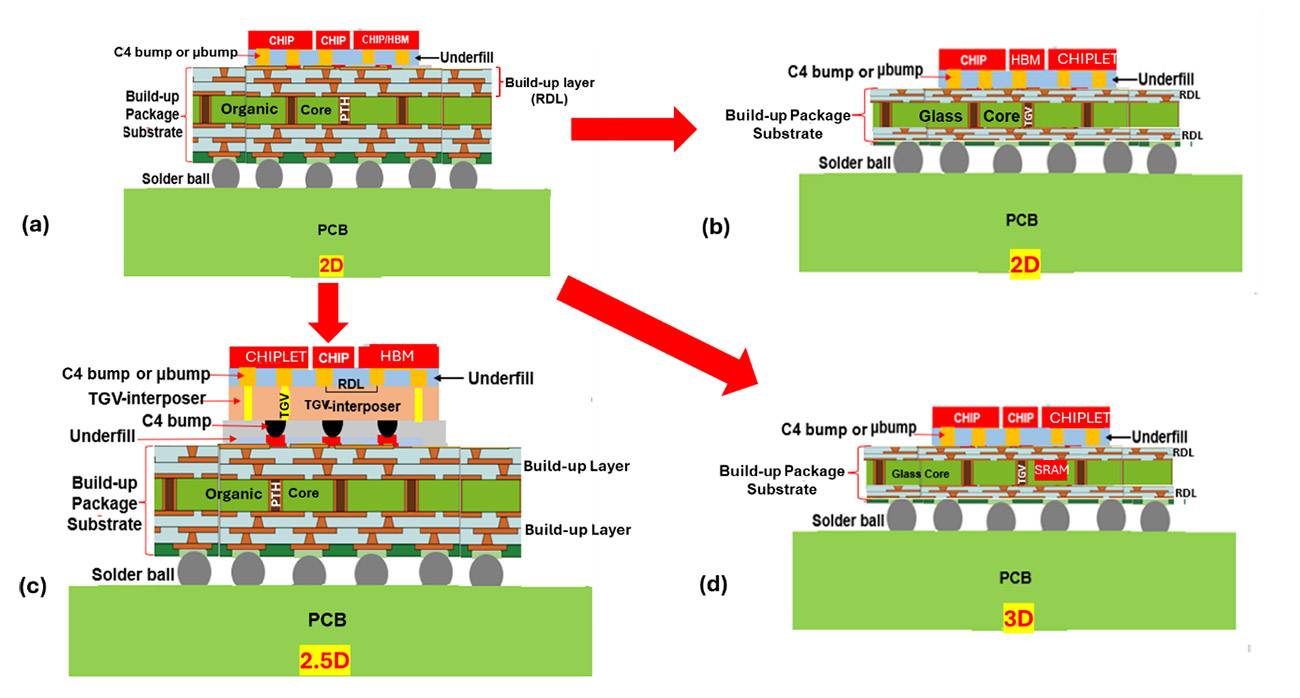

In Abbildung 2 ist der schematische Aufbau von Multilayern mit laminierten Glass-Substraten dargestellt mit einer Ergänzung des Aufbaus von Through-Glass-Vias (TGV) zur Verdrahtung in der Z-Achse des Multilayers. Das Packaging ist eines der zentralen Themen bei der Herstellung elektronischer Bauelemente und Komponenten. Hier wird das Funktionselement (Si, SiC, GaN, GaAs oder InP) auf Interposern montiert, um nachfolgend durch entsprechende Umverdrahtung das funktionelle Bauteil auf geeigneten Substraten zu realisieren. Die Substrate können metallisch, organisch und/oder anorganisch sein, je nach funktionellen Anforderungen an das Package. Im Packaging-Bereich werden CTE-Unterschiede im Package-Aufbau und Warpage-Eigenschaften der Substrate (Interposer) immer stärker wirksam. Damit verbunden sind Probleme im First Level und Second Level der Komponenten, die im Sinne der Verfahrenszuverlässigkeit und der Board-Level-Reliability funktionell und zuverlässigkeitsorientiert limitierend wirken. Hier muss definitiv Abhilfe geschaffen werden, um die Anforderungen an 2D- und 3D-Packages sowie heterogene Integration erfüllen zu können. Hier bietet sich der Werkstoff Glas an, um die physikalisch-chemischen Vorteile und thermomechanischen Eigenschaften nutzbringend in den Package-Aufbau zu integrieren. Glas als Interposer und/oder als Substrat ist Bestandteil internationaler Anstrengungen zur Bewältigung vorstehender Einschränkungen, siehe Tabelle 1.

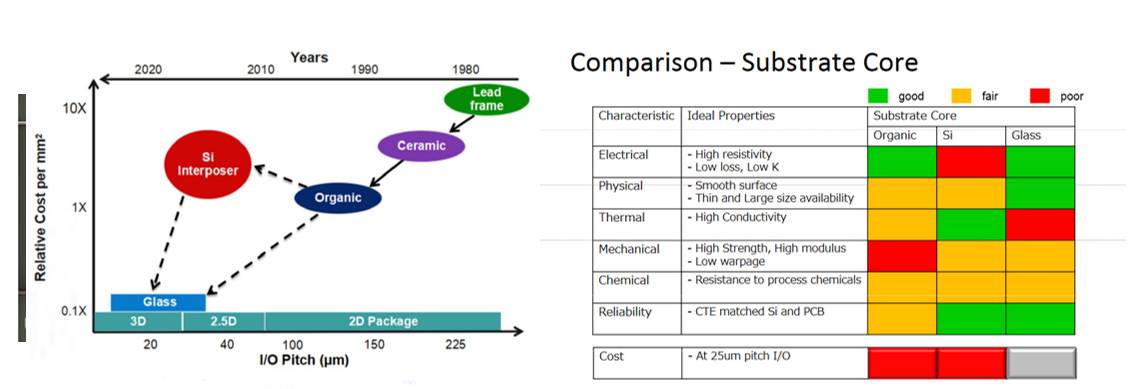

In Abbildung 5 ist ein Vergleich der organischen Interposer mit Silicium-Interposern und Glass-Core-Substraten dargestellt. Integriert in die Grafik ist ein Kostenvergleich zwischen Leadframes, keramischen, organischen und Si-Interposern zu Glass-Core-Substraten und ein Vergleich potenzieller Vorteile elektrischer, physikalischer, thermischer, mechanischer, thermo-mechanischer und chemischer Eigenschaften.

Abb. 2: Schematisches Diagramm von Multilayer-Glas- Substraten für Flip Chip Assembly

Abb. 2: Schematisches Diagramm von Multilayer-Glas- Substraten für Flip Chip Assembly

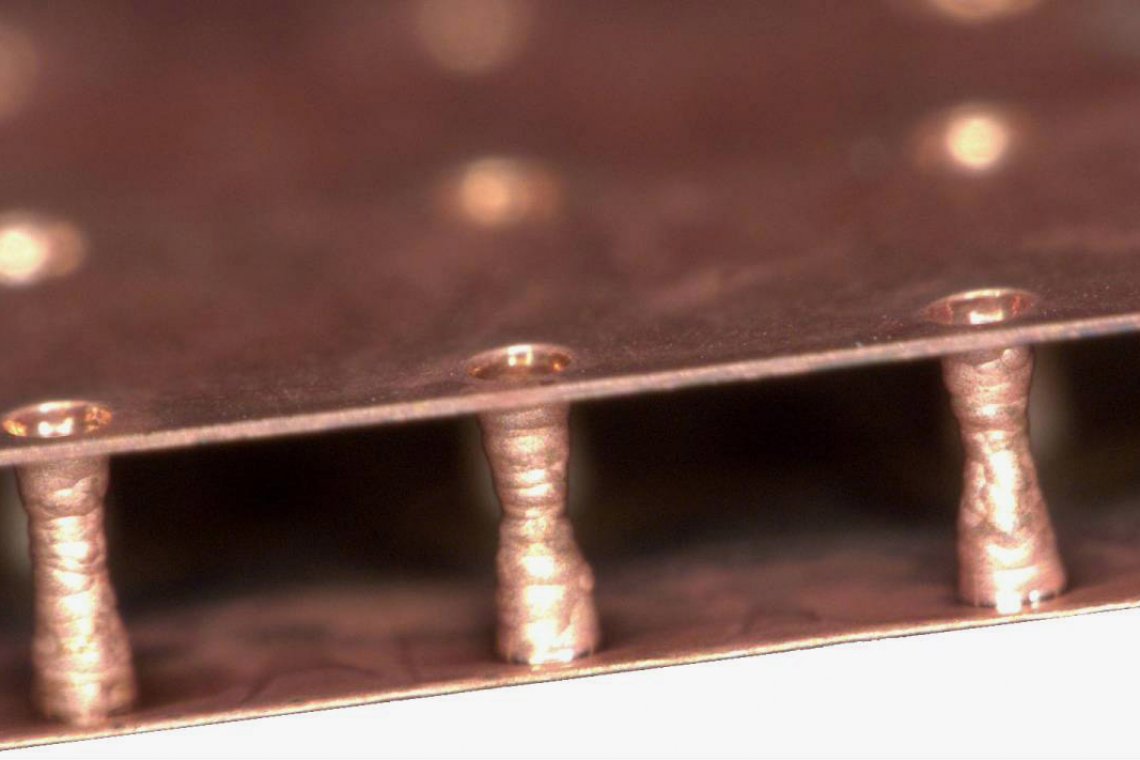

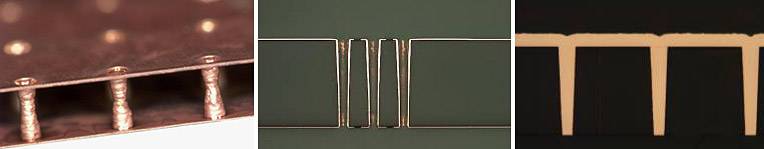

Abb 3: (a) Through-Glass-Vias PlanOptik - (b) Through-Glass-Vias (Oktober 2023) - (c) TGV FhG (2023). TGV-Substrate (Through-Glass-Vias) können die Leitungslänge erheblich reduzieren

Abb 3: (a) Through-Glass-Vias PlanOptik - (b) Through-Glass-Vias (Oktober 2023) - (c) TGV FhG (2023). TGV-Substrate (Through-Glass-Vias) können die Leitungslänge erheblich reduzieren

Abb. 4: Advanced Packaging und heterogene Integration

Abb. 4: Advanced Packaging und heterogene Integration

Abb. 5: Relative Kosten im Vergleich verschiedener Substrate

Abb. 5: Relative Kosten im Vergleich verschiedener Substrate

|

Organische Substrate |

Glass-Core-Substrate |

| >10/10 µm | Derzeit <5/f L/S und ein Anstieg auf <2/2 L/S in den nächsten Jahren |

| Niedrige Kosten bei der Großserienfertigung gegenüber Glaskernsubstraten | Vertragen höhere Temperaturen und bieten 50 % weniger pattern distortion |

| Verformungsprobleme bei größeren organischen Substraten | Aus lithografischer Sicht haben Glaskernsubstrate aufgrund der extrem geringen Ebenheit bessere DoF (Degrees of freedom) |

| Niedrigere Verarbeitungstemperatur aufgrund der polymeren Beschaffenheit des Kerns gegenüber Glaskerbensubstraten | Glaskernsubstrat hat eine höhere Interkonnektordichte (bis zu 10× im Vergleich zu OCS) |

| Dielekrische Konstante schwankt zwischen 4 und 6 | Weniger Verzugsprobleme, da die mechanischen Eigenschaften von Glaskernsubstraten ultragroße Gehäuse (bis zu 240 × 240) ermöglichen |

| Höherer Verlustfaktor von ~ 0,02 gegenüber Glaskernsubstraten (~ 0,005) | Großformatige Substrate ermöglichen eine hohe Montageeffizienz |

| Geringere Wärmeleitfähigkeit als Glaskernsubstrate: 0,2-0,5 < ~1,5 W/mK | Glaskernsubstrate bieten eine höhere Flexibilität beim Design bzgl. Signalführung und Stromversorgung |

| Höherer CTE (Coefficient of Thermal Expansion von ~17 gegenüber Glaskernsubstraten (3-8 ppm/°C) | Bei der Stromversorgung bieten Glaskernsubstrate Hochgeschwindigkeitssignale bei extrem niedrigem Stromverbrauch |

| Breiteres Marktspektrum, zielen vor allem auf Anwendungen im unteren bis mittleren Preissegment ab | Die Formstabilität des Glaskernsubstrats ist entscheidend für die präzise Ausrichtung zwischen den Schichten in Verbindungsüberlagerungen mit sehr engen Toleranzen |

| Gefüllte TGC mit hohem Aspect Ratio von (1:10 bis 1:50) | |

| Glaskerndicke von bis zu 1 mm für Anwendungen wie KI und Rechenzentren | |

| Sehr aktive Forschung und Entwicklung während der letzten Jahre |

Through-Glass-Vias

Die Integration von Glas in verschiedenen Packages ist in Abbildung 7 dargestellt. Es handelt sich hier um Package-Varianten des von Unimicron. Die Multilayer-Varianten beinhalten Through-Glass-Vias, die in der z-Achse mittels Laserbohren eingebracht werden. Der Durchmesser der Vias ist durch die Lasertechnik vorgegeben. Die z-Achse kann bis 500 µm tief in die Glassubstrate gebohrt werden, nachfolgend nach dem Ätzen metallisiert werden.

Die 5G- und 6G-Technologie geht mit noch nie gesehenen Anforderungen bei Datenmengen, Übertragungsgeschwindigkeiten und Verarbeitungskapazitäten einher. Dies bringt auch das Problem verstärkter Abwärme von Komponenten und Systemen mit sich [3].

Die Wärmeleitfähigkeit des Glases ist limitiert, weshalb sich vorteilhafterweise beliebig viele metallisch gefüllte Through Glass Vias im Substrat anbieten, die Wärmeleitfähigkeit in der z-Achse zu verbessern. Gerade in der Leistungselektronik wäre eine derartige Verfahrensweise zielführend.

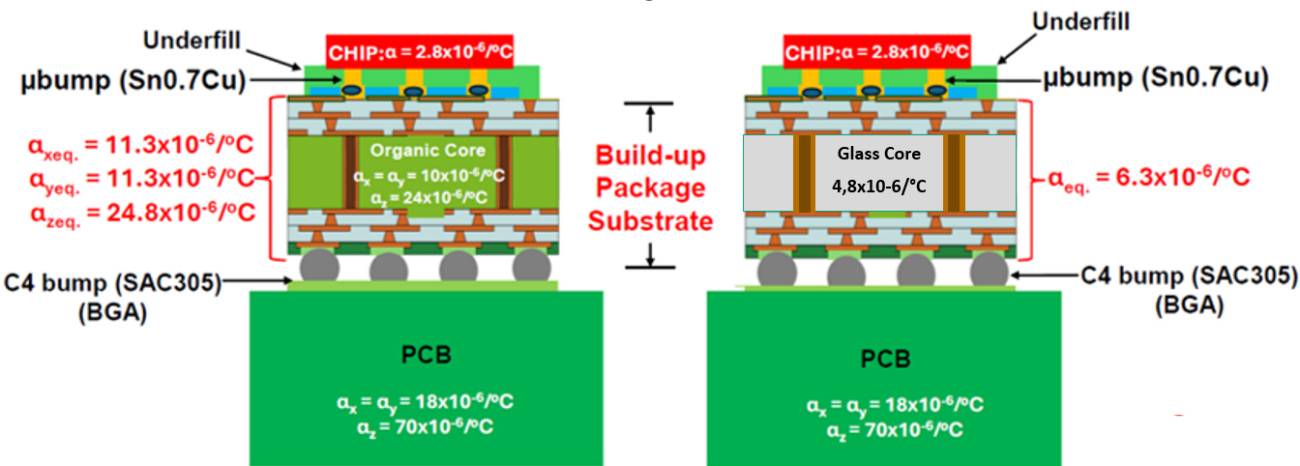

Ein direkter Vergleich organisches Core-Substrat mit Glass-Core-Substraten ist in Abbildung 7 gegeben. Die Unterschiede im CTE-Wert in Stapelverbund werden deutlich abgebildet und verdeutlichen die Vorteile im Warpage-Verhalten. Gerade hier sind Vorteile im First Level und Second Level zu erwarten, um die thermo-mechanische Stabilität der Packages an die Forderungen z. B. der Automotive-Industrie anzupassen.

Im DARPA-Programm wird Glas als Interposer benannt, um dann nach funktioneller Erweiterung auf Substraten zum finalen Package wertgeschöpft zu werden [4]. Bei CHIMES (Penn State), PRC (Georgia Tech) in den USA, Joint2 in Japan, der Konferenz ISPEC 2024 in Indien und weiteren Aktivitäten in Japan und China wird die Arbeit am Thema Glass-Panel-Based-Packaging international intensiv staatlich gefördert und vorangetrieben. Anstelle von organischen Interposern werden hier Glas-Interposer für die funktionelle Umverdrahtung vorgeschlagen. Zur vertikalen Verdrahtung werden Through-Glass-Vias realisiert, die die z-Achse elektrisch kontaktieren. Einzigartige Charakteristika von Glas wie die thermischen und mechanischen Eigenschaften oder die geringen Dickentoleranzen in den Geometrien ermöglichen Innovationen und nie dagewesene Designs im Bereich der Halbleiterverpackung. Dank dieser Eigenschaften können Experten im Halbleiter-Bereich hochwertige und neuartige Packaging-Lösungen konzipieren.

Die Struktur des avisierten Packageaufbaus ist in Abbildung 6 im direkten Vergleich mit einem organischen Interposer gezeigt. Die hier mögliche CTE-Anpassung mit dem zu erwartenden geringsten Warpage-Level spiegelt die technologischen Fähigkeiten wider. Eine vergleichende Betrachtung von Laminat-Interposer, Silicium-Interposer, Mold-Interposer und Glas-Interposer für mikroelektronische und mechanisch-elektronische Komponenten und Module ist international nicht vorhanden, wäre aber für die zuverlässigkeitsrelevanten Aspekte des Packaging und der Board Level Reliability zwingend erforderlich.

Abb. 6: Glass Interposer in verschiedenen Package-Aufbauten

Abb. 6: Glass Interposer in verschiedenen Package-Aufbauten

Abb. 7: Vergleich organischer gegenüber Glass-Core- Substraten

Abb. 7: Vergleich organischer gegenüber Glass-Core- Substraten

Referenzen

[1] Erik Jung, IZM, Hetero-Integration: Die Zukunft der Halbleitertechnik, 12/2024.

[2] Brüning, FhG, IZM, Januar 2025.

[3] Schott Packaging 2023.

[4] DARPA NGMM Program, Page 13, October 16, 2023: „Although it is anticipated that a diverse set of chips that will be supported by this fabrication capability, to facilitate the standardization of design and processes in Phases 1 and 2 of the NGMM program, the candidate semiconductor substrates for the exemplar circuit will be limited to silicon, silicon carbide (including GaN epilayers), gallium arsenide, InP, and/or glass.“

Literatur

Christopher Blancher, ‚Multilayer Process Development', IMAPS, 2023.

Ralph Delmdahl et al, ‚High Density Through Glass Vias for Advanced Chip Packaging, 32nd Int. Congress of Lasers & Electro-optics', 2013.

Ralph Delmdahl et al, ‚Laser Drilling of High-Density Through Glass Vias (TGVs) for 2.5D and 3DPackaging;',Journal of the Microelectronic and Packaging Society, Juni 2014, https://koreascience.or.kr/article/JAKO201425560113563.page (Abruf: 14.07.2025).

Serhat Erdogan et al, ‚Characterization of Chip-to-Package Interconnects for Glass Panel Embedding (GPE) for Sub-THz Wireless Communications', 71th ECTC Conference, 2021.

Koji Fujimoto, ‚Development of Glass Core Substrates for Long-Term Reliability Under Thermal Stress', ECTC 2025.

Bryce Gray, ‚Direct Digital Manufacturing for Laser-Drilled Vias in Multilayer Glass Printed Circuit Structures', ECTC 2025.

Kai-Qi Huang, Madhavan Swaminathan, ‚Antennas in Glass Interposer For sub-THz Applications', 71th ECTC Conference 2021.

Intel-publication, Electronic Design, 24.08.2023.

Xiaofan Jia et al, ‚Antenna-Integrated, Die-Embedded Glass Package for 6G Wireless Applications', 72th ECTC Conference, 2022.

Yaming Jiang, ‚Dry Film Photo-Imageable Dielectric Enabling Glass Core Substrate TGV Filling and Build-up', ECTC 2025.

Mandakini Kanungo, ‚Metallization of Helium-Hermetic and Thermo-Mechanically Reliable Through Glass Vias (TGV) by Conformal Pinched Via (CPV) Approach', ECTC 2025.

Andrew Ketterson et al, ‚Glass-Core Substrates for RF Heterogeneous Integrated Packages', IMAPS 2023, 2.-5. Oktober 2023, San Diego.

Andrew Ketterson et al. ‚Glass-Core Substrates for RF Heterogeneous Integrated Packages; Int. Symp. On Microelectronics: San Diego', 3. Oktober 2023.

Alexander R. King, ,Multi-Layer Sequential Fabrication and Mechanics-Based Model of Glass-Core Packages with Embedded Dies', ECTC 2025.

Satoru Kuramochi et al, ‚High Speed Transmission Characteristics on Glass based interposers'. EMPC Conference, 2023.

Ching-Kuan Lee, ‚Reliability Evaluation of Glass Interposer Module; Electronic Design', 2023.

John H. Lau, Glass-Core Substrate versus Organic-Core Substrate, ECTC 2025.

David H. Levy et al, ‚Enabling low loss thin glass solutions for 5G / mm-Wave applications'; 71th ECTC Conf., 1.-4. Juni 2021, Virtual.

Xingchen Li, ‚3D Vertical Glass Stacking for 6G Communications – Interconnect Fabrication and Broadband Characterization',ECTC 2025

Fuhan Liu et al, ‚High Aspect Ration through Glass Vias(TGV)', Georgia Tech. Atlanta, November 2019.

Yasuhiro Morikawa, ‚Deep via and trench etching of low CTE glass package substrate using SF6, NF3 and H2O based NLD plasma process', ECTC 2025.

Toshio Otsu, ‚High-aspect-ratio, 6-μm-diameter through-glass-via fabrication into 100-μm-thick ENA1 by dry laser micro-drilling process',ECTC 2025.

Rafael Santos et al, ‚Fabrication of Panel-Level Glass Substrates with Complete Design Freedom using LIDE', IMAPS 2022, Boston.

Yoichiro Sato, ‚Laser-drilling formation of through-glass-via (TGV) on polymer-laminated glass'; Journal of Materials science: Materials in Electronics, Juni 2019, https://doi.org/10.1007/s10854-019-01354-5.

Henning Schröder al: ‚glassPack – A 3D Glass Based Interposer Concept for SiP with Integrated Optical Interconnects', 71th ECTC Conference, 2021.

Seong-Ho Seok, ‚Advanced Glass Substrate Fabrication and Metallization Process Technology for Co-Packaged Optics',ECTC 2025.

Aric B. Shorey, ‚Progress and application of through glass via (TGV) technology', IMAPS 2016.

Aric B. Shorey et al. ‚Thin Glass Substrates with Through-Glass Vias', IMAPS 2019, Boston.

Masahiro Sunohara, ‚Development of Glass Core Build-up Substate with TGV', ECTC 2025

Madhavan Swaminathan, ‚Semiconductor Packaging, The Future is Now!', Georgia Tech Atlanta, 2023 (Vortrag), https://ieeetv.ieee.org/dallas-eps/semiconductor-packaging-the-future-is-now (Abruf: 14. Juli 2025).

Masaya Tanaka, ‚Fundamental transmission performance evaluation of sub-2 micron fine-wiring for Glass Substrate', ECTC 2025.

Michael Töpper et al., ‚3-D Thin Film Interposer Based on TGV (Through Glass Vias): An Alternative to Si-Interposer', ECTC 2010.

Trent Uehling, ‚Chiplet Package for Automotive and Edge Processors', ECTC 2025.

Frank Wie, ‚Comprehensive Die Strengths Comparisons for Glass-Core Advanced Packaging Substrates using Different Singulation Methods', ECTC 2025.