Die Nachfrage nach hochleistungsfähigen und energieeffizienten Halbleitersubstraten wird durch den rasant steigenden Bedarf an Rechenleistung und Energieeffizienz angetrieben. Neue Smartphones haben Substrate von zwei bis sechs Lagen bei 15 x 15 mm Fläche. Anspruchsvolle PCs liegen bei vier bis acht Lagen und 30 x 30 mm Fläche. Bei Servern, KI Systemen und selbstfahrenden Autos kommen Substrate mit zehn bis 22 Lagen zum Einsatz bei 50 x 50 mm Fläche. Für KI-Anwendungen werden aber zukünftig 100 x 100 mm Fläche erforderlich sein, um mehrere Tausend I/Os bei einem Multi-Die Chiplet umzuverdrahten.

Das IC-Substrat bildet dabei eine physische Schnittstelle zwischen dem Mikroprozessor und der Leiterplatte. Es überbrückt die Kluft zwischen zwei sehr unterschiedlichen Größenordnungen, wenige Nanometer versus 5 - 40 µm. Dabei schützt das organische Halbleitersubstrat die ICs, optimiert die Verlegung von Hochgeschwindigkeitssignalleitungen, hilft bei der effizienten Verteilung der Stromleitungen und leitet die Wärme ab, die sonst die Leistung beeinträchtigen könnte (Abb.1).

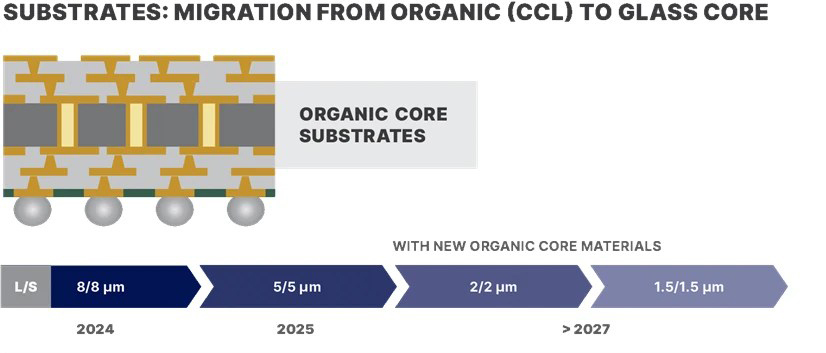

Abb. 1: Die Roadmap von organischen Substraten zu Glas

Abb. 1: Die Roadmap von organischen Substraten zu Glas

Wann erreichen organische Substrate ihre Grenze?

Fortschrittliche IC-Substrate (Advanced IC substrates, AICS) bewegen sich seit einiger Zeit auf den Technologieknotenpunkt 2 µm Line/Space (L/S) zu. In diesem Grenzbereich stellen sich jedoch noch viele Fragen hinsichtlich der Fähigkeit organischer Substrate, die Anforderungen der nächsten Generation fortschrittlicher Gehäuse (Advanced Packages, AP) zu erfüllen, die weniger als 2 µm L/S und vielleicht sogar nur 1,5 µm L/S aufweisen. Einfach ausgedrückt: Sind organische Substrate der Herausforderung gewachsen? (Abb. 2)

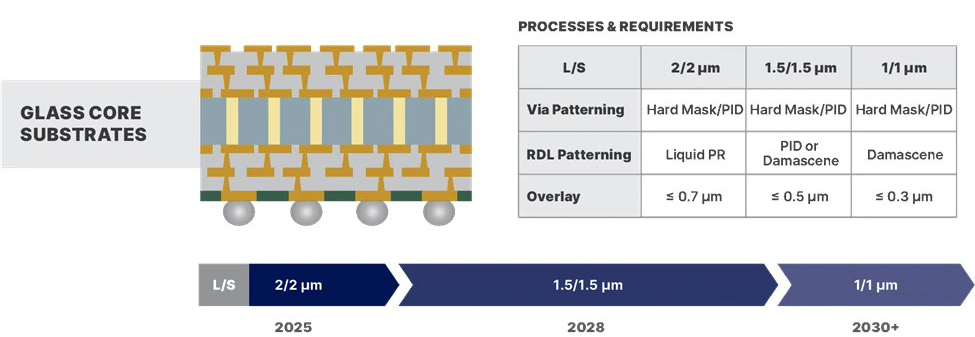

Abb. 2: Die Roadmap zu Glassubstraten

Abb. 2: Die Roadmap zu Glassubstraten

Die Anwendung Künstlicher Intelligenz treibt mit ihren Datenmengen die Entwicklung vor sich her. Dadurch wird die Entwicklung von Glassubstraten beschleunigt, und diese könnten organische Interposer bald überflüssig machen. Glassubstrate erhöhen die Geschwindigkeit von Halbleitern bis zu 40 % und reduzieren gleichzeitig den Stromverbrauch um ca. 50 %.

Die großen Halbleiterhersteller haben angekündigt, für die nächste Generation ihrer Chips Glassubstrate zu verwenden. Intel hat 1 Mrd. $ in die Entwicklung von Glassubstraten investiert, die bis 2030 auf den Markt kommen sollen.

In Korea nimmt die Tochtergesellschaft von SKC, Absolics, ein 70/30-Gemeinschaftsunternehmen mit Applied Materials, eine Vorreiterrolle ein. In der ersten Hälfte des Jahres 2024 hat man den Bau der weltweit ersten Massenproduktionsanlage für Glassubstrate in Georgia abgeschlossen.

Im Rahmen des Inflation Reduction Acts hat das Unternehmen von der US-Regierung Produktionssubventionen in Höhe von 75 Mio. $ und F&E-Zuschüsse in Höhe von 100 Mio. $ erhalten. Das Unternehmen plant die Aufnahme der Massenproduktion bis Ende dieses Jahres.

Samsung Electro-Mechanics hat eine Pilotlinie für Glassubstrate eingerichtet und plant, noch in diesem Jahr Prototypen an zwei bis drei Kunden zu liefern, wobei die Massenproduktion voraussichtlich nach 2027 beginnen soll.

LG Innotek baut eine Pilotlinie auf und will noch in diesem Jahr mit der Herstellung von Prototypen beginnen. Die Prognose von LG ist, dass Glassubstrate in den nächsten zwei bis drei Jahren allgemein in Kommunikationshalbleitern eingesetzt werden. Bei Server-Halbleitern werden sie voraussichtlich in etwa fünf Jahren zu einer Mainstream-Lösung werden.

Unternehmen in Japan und Taiwan machen ebenfalls rasche Fortschritte bei der Entwicklung von Glassubstraten (und anderen Substraten) für das Advanced Packaging von 2-nm-Chips und kleiner.

Hat Kupfer seine physikalischen Grenzen erreicht?

Bereits vor 25 Jahren wurde diese Frage gestellt. Damals betreute beim IZM in Berlin Prof. Dr. Wolfgang Scheel eine Gruppe unter Leitung des Physikers Prof. Dr. Henning Schröder, die an der Dünnglastechnologie für photonische Systemintegration arbeitete.

Getrieben wurde die Entwicklung durch den Bedarf an Bandbreite zur störungsfreien Übertragung großer Datenmengen innerhalb von Rechner- und Telekommunikationssystemen. Für die damit verbundene Forderung nach hochbitfähigen Kurzstreckenverbindungen stellten optische Übertragungsstrecken eine sinnvolle Alternative zu hochfrequenten elektrischen Verbindungen dar. Das BMBF-Projekt NeGIT (New Generation Interconnection Technology) förderte damals bereits die Herstellung von Leiterplatten mit innenliegenden optischen Wellenleitern auf Polymerbasis.

KI sprengt heute alle Datenmengen

Die rasante Ausbreitung der KI hat die Datenübertragung innerhalb der KI-Infrastruktur vor nie dagewesene Herausforderungen gestellt. Insbesondere herkömmliche Kupferverbindungen, die einst für die Datenübertragung ausreichten, werden nun den Anforderungen der immer komplexeren KI-Modelle nicht mehr gerecht.

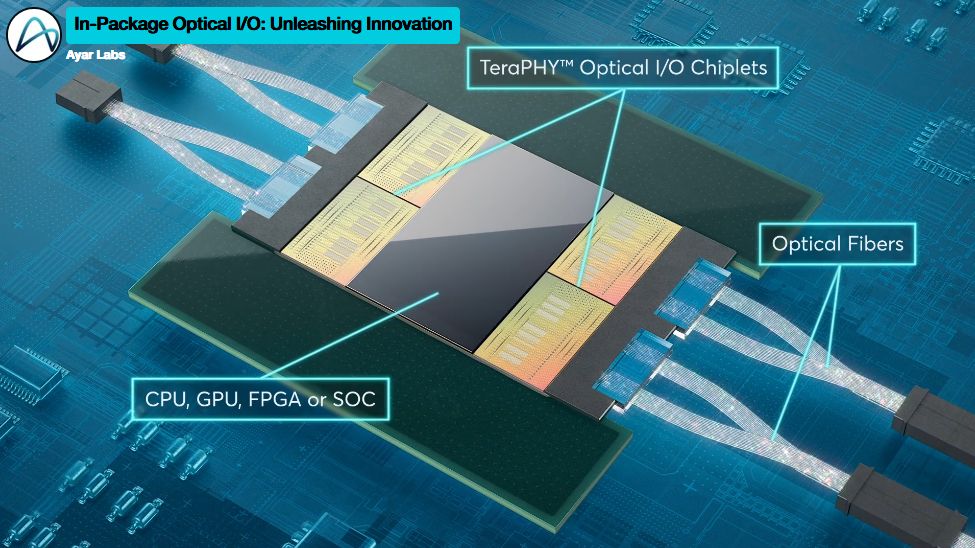

Die optische E/A-Technologie beseitigt herkömmliche Engpässe bei Verbindungen, indem sie Datenbewegungen mit Geschwindigkeiten ermöglicht, die für umfangreiche KI-Workloads erforderlich sind. Durch die Reduzierung von Latenzzeiten, Stromverbrauch und Betriebskosten trägt die Technologie zur Optimierung der KI-Infrastruktur bei und macht sie effizienter und kostengünstiger (Abb. 3).

Abb. 3: Ein Beispiel der USFirma Ayar Labs: Optische I/O erhöhen die Bandbreite 5 -10×, reduzieren den Stromverbrauch 4 - 8× und die Latenzzeit um den Faktor 10

Abb. 3: Ein Beispiel der USFirma Ayar Labs: Optische I/O erhöhen die Bandbreite 5 -10×, reduzieren den Stromverbrauch 4 - 8× und die Latenzzeit um den Faktor 10

Der Schlüssel, das Alignment

Organische Substrate können sich während der Aushärtung verformen, dazu gehören Verzerrungen der X/Y Ebene mit Auswirkungen auf die Planheit der Substratoberfläche. Dazu kommt die zu grobe Korngröße des stromlosen Kupfers, die für feinere Leiterbahnen (< 2 µm) ungeeignet ist. Möglichkeiten zur Verbesserung der Genauigkeit beim Alignment von Durchkontaktierungen könnte die Verwendung von PID-Materialien (Photo Imageable Dielectric) sein, die lasergebohrte Durchkontaktierungen ersetzen. Eine andere Innovation: Die Hersteller könnten eine mit Resist strukturierte Hartmaske verwenden, um die Abmessungen der Durchkontaktierung festzulegen, und dann die Aufbauschicht auf der Kupferoberfläche der zuvor strukturierten RDL trocken ätzen.

Im Gegensatz zu organischen Substraten ist die Zukunft für Glassubstrate klar: Sie haben aufgrund ihrer Stabilität und ihrer elektrischen Eigenschaften das größte Potenzial, den 1-µm-L/S-Technologieknoten zu erreichen. Darüber hinaus wird durch das Ersetzen von durchkontaktierten Löchern (PTHs) durch Glas-Durchkontaktierungen (TGVs) die Dichte der Front-to-Back-Verbindungen erhöht (Abb. 4)

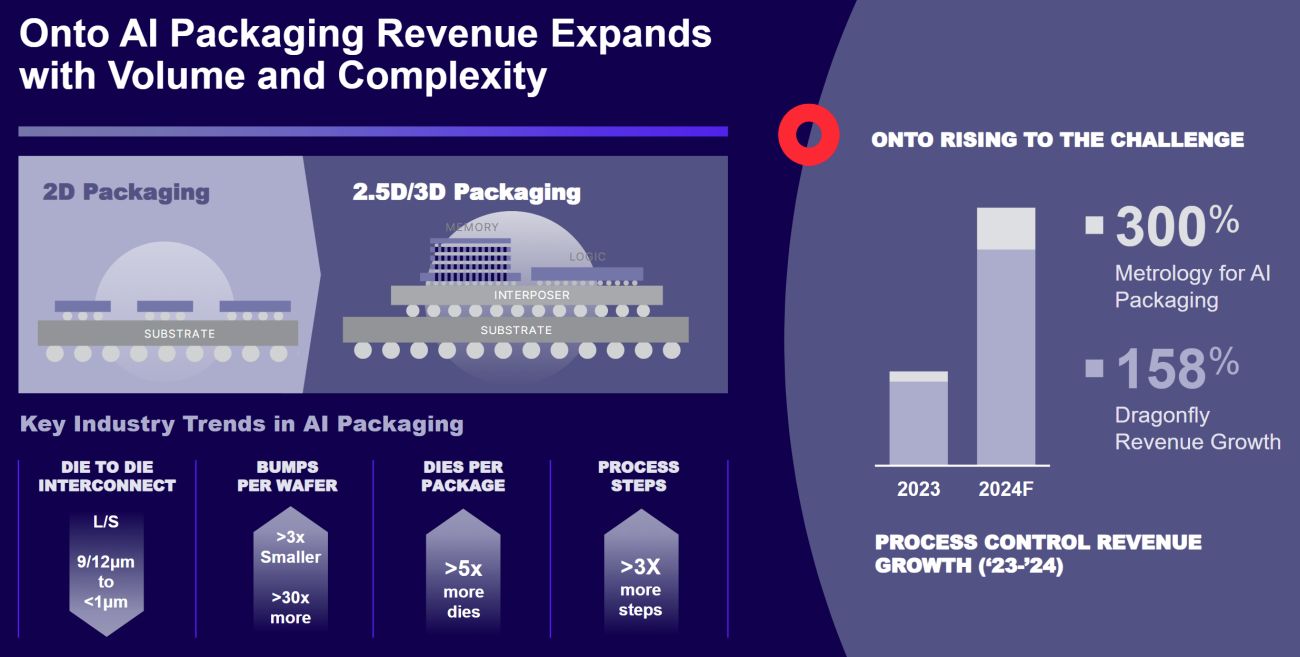

Abb. 4: AI Packaging Key Industry Trends

Abb. 4: AI Packaging Key Industry Trends

Auf den Punkt gebracht

Substrate verbinden Tausende von I/Os leistungsfähiger Mikrochips mit den viel größeren Strukturen der Leiterplatte und bilden so die Brücke zwischen der Nanowelt (nm Strukturen) der Halbleiterindustrie und der Mikrowelt (mm Strukturen) der Leiterplatten.

- Substrate haben zwei bis 20 Lagen und basieren auf organischem Laminat (Copper-Clad-Laminate)

- Die Auflösungsgrenze liegt bei 2-5 µm Strukturbreite (Leiterbahnbreite und -abstand)

- Aufgrund des immer schwierigeren Alignments und der Durchkontaktierung der einzelnen Lagen geht der Trend ab ca. 1,5 µm zu Glassubstraten

- Viele große Halbleiterhersteller von Intel, Samsung bis LG investieren in Produktionslinien für Glassubstrate, die ab 2027 in die Großserie gehen

Etwa alle zehn bis 20 Jahre gibt es in der Leiterplattenbranche eine Technologiedisruption oder, anders ausgedrückt, einen Technologiesprung. Ob von einseitig über durchkontaktiert zu Multilayer, Microvia, HDI oder nun Glassubstrat: Irgendwann erfordert, wie hier der Transport exorbitant steigende Datenströme bei der Anwendung künstlicher Intelligenz (AI) einen Technologiesprung.

Weitere Informationen, Zusammenhänge und Daten kann man auf dem Bayern Innovativ Leiterplattenforum am 26. Februar 2025 in Erding bei München erfahren.

Bleiben Sie uns gewogen.

Es grüßt Sie herzlich

Ihr

Hans-Joachim Friedrichkeit