Photonic processing units (PPUs) or photonic integrated circuits (PICs) are consistently increasing in complexity, application spectrum, and usage. This trend, however, is held back by a lack of packaging solutions for high I/O-count. The research project ‚Silhouette' aims to close this bottleneck with a universal platform approach. Central piece is a silicon-based interposer, to which optical function is added via a polymer layer stack. This article explains co-design and processing of the platform components for two optical, cryptographical applications.

1. Einleitung

Im letzten Jahrzehnt hat die Forschung an photonischen integrierten Schaltkreisen (engl.: photonic integrated circuits - PICs) und photonischen Recheneinheiten (photonic processing units - PPUs), d. h. monolithisch integrierten, optischen Mikrochips stark zugenommen [1, 2, 3]. Während die Komplexität und Anwendungsbreite der Chips sich dadurch deutlich erhöht hat, fehlt es an geeigneten Lösungen für die Systemintegration, bedingt insbesondere durch eine Lücke in der optischen Aufbau- und Verbindungstechnik. Aus Effizienz- und Bandbreitengesichtspunkten hat die optische Signalübertragung in großem Stil Einzug in die höheren Systemebenen von Rack-to-Rack bis zur Backplane gehalten, insbesondere mit faserbasierten Aufbauten. Diese sind jedoch begrenzt in Integrationsdichte und Skalierbarkeit und ermöglichen meist nur die Anbindung an die Außenwelt und keine Verbindungen innerhalb des Systems. Andere Lösungen für die elektro-optische Leiterplatte (EO-PCB) sind zwar erforscht, aber werden nur in geringerem Umfang eingesetzt. Zwischen PICs und EO-PCBs sind allerdings zusätzliche Umverdrahtungsträger, sog. elektro-optische Interposer, notwendig. Aktuell sind keine kommerziellen und nur wenige Lösungen in Forschungsarbeiten vorhanden. Die Anbindung der PICs beruht dann doch meist auf voluminösen Faseraufbauten und ermöglicht keine Verbindungen zwischen einzelnen PICs [4]

1.1. Universelles Plattformkonzept

Die Lücke zwischen PICs und den höheren Systemebenen soll durch das Plattformkonzept, welches aktuell im BMBF-Verbundprojekt ,SILHOUETTE' erforscht wird, geschlossen werden. Zentraler Bestandteil ist der Silicium-Interposer in Abbildung 1 mit Kupfer-Umverdrahtungslage und Goldpads für Draht- und Thermokompressionsbonden sowie Reflowlöten. Hierdurch kann eine Vielzahl von ungehäusten Chip-Bauelementen entweder face-up, wie in Abbildung 1 das programmierbare Logikgatter (FPGA) und die Photodiode, oder mittels Flip-Chip-Technik, wie die anwendungsspezifische integrierte Schaltung (ASIC), Laser und auch die PICs, mit Standardverfahren montiert und elektrisch kontaktiert werden. Die optische Kontaktierung erfolgt mittels eines polymeren Wellenleiterstapels mit integrierten µ-Spiegeln für Oberflächenkopplung zu den Faser-Gitter-Kopplern (FGC) auf den PICs. Über Kantenkopplung können ebenso Fasern und elektro-optische Wandler angesteuert werden.

![Abb. 1: Silizium-Interposer (E/O-Interposer), welcher Laser, photonische Recheneinheit (PPU), Photodioden (PD), programmierbare Logikgatter (FPGA) und anwendungsspezifische integrierte Schaltungen (ASIC) mechanisch, elektrisch und optisch über unterschiedliche Verfahren der Aufbau- und Verbindungstechnik kontaktiert [5] Abb. 1: Silizium-Interposer (E/O-Interposer), welcher Laser, photonische Recheneinheit (PPU), Photodioden (PD), programmierbare Logikgatter (FPGA) und anwendungsspezifische integrierte Schaltungen (ASIC) mechanisch, elektrisch und optisch über unterschiedliche Verfahren der Aufbau- und Verbindungstechnik kontaktiert [5]](/images/stories/Abo-2024-03/plus-2024-03-066.jpg) Abb. 1: Silizium-Interposer (E/O-Interposer), welcher Laser, photonische Recheneinheit (PPU), Photodioden (PD), programmierbare Logikgatter (FPGA) und anwendungsspezifische integrierte Schaltungen (ASIC) mechanisch, elektrisch und optisch über unterschiedliche Verfahren der Aufbau- und Verbindungstechnik kontaktiert [5]

Abb. 1: Silizium-Interposer (E/O-Interposer), welcher Laser, photonische Recheneinheit (PPU), Photodioden (PD), programmierbare Logikgatter (FPGA) und anwendungsspezifische integrierte Schaltungen (ASIC) mechanisch, elektrisch und optisch über unterschiedliche Verfahren der Aufbau- und Verbindungstechnik kontaktiert [5]

1.2. Photonische integrierte Schaltkreise

Im Projekt werden zwei verschiedene PICs entwickelt, die jeweils Anforderungen für Verschlüsselungsmechanismen der vertrauenswürdigen Elektronik erfüllen. Einerseits wird mit einem kryptografischen Multimode-Interferometer (K-MMI) eine sog. physikalische unklonbare Funktion(PUF) erforscht. Diese erzeugt für definierte Eingabewerte nicht vorhersagbare, aber deterministische eindeutige Ergebnisse, welche zur Identifizierung, Authentifizierung oder Verschlüsselung genutzt werden, wobei besonders photonische PUFs eine höhere Komplexität verglichen mit elektronischen PUFs zeigen und weniger anfällig gegenüber Angriffen sind [6]. Das K-MMI erzeugt gemäß Abbildung 2 einen privaten Schlüssel, indem das optische Signal in 16 Kanäle aufgeteilt und mit einem öffentlichen Schlüssel phasencodiert wird. Dieses wird dann parallel in einen Multimode-Wellenleiter mit definierten Maßen und eingebrachter Topografie eingespeist, sodass sich der private Schlüssel als Modeninterferenzmuster auf den 16 Kanälen am Ausgang des Interferometers abbildet.

Andererseits wird mit dem optischen Zufallszahlengenerator die für Verschlüsselungen wichtige Fähigkeit gewonnen, wirkliche Zufallszahlen zu generieren. Wirkliche Zufallszahlengeneratoren - engl.: true random number generator (TRNG) - können z. B. durch radioaktiven Zerfall [7], elektrisches Rauschen [8] oder atomare Systeme [9] aufgebaut werden. Im Falle des optischen TRNG wird die Quantennatur von Photonen ausgenutzt [10]. Dazu wird ein Ringoszillator von zwei Lasern mit geringfügig unterschiedlichen Wellenlängen gepumpt. Dadurch kommt es zur Zweiphotonenabsorption, die wiederum zur Emission von zwei Photonen mit der Mittenwellenlänge führt. So entsteht ein gepulstes Signal, dessen Phase unter bestimmten Bedingungen bi-stabil, also innerhalb eines Pulses konstant ist und nur zwei gegenphasige Zustände annehmen kann. Durch optische Überlagerung zweier aufeinanderfolgender Pulse entsteht so das Zufallssignal.

![Abb. 2: Grundkonzept der PPU des Schlüsselgenerators mit 1x16-Splitter, 16 steuerbaren Phasenschiebern und einem Speckle-MMI als PUF [12] Abb. 2: Grundkonzept der PPU des Schlüsselgenerators mit 1x16-Splitter, 16 steuerbaren Phasenschiebern und einem Speckle-MMI als PUF [12]](/images/stories/Abo-2024-03/plus-2024-03-067.jpg) Abb. 2: Grundkonzept der PPU des Schlüsselgenerators mit 1x16-Splitter, 16 steuerbaren Phasenschiebern und einem Speckle-MMI als PUF [12]

Abb. 2: Grundkonzept der PPU des Schlüsselgenerators mit 1x16-Splitter, 16 steuerbaren Phasenschiebern und einem Speckle-MMI als PUF [12]

2. Design

Ziel des Projektes ist es eine Plattform zu entwickeln, die, wie in Abbildung 1 dargestellt, in der Lage ist, möglichst viele optische und elektrische Komponenten zu verbinden. Da kommerziell verfügbare Komponenten sowie solche, die innerhalb des Projektes entworfen und intern oder extern gefertigt werden, zum Einsatz kommen, soll die Plattform möglichst flexibel gestaltet sein. Trotzdem müssen gewisse Entwurfsregeln definiert werden, um das Zusammenspiel der Komponenten und Prozesse zu ermöglichen.

2.1. ‚SILHOUETTE'-Plattform

Entwurfsregeln für die ,SILHOUETTE'-Plattform:

- Festlegung auf 1550 nm als optische Wellenlänge (meistgenutzt in der integrierten Photonik)

- 127 µm optischer I/O Pitch passend zu Standardfaserarrays

- Möglichst alle notwendigen Systemelemente auf Interposer integrieren (elektrische Signalintegrität und möglichst wenige optische Kontakte für geringen Verlust)

Verschiedene Montagetechniken kombinieren:

- Drahtbonden für externe Bauelemente ohne Lötbumps

- Reflowlöten

- Thermokompressionsbonden für intern gefertigte Bauelemente.

- Eingänge der PICs möglichst auf 3,3 V und 40 mW begrenzen (typ. Ausgangsleistung ASIC)

- Kompatibilität aller Prozesse in möglichst kleinen Blöcken prüfen.

Zur Umsetzung wird ein konventioneller Siliciuminterposer mit einer polymeren optischen Umverdrahtungslage (engl.: re-distribution layer RDL) erweitert. Diese liefert eine optische Umverdrahtung in der Ebene sowie die Oberflächenkopplung über µ-Spiegel zu den Fasergitterkopplern (FGC) der PICs. Die Ausrichtung zwischen diesen beiden Elementen ist für einen geringen Koppelverlust kritisch. Um diese Verluste möglichst gering zu halten, werden zwei Montagetechniken getestet, einerseits Reflowlöten mit Selbstausrichtung zwischen Lötbump und Lötpad und andererseits Thermokompressionsbonden.

Um das Co-Design der unterschiedlichen Komponenten der Plattform effizient zu gestalten, müssen die einzelnen Entwurfsregeln und Technologiegrenzen in Tabelle 1 beachtet werden. Die elektrischen RDLs auf Interposer und PIC sind weitestgehend identisch. Bei ersterem ist sie durch den polymeren Wellenleiterstapel bedeckt, während sie bei zweiterem auf dem oberen Oxid der SiN-Wellenleiter abgeschieden wird. Da die Schichtdicke aufgrund der geringen Abscheiderate begrenzt ist, können sich Wellenleiter und elektrische RDL auf dem PIC nicht kreuzen, während dies auf dem Interposer möglich ist. In beiden Fällen dürfen sich elektrische und optische Kontakte nicht überlappen. Zusätzlich muss auf dem Interposer der Wellenleiterstapel für einen elektrischen Kontakt vollständig geöffnet sein, Wellenleiterkerne müssen mindesten 20 µm Abstand zu diesen Öffnungen haben. Zentral für das Co-Design ist die große Diskrepanz im Pitch der optischen Kontakte. Diese muss der Interposer durch ein optisches Fan-Out adressieren, wobei der kritische Krümmungsradius aufgrund der geringen numerischen Apertur der Wellenleiter der limitierende Faktor ist. Auf dem PIC hingegen sind durch den hohen Indexkontrast im SiN/SiO2-Materialsystem ein deutlich engeres Routing und somit eine hohe optische Integrationsdichte sowie geringere Fläche und damit geringere Kosten pro Chip möglich.

|

Parameter\Struktur |

Interposer - optische RDL |

Interposer/ PIC - elektrische RDL |

PIC – optische RDL |

|

Min. Linienbreite/ -abstand |

5-8 μm / 20 μm |

10 μm / 10 μm |

0.5-1 μm / 5 μm |

|

Kontaktgröße |

20 μm x 20 μm |

⌀ 80 μm Lötbumps 90 µm x 160 µm TC-Bonden |

25 μm x 40 μm |

|

Verlust / Kontakt |

≈ 1 dB |

- |

≈ 7 dB |

|

1dB Krümmungsverlustradius |

7 mm |

- |

10 μm |

|

Min. IO-Pitch |

20 μm (μ-Spiegel Reihe), 127 μm (Faserarray), 250 μm (PD Doppelreihe) |

100 μm (Lötbump/TC-Bonden), 60 μm → 30 μm (Drahtbonden in Doppelreihe) |

20 μm (FGC-Reihe) |

2.2. Interposer

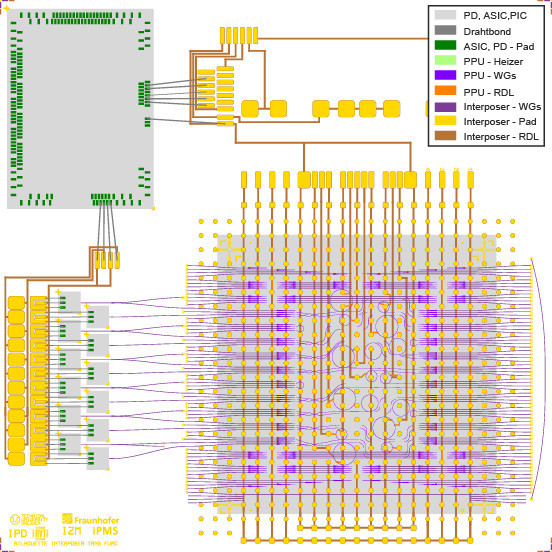

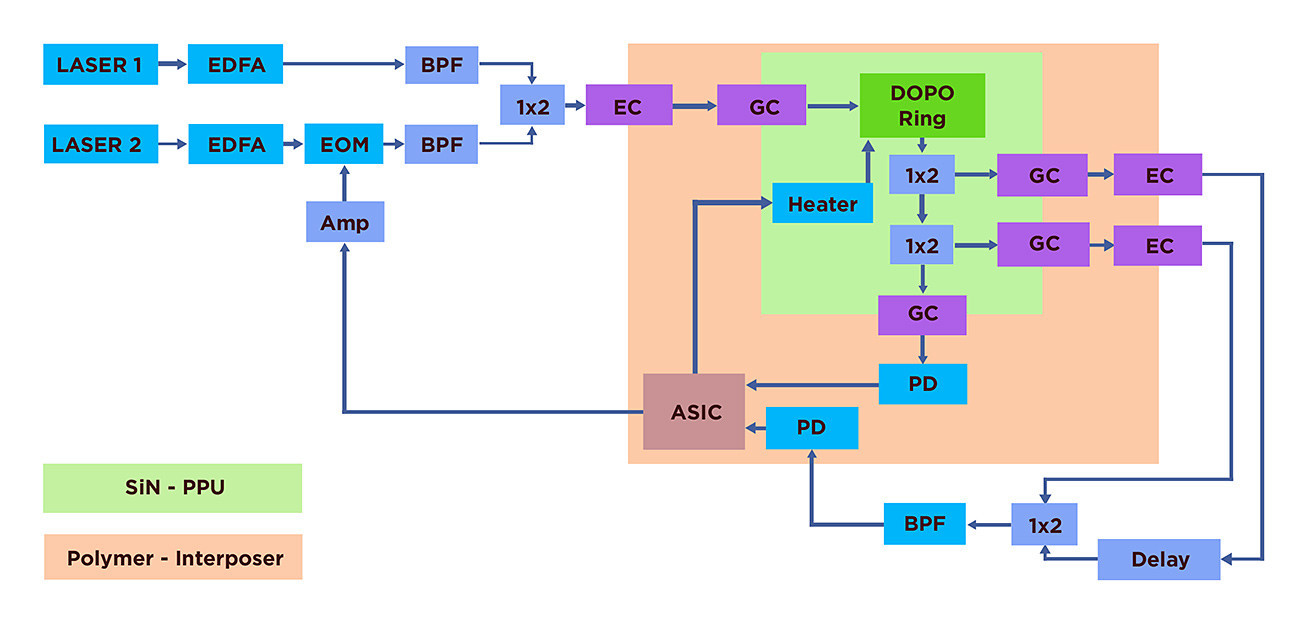

Für die beiden Interposerlayouts für die Varianten TRNG und K-MMI in Abbildung 3 ist diese Limitation verschieden adressiert. Da für den TRNG Lötbumps mit Selbstausrichtung beim Reflowlöten für die Montage verwendet werden, die sowohl für den Abscheidungsprozess als auch für die Selbstausrichtung regelmäßig angeordnet seien müssen, ist ein Gitter mit 254 µm Pitch gewählt worden, sodass pro Reihe zwei Kanäle über 45° µ-Spiegel mit einem 127 µm Faserarray gekoppelt werden können. Auf einer Seite stehen damit bis zu 32 Kanäle zur Verfügung. Für Testzwecke können zusätzliche 32 Kanäle durch Verschieben des Arrays um den halben Pitch gekoppelt werden. Der Pitch von 63,5 µm am Ausgang des Interposers wird dann auf 35 µm unter dem PIC reduziert, um zwischen die elektrischen Kontakte zu passen. Zusätzliche optische Daisy-Chains mit verschiedener Anzahl von Koppelstrukturen befinden sich ebenfalls auf dem PIC. In der Mitte sind insgesamt 16 TRNGs angeordnet, wobei 12 jeweils mit zwei Photodioden verbunden sind. Das Ausgangssignal der TRNGs wird auf dem PIC in Referenz- und 2 Halbsignale geteilt. Ein Halbsignal wird vom Interposer in eine Faserverzögerungschleife und zurück zum Interposer gekoppelt (siehe Blockdiagramm in Abbildung 4). Durch die Mischung beider Halbsignale auf dem Interposer entsteht das binäre Zufallssignal.

Auf den KMMI-PICs befindet sich jeweils ein KMMI pro Chip. Dessen Eingang, die 16 Ausgänge sowie zusätzliche Testsignale zur Ausrichtung können in einer Reihe mit 32 Kopplern und 127 µm Abstand an der oberen Kante des Chips gekoppelt werden. Von den 32 Signalen wird eine Hälfte mittels 45° µ-Spiegeln an ein Faserarray bzw. die PDs gekoppelt. Die gewählte Montagetechnologie Thermokompressionsbonden mit Studbumps ermöglicht eine freiere Anordnung, sodass optische und elektrische Kontakte hier räumlich getrennt werden können, solange eine stabile Auflage des Chips gegeben ist.

Abb. 3: Layoutentwurf des Interposers für TRNG (links) und K-MMI (rechts) mit jeweils dem ASIC oben links und den PICs auf der rechten Seite. Für den TRNG befindet sich ein PD-Array links des Chips, für den K-MMI oberhalb.

Abb. 4: TRNG Blockdiagramm: EDFA - Erbiumfaserverstärker; EOM – Elektro-optischer Modulator ; Amp – Elektrischer Verstärker; BPF - Bandpassfilter (optisch); 1x2 – Optischer Splitter; EC – Kopplung Interposer - Faser; GC – Kopplung Interposer Chip; PD - Photodiode; Delay - Faserverzögerungsschleife

Abb. 4: TRNG Blockdiagramm: EDFA - Erbiumfaserverstärker; EOM – Elektro-optischer Modulator ; Amp – Elektrischer Verstärker; BPF - Bandpassfilter (optisch); 1x2 – Optischer Splitter; EC – Kopplung Interposer - Faser; GC – Kopplung Interposer Chip; PD - Photodiode; Delay - Faserverzögerungsschleife

2.3. Zufallszahlengenerator (TRNG)

Abbildung 4 zeigt das Blockdiagramm für den TRNG. Herzstück ist dabei der degenerierte optische parametrische Ringoszillator (DOPO). Dieser wird über Faserkopplung und den Interposer von zwei kohärenten Laserquellen gespeist, von denen eine moduliert ist, um die Taktung des Signals einzustellen. Oberhalb einer Leistungsschwelle entsteht ein Signal mit bi-stabiler Phase, welches durch Überlagerung mit einem Folgesignal zur Generierung des Zufallssignals verwendet wird. Die Leistungsschwelle ist hierbei insbesondere von der Dämpfung innerhalb des Rings abhängig. Um diese unter 100 mW zu halten, muss die Dämpfung auf unter 0.5 dB/cm optimiert werden [11]. Nur so kann die Zuleitung über die Polymerwellenleiter unterhalb ihrer Zerstörungsschwelle erfolgen. Zusätzlich muss der Verlust durch die Gitterkoppler möglichst gering gehalten werden.

Die maximale Taktrate wird durch die Abschwingzeit des Ringoszillators bestimmt. Durch die Integration auf einem Substrat mit dem ASIC können sowohl die Abschwingzeit als auch die Temperatur der Ringe über Heizer eingestellt werden, um Signaldrift zu verhindern.

2.4. Krypto-Multimodeinterferometer (K-MMI)

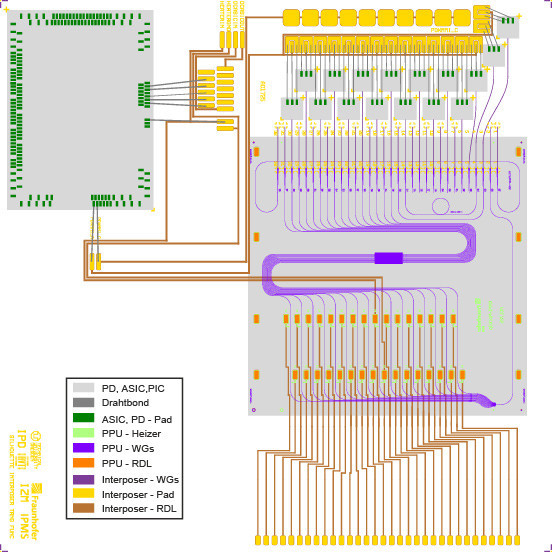

Das K-MMI wird, wie in Abbildung 5 dargestellt, von einem Laser optisch gespeist und durch eine Elektronik angesteuert, um das von der PPU ausgespeiste optische Signal mittels Fotodioden und zugehöriger Elektronik als elektrisches Ausgangssignal zurückzugeben. Das elektrische Ansteuersignal repräsentiert hierbei den öffentlichen Schlüssel und das elektrische Ausgangssignal den privaten. Die Berechnung erfolgt auf dem optischen Weg. Hierzu wird das in die PPU eingespeiste optische Signal durch einen Splitter auf mehrere Wellenleiter aufgeteilt und das elektrische Ansteuersignal durch die Phasenschieber optisch codiert. Die Wellenleiter münden in ein Speckle-Multimodeinterferometer (Speckle-MMI), welches das phasencodierte Signal am Eingang in ein quasi zufälliges Signal am Ausgang überführt. Das Speckle-MMI ist die PUF und besteht aus einem MMI, welches durch eine zusätzlich eingebrachte zufällige Oberflächentopologie ein nicht vorhersagbares Interferenzmuster an dessen Ausgang erzeugt, das von der Phase am Eingang abhängt. Abschließend wird das Interferenzmuster durch Wellenleiter abgegriffen und ausgespeist. Die Vorteile dieses Konzeptes sind die Fertigbarkeit auf unterschiedlichen Photonik-Plattformen, wie z. B. Silicium, Siliciumnitrid oder Lithiumniobat und die breite Auswahl an Wirkprinzipien für die elektro/optische Signalwandlung, wie z. B. elektro-, thermo- oder stressoptisch. Um den Randbedingungen zu genügen und perspektivisch die PPU auch im sichtbaren Spektralbereich einsetzen zu können, wird eine Siliciumnitrid-Plattform verwendet. Zur Ein- und Auskopplung der optischen Signale werden Gitterkoppler genutzt, die in einem Winkel von 8° zur Senkrechten der PPU-Ebene abstrahlen. Mikro-Elektro-Mechanische Systeme (MEMS) bilden die Grundlage für die MEMS-Phasenschieber, welche im Vergleich zu thermischen Phasenschiebern eine um mehrere Größenordnungen geringere elektrische Leistungsaufnahme besitzen und kein Übersprechen zeigen. Die MEMS-Phasenschieber sind Gegenstand der aktuellen Entwicklung am Fraunhofer IPMS. Um bereits die Eignung der Aufbau- und Verbindungstechnik nachzuweisen, wurde eine Mockup-Version entworfen und gefertigt, welche bis hin zur Position der Bondpads bereits dem Ziellayout entspricht, jedoch anstelle der MEMS-Phasenschieber thermische Versionen besitzt [12].

![Abb. 5 mit einem 32 Kanal Gitterkoppler-Array, einem 1x16-Sternkoppler, 16 thermischen Phasenschiebern und einem MMI; Pfeile kennzeichnen den optischen Signalweg [12] Abb. 5 mit einem 32 Kanal Gitterkoppler-Array, einem 1x16-Sternkoppler, 16 thermischen Phasenschiebern und einem MMI; Pfeile kennzeichnen den optischen Signalweg [12]](/images/stories/Abo-2024-03/plus-2024-03-032.jpg) Abb. 5 mit einem 32 Kanal Gitterkoppler-Array, einem 1x16-Sternkoppler, 16 thermischen Phasenschiebern und einem MMI; Pfeile kennzeichnen den optischen Signalweg [12]

Abb. 5 mit einem 32 Kanal Gitterkoppler-Array, einem 1x16-Sternkoppler, 16 thermischen Phasenschiebern und einem MMI; Pfeile kennzeichnen den optischen Signalweg [12]

2.5. Applikationsspezifischer integrierter Schaltkreis (ASIC)

Der ASIC steuert und überwacht den ,SILHOUETTE'-Demonstrator. Die Stromsignale der PDs werden mittels Transimpedanzverstärkern in Spannungen gewandelt und dann verarbeitet, damit die Schlüssel bzw. das Zufallssignal einem RISC-V-Prozessorkern (EMSA5) zur Verfügung stehen. Dieser stellt die notwendige Flexibilität bereit, um sich an die verschiedenen Nutzungsfälle und Protokolle für das System anzupassen. Über Ausgänge werden zusätzlich die Heizer im TRNG gesteuert und überwacht sowie der öffentliche Schlüssel an die Phasenschieber des K-MMI weitergegeben. Der Chip mit einer Größe von 3,9 x 2,9 mm2 wurde extern im 28-nm-1-poly-9-Metal-Technologieknoten gefertigt. Über einen Doppelpadring und Drahtbonden werden der Interposer sowie eine Vielzahl von Testsignalen direkt zum unterliegenden PCB kontaktiert.

3. Prozesstechnologie

In diesem Abschnitt wird die Fertigung des Interposers sowie des TRNG mit Fokus auf die Adaptionen für die ‚SILHOUETTE'-Plattform erläutert. Außerdem werden die Ergebnisse des Thermokompressionsbondens mit dem Mock-up-K-MMI vorgestellt.

3.1. Interposer

Der Interposer ist das zentrale Element der ‚SILHOUETTE'-Plattform und ermöglicht die optische und elektrische Kommunikation der Komponenten sowie die mechanische Verbindung über geeignete Kontaktstellen. Als elektromechanische Struktur werden eine Kupfer-RDL mit 10 µm Linienabstand und -weite und ein Kupfer-Nickel-Gold-Padaufbau verwendet. Beide sind durch eine SiO2-Passivierung abgedeckt, die unterhalb der Pads durch Trockenätzen geöffnet wird. Die Padstrukturen sind neben der elektrischen Verbindung insbesondere für die mechanische Ausrichtung kritisch. Beim Reflowlöten zentrieren sich die Lötdepots des TRNG selbstständig auf den Pads des Interposers. Insofern ist hier kritisch, dass die optischen Lagen auf beiden Verbindungspartnern möglichst geringen Versatz zur Padlage haben. Hierfür wurden interposerseitig die Ausrichtungsmarken für die optischen Lagen und die spätere Montage in die Padlage integriert, um ein Aufsummieren der Ausrichtungstoleranzen zu verhindern. Die Fertigung der elektrischen Lagen erfolgt in einer etablierten 8“-Produktionslinie für Interposer. Das Hauptaugenmerk liegt also auf der Kompatibilität zur neu entwickelten polymeren RDL.

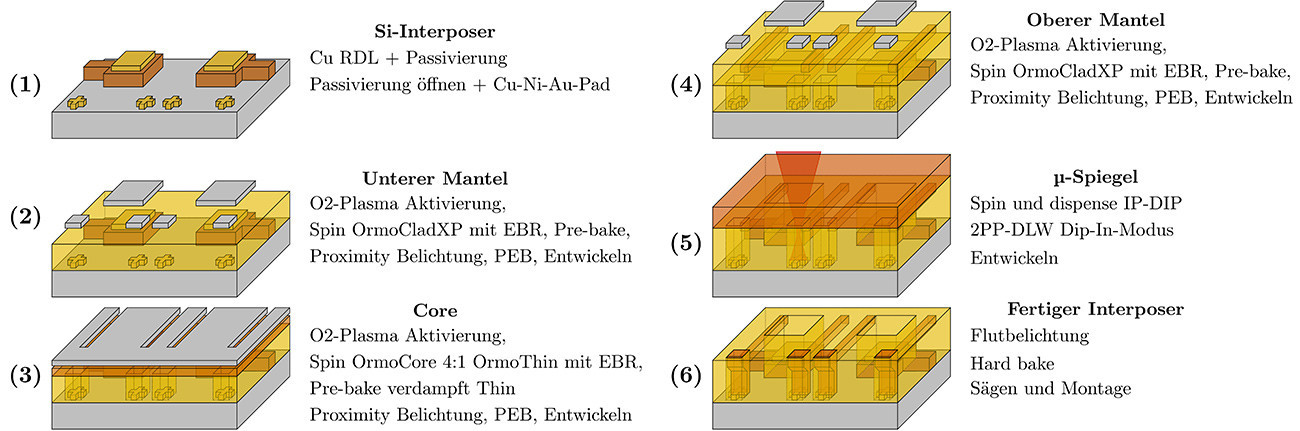

In [13, 14, 15, 16] ist die Entwicklung von Schichtaufbau und Prozess für das neu entwickelte polymere optische RDL beschrieben. Abbildung 6 zeigt die Prozessfolge, um zunächst den 3-lagigen Wellenleiterstapel und anschließend die µ-Spiegel mittels 2-Photononenpolymerisations-Laserdirektschreiben (2PP-DLW) herzustellen. Da das verwendete Lacksystem OrmoCore/Clad nach dem Belacken noch klebrig ist, wird die Proximitybelichtung mit Abstandshaltern auf den Wafern oder zum Einschwenken zwischen Maske und Wafer verwendet. So kann der für hohe Kantensteilheit und Auflösung erforderliche geringe Belichtungsabstand von 20-50 µm eingestellt werden.

Abb. 6: Schematische Prozessfolge zur Herstellung der polymeren optischen RDL und µ-Spiegel auf Si-Interposer mit Cu-RDL und Pads

Abb. 6: Schematische Prozessfolge zur Herstellung der polymeren optischen RDL und µ-Spiegel auf Si-Interposer mit Cu-RDL und Pads

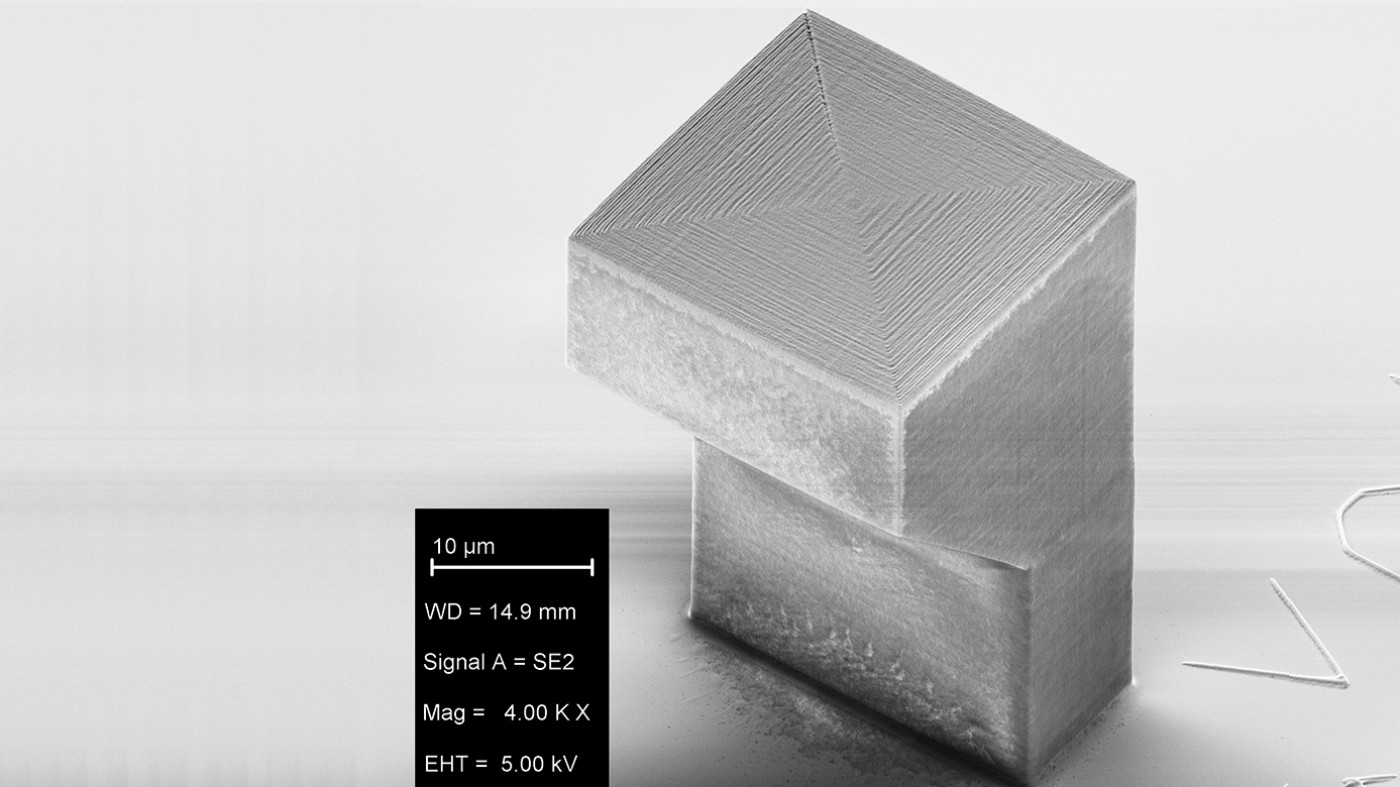

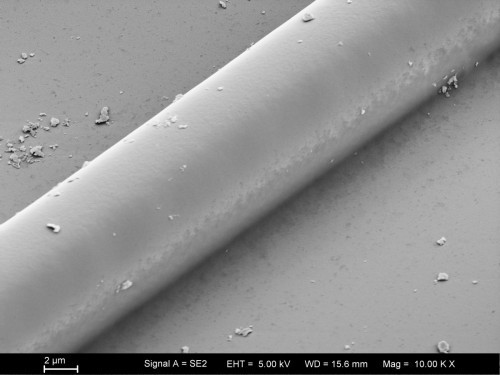

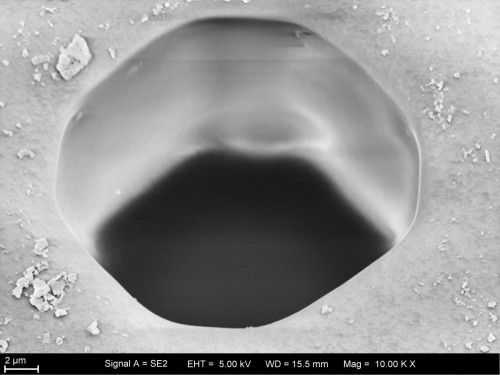

Um die Kompatibilität mit dem Si-Interposer zu zeigen, wurden zunächst Haftungs- und Planarisierungstests durchgeführt. Diese haben gezeigt, dass ein 27 µm dicker unterer Mantel die Topografie der elektrischen Strukturen glätten kann. Anschließend werden dann Kern und oberer Mantel identisch aufgetragen, sodass sich die Gesamtdicke des Stapels von 55 µm ergibt. Die Kernlage definiert dabei die Lichtwellenleiter, während beide Mäntel mit identischem Layout die Öffnungen für µ-Spiegel und die elektrischen Verbindungen enthalten.Um die hohe Flankensteilheit und glatten Seitenwände in Abbildung 7 zu erzielen, wird eine UV-LED-Quelle mit zwei Wellenlängen und kollimiertem Strahl verwendet. Durch das breite Spektrum können Stehwelleneffekte, die bei vorherigen Tests mit i-Linien-Hg-Quelle auftraten, vermieden werden. In diese Öffnungen werden dann mittel 2PP-DLW die µ-Spiegel zur Strahlumlenkung integriert. Hierzu wird ein 780 nm Laser durch ein Mikroskopobjektiv fokussiert und dieses in einen Tropfen IP-Dip-Resist auf dem Substrat getaucht. Aufgrund der Zweiphotonenabsorption ist die Vernetzung proportional zum Quadrat der Intensität, sodass nur im Fokusvolumen in der Größenordnung von 1 µm3 die Vernetzungsdosis überschritten wird. Mittels Galvanikspiegeln und Piezomanipulatoren wird das Fokusvolumen durch das Resist bewegt und somit die 3D-µ-Spiegelstruktur erzeugt. Ein Spiegel, wie zu Beginn dieses Artikels beispielhaft freistehend gezeigt, kann in unter 10 Sekunden mit einer unkritischen Rauheit von unter 30 nm geschrieben werden [14]. Um die Spiegel mit sub-µm-Versatz zu drucken, ist auf dem Interposer jeweils ein Satz Ausrichtungsmarken pro Spiegel integriert, der über die Inlinekamera registriert wird. Aufgrund der seriellen Natur des Verfahrens ist es außerdem möglich, die µ-Spiegel schnell an unterschiedlichste Koppelszenarien anzupassen.

Abb. 7: Beste Ergebnisse für Wellenleiterkerne (links) und Mantelöffnungen (rechts) mit 365 nm und 405 nm

Biwellenlänge-UV-LED-Belichtungsquelle

3.2. TRNG

Für die Strukturierung der optischen Schichten auf dem TRNG wird Elektronenstrahllithografie mit einer Auflösungsgrenze von 50 nm verwendet. Insbesondere die FGCs sowie die Koppelstellen zu den Ringresonatoren benötigen diese hohe Auflösung. Das SiN wird dabei mittels Trockenätzen strukturiert, wobei aufgrund der hohen Schichtdicke von 690 nm eine TiN-Hartmaske verwendet wird. Abgeschieden werden zunächst der SiO2-Mantel und dann die SiN-Kernschicht mittels plasmaunterstützter chemischer Gasphasenabscheidung (PECVD) bei 400 °C mit SiH4 und N2O bzw. SiH4 und NH3. Um eine geringe Dämpfung im Nahinfrarotbereich zu realisieren, müssen im Anschluss durch Temperaturbehandlung die restlichen Wasserstoffverbindungen entfernt werden [17]. Hierzu wird der Wafer unter Stickstoffatmosphäre auf 1100 °C gebracht. Insbesondere auf 300-mm-Wafern stellt die Schichtspannung eine Herausforderung dar. Um 690 nm SiN auf 2 µm SiO2 mit geringer Spannung abzuscheiden, müssen die Abscheideparameter und die Temperaturbehandlung angepasst werden. Nach dem Trockenätzen der Wellenleiter werden diese mit 1 µm SiO2 bedeckt. Um die Mikroringe thermisch regeln zu können, müssen Heizer aufgebracht werden, die sowohl einen geeigneten Schichtwiderstand haben als auch in ihrer Prozessierung kompatibel zu den Wellenleiterschichten sind. Hierzu wird TiN verwendet. Im Anschluss werden dann analog zum Interposer eine Cu-RDL und Cu-Ni-Au Pads aufgetragen. Diese werden dann mit SnAg-Lötbumps, für die spätere Flip-Chip Montage und das Reflowlöten, abgeschieden. Auch hier ist ein geringer Versatz zwischen den Wellenleitern und optischen Kopplern sowie den Lötbumps, die die mechanische Verbindung herstellen, essentiell.

3.3. Thermokompressionsbonden

Die Prozessierung des K-MMI-PICs verläuft ähnlich, wobei Thermokompressionsbonden als Montageverfahren verwendet wird und daher keine Lötbumps abgeschieden werden. Da sich der ‚SILHOUETTE'-Interposer derzeit noch in der Entwicklung befindet, wird für erste Tests die in Abbildung 8 dargestellte Mockup-Version verwendet. Die Gitterkoppler entsprechen denen der PPU und die Lage der Bondpads ist für die Flip-Chip-Montage um die Längsachse zur PPU gespiegelt. Die Bondpads des Mockup und der PPU bestehen aus einer Aluminiumlegierung (AlSiCu), weswegen sowohl auf den Bondpads des Interposers als auch auf denen des PICs Gold-Stud-Bumps aufgebracht werden. Hierbei ist zu beachten, dass durch den Abstrahlwinkel des Gitters ein Versatz der PPU gegenüber dem Interposer einzustellen ist, der vom Abstand zwischen PPU und Interposer abhängt. Die Verwendung außermittig platzierter Studbumps erlaubt, hier flexibel zu reagieren. Aufgrund der Padgeometrien musste interposerseitig ein Stack bestehend aus zwei Studbumps realisiert werden, um für den angestrebten Abstand von 60 μm ausreichend Material vorzulegen. Auf der Seite der PPU genügte ein breiterer und zusätzlich gecointer Stud-Bump, um hier die Lagetoleranz zu erhöhen. Nach dem Setzen der Stud-Bumps auf beiden Komponenten wird die PPU face down zum Interposer ausgerichtet, sodass die Studs mittig miteinander verbunden werden können. Dies geschieht bei einer Temperatur von ca. 250 °C und einem Druck von ca. 250 MPa, bezogen auf die Kontaktfläche der Stud-Bumps. Durch die Wahl der Bondparameter wird zusätzlich die finale Höhe zwischen den Komponenten bestimmt.

![Abb. 8: Schematische Darstellung des Bond-Prozesses mit zwei gestapelten Stud-Bumps auf dem Mock-UpInterposer und einem größeren gecointen Stud-Bump auf der PPU [12] Abb. 8: Schematische Darstellung des Bond-Prozesses mit zwei gestapelten Stud-Bumps auf dem Mock-UpInterposer und einem größeren gecointen Stud-Bump auf der PPU [12]](/images/stories/Abo-2024-03/plus-2024-03-073.jpg) Abb. 8: Schematische Darstellung des Bond-Prozesses mit zwei gestapelten Stud-Bumps auf dem Mock-UpInterposer und einem größeren gecointen Stud-Bump auf der PPU [12]

Abb. 8: Schematische Darstellung des Bond-Prozesses mit zwei gestapelten Stud-Bumps auf dem Mock-UpInterposer und einem größeren gecointen Stud-Bump auf der PPU [12]

Zusammenfassung und Ausblick

Die vorgestellte SILHOUETTE-Plattform ist nach unserem Wissen der erste hybride System–in-Package-(SiP)-Ansatz, der photonische Schaltkreise, Photo- und Laserdioden sowie ASICs auf einem Substrat vereint. Hierzu ist es insbesondere wichtig, die Komponenten und Prozesse aufeinander abgestimmt zu entwickeln. In den Bereichen polymere Wellenleitertechnik, SiN-Abscheidung und Strukturierung auf 300 mm Wafer sowie Thermokompressionsbonden konnte der Stand der Technik erweitert werden.

Trotzdem gilt es, im Projektverlauf die beiden Wellenleitersysteme weiter zu verbessern. Im Anschluss müssen die Plattform vollständig aufgebaut und die elektrische sowie optische Funktion gezeigt werden. Die Technologie kann danach für andere Anwendungen geöffnet werden, um eine universelle Plattform für optische und hybride SiP-Systeme zu schaffen.

Die Arbeiten werden durch das Bundesministerium für Bildung und Forschung (BMBF) im Projekt ,SILHOUETTE' unter der Fördernummer 16ME0313K gefördert. Die Autoren danken dem beteiligten wissenschaftlichen und technischen Personal an der TU Dresden (Markus Göhler, Menglong He, Ilias Sotiriou), dem Fraunhofer IPMS (Qamber Abbas, Margarita Lapteva, Meysam Namdari, Vinya Vibhuti, Christopher Zschorn) und dem Fraunhofer IZM (Karin Kutyma, Maximilian Wagner) für ihre Unterstützung. Dieser Beitrag beruht auf zwei Veröffentlichungen des Konsortiums beim Mikrosystemtechnikkongress 2023 in Dresden [5, 12].

Literaturverzeichnis

[1] L. Feng, M. Zhang, J. Wang, X. Zhou, X. Qiang, G. Guo und X. Ren, ‚Silicon photonic devices for scalable quantum information applications', Photon. Res., Bd. 10, p. A135–A153, October (2022)

[2] N. Margalit, C. Xiang, S. M. Bowers, A. Bjorlin, R. Blum und J. E. Bowers, ‚Perspective on the future of silicon photonics and electronics', Applied Physics Letters, Bd. 118, p. 220501, June (2021)

[3] M. Teng, A. Honardoost, Y. Alahmadi, S. S. Polkoo, K. Kojima, H. Wen, C. K. Renshaw, P. LiKamWa, G. Li, S. Fathpour, R. Safian und L. Zhuang, ‚Miniaturized Silicon Photonics Devices for Integrated Optical Signal Processors', Journal of Lightwave Technology, Bd. 38, pp. 6-17, (2020)

[4] L. Carroll, J.-S. Lee, C. Scarcella, K. Gradkowski, M. Duperron, H. Lu, Y. Zhao, C. Eason, P. Morrissey, M. Rensing, S. Collins, H. Y. Hwang und P. O’Brien, ‚Photonic Packaging: Transforming Silicon Photonic Integrated Circuits into Photonic Devices', Applied Sciences, Bd. 6, (2016)

[5] D. Weyers, M.-T. Catuneanu, M. Lapteva, V. Vibhuti, M. He, S. Böhnhardt, M. Landwehr, J. N. K. Fell, K. Jamshidi und K. Bock, ‚Electro-optical co-integration platform for high-density hybrid systems – SILHOUETTE (Im Druck)', Mikrosystemtechnik Kongress Dresden, (2023)

[6] F. Pavanello, I. O’Connor, U. Rührmair, A. Foster und D. Syvridis, ‚Recent Advances in Photonic Physical Unclonable Functions', IEEE European Test Symposium (ETS), (2021)

[7] A. Alkassar, T. Nicolay und M. Rohe, ‚Obtaining True-Random Binary Numbers from a Weak Radioactive Source', in Computational Science and Its Applications – ICCSA 2005, Berlin, (2005)

[8] C. Li, Q. Wang, J. Jiang und N. Guan, ‚A metastability-based true random number generator on FPGA', in 2017 IEEE 12th International Conference on ASIC (ASICON), (2017)

[9] N. Rangarajan, A. Parthasarathy und S. Rakheja, ‚A spin-based true random number generator exploiting the stochastic precessional switching of nanomagnets', Journal of Applied Physics, Bd. 121, p. 223905, June (2017)

[10] Y. Okawachi, M. Yu, K. Luke, D. O. Carvalho, M. Lipson und A. L. Gaeta, ‚Quantum random number generator using a microresonator-based Kerr oscillator', Opt. Lett., Bd. 41, p. 4194–4197, September (2016)

[11] M. H. a. K. Jamshidi, ‚Conditions for dual-pumped optical parametric oscillation in silicon nitride ring cavities', IEEE Photonics Conference (IPC), (2022)

[12] M. Blasl, M. Namdari, J. Fröhlich und H. Oppermann, ‚Herstellung zuverlässiger elektrischer und optischer Verbindungen für Siliciumnitrid-Photonik mittels Thermokompressionsbonden', Mikrosystemtechnik Kongress Dresden, (2023)

[13] D. Weyers, K. Nieweglowski, L. Lorenz und K. Bock, ‚Analysis of polymeric singlemode waveguides for inter-system communication', in 2021 23rd European Microelectronics and Packaging Conference & Exhibition (EMPC), (2021)

[14] D. Weyers, K. Nieweglowski und K. Bock, ‚Hybrid lithography fabrication of single mode optics for signal redistribution and coupling', in 2023 24rd European Microelectronics and Packaging Conference & Exhibition (EMPC), (2023)

[15] D. Weyers, K. Nieweglowski und K. Bock, ‚Advances in UV-lithographic patterning of multi-layer waveguide stack for single mode polymeric RDL', in 2022 IEEE 9th Electronics System-Integration Technology Conference (ESTC), (2022)[16] D. Weyers, A. Mistry, K. Nieweglowski und K. Bock, ‚Hybrid lithography approach for single mode polymeric waveguides and out-of-plane coupling mirrors', in Proc. of IEEE 72nd Electronic Components and Technology Conf. (ECTC), San Diego, CA, USA, (2022)

[17] F. L. Martinez, A. Del Prado, I. Mártil, G. González-Diaz, W. Bohne, W. Fuhs, J. Röhrich, B. Selle und I. Sieber, ‚Molecular models and activation energies for bonding rearrangement in plasma-deposited a- SiN x: H dielectric thin films treated by rapid thermal annealing', Physical Review B, Bd. 63, p. 245320, (2001)