So geht Halbleiter-Forschungsdirektorin Emilie Jolivet vom französischen Marktanalyse-Unternehmen Yole davon aus, dass der Markt für Chip-Packaging von 44,3 Mrd. $ Umsatz im Jahr 2022 bis zum Jahr 2028 auf 78,6 Mrd. $ Dollar steigt – bei jährlichen Wachstumsraten um die 10 %. Im Teilmarkt für 2,5D- und 3D-Packaging sei jedoch sogar mit jährlichen Zuwachsraten um die 30 % zu rechnen. Gerade das Spitzensegment wird hier allerdings bisher von nur wenigen Akteuren beherrscht. Dazu gehören TSMC, Samsung, Intel, Hynix und die hierzulande wenig bekannte chinesische Gruppe YMTC. Bei etwas einfacher gestrickten Übergangstechnologien (2,5D) sind auch Amkor, UMC und weitere Unternehmen mit im Geschäft.

Europa wiederum forscht zwar auch an 3D-, 2,5D- und Chiplet-Technologien, beispielsweise im belgischen Imec, im französischen CEA-Leti oder in den Fraunhofer-Einrichtungen Assid und EAS in Dresden. Doch eine eigene Massenproduktion im 3D-Packaging-Segment gibt es in Europa nicht. Diese Lücke versucht übrigens auch der ‚European Chips Act' ein Stück weit zu schließen.

„3D-Architekturen werden die Grenzen des Machbaren insbesondere für Künstliche Intelligenz hinausschieben“

Emilie Jolivet, Semiconductor, Memory and Computing Division Director, Yole Group

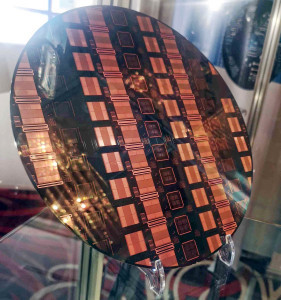

Auch das Fraunhofer-Zentrum Assid zeigte Wafer mit 3D-integrierten Schaltkreisen am Rande der Semi-Konferenz in DresdenDen Anschluss in der 3D-Integration heterogener Schaltkreise und Chiplets zu gewinnen, entwickelt sich dabei immer mehr zu einem Schlüsselthema bei der Debatte um digitale Souveränität und Wettbewerbsfähigkeit der konkurrierenden Hochtechnologie-Standorte weltweit.

Auch das Fraunhofer-Zentrum Assid zeigte Wafer mit 3D-integrierten Schaltkreisen am Rande der Semi-Konferenz in DresdenDen Anschluss in der 3D-Integration heterogener Schaltkreise und Chiplets zu gewinnen, entwickelt sich dabei immer mehr zu einem Schlüsselthema bei der Debatte um digitale Souveränität und Wettbewerbsfähigkeit der konkurrierenden Hochtechnologie-Standorte weltweit.

„Heterogene Integration fördert die nächsten Wachstumsschritte der Halbleiterindustrie“, meint auch Vizepräsidentin Rozalia Beica von AT&S. Sie rechnet sogar mit einer ganz „neuen Ära der Mikroelektronik“. Und Heiko Dudek von Siemens EDA ist überzeugt: „Die Vorteile, die sich aus der heterogenen Integration von Chiplets ergeben, führen zu einer dramatisch steigenden Nachfrage in immer mehr Märkten und Applikationen.“

Hintergrund: War in der Anfangszeit der Mikroelektronik das Moorsche Gesetz noch recht mühelos einzuhalten, laut dem sich die Transistor-Dichte in Schaltkreisen etwa alle anderthalb Jahre verdoppelt, so ist dieser Pfad hin zu mehr Rechenleistung mittlerweile extrem aufwendig und teuer geworden. All dies hat den Fokus der Industrie ein Stück weit von den Kernprozessen der Chipfertigung (Frontend) hin zu neuen Verpackungs-, Kontaktier- und Endmontagetechnologien (Backend beziehungsweise Packaging) für Schaltkreise gelenkt, hin zu Konzepten wie ‚Chiplets', 3D- und 2,5D-Integration. Dabei werden beispielsweise unterschiedliche Schaltkreise, Sensoren, analoge Elemente und andere Funktionsblöcke dicht neben- oder übereinander zusammenfügt, durchkontaktiert und dann wie ein Computerchip in einem Gehäuse verpackt. Das können beispielsweise ein oder mehrere Zentralrechnerkerne (CPUs), Grafikprozessoren (GPUs), aber auch Speicher und Kommunikations-Bausteine sein. Beispiele dafür sind der ‚Ryzen' von AMD, der ‚Meteor Lake' von Intel, der bei TSMC produzierte ‚M1 Ultra' von Apple oder der chinesische Kryptoschürfer-Chip ‚Jasminer X4'.

Höhere Ausbeute bei kleineren Einzel-Dies

Teils steht beim Einsatz solcher Techniken die Kostenfrage im Mittelpunkt. Denn die 2,5D- beziehungsweise 3D-integrierten Funktionsblöcke für ein Chiplet müssen nicht alle im selben, teuren Spitzenprozess gefertigt werden. Einige lassen sich durchaus in preiswerteren, weniger hochintegrierten Fertigungslinien produzieren. Zudem steigt bei kleineren Dies auch die Ausbeute im Vergleich zu monolithischen Großschaltkreisen. Und meist geht es eben auch darum, mehr Rechenkraft oder Funktionalitäten auf kleinstem Raum zu packen.

Für besonders hohe Pack- und Kontaktierdichten in kleinen Rasterabständen unterhalb von 10 µm setzt sich dabei immer mehr das ‚Hybrid Bonding' durch. Dabei werden die noch unverpackten Schaltkreise (‚Dies') über in Silicium eingebettete Kupfer-Ballen (‚Pads') verknüpft. Um damit Dies beziehungsweise Funktionsblöcke übereinander zu kontaktieren, sind allerdings hochpräzise Montagetechniken nötig, betonte Emmanuel Ollier vom französischen Großforschungszentrum ‚CEA-Leti', das dafür auch mit selbstorganisierenden Strukturen experimentiert. Die Platzierung und Kontaktierung von einzelnen Schaltkreisen auf prozessierten Wafern (Die-to-wafer) mittels Hybrid Bonding ist nach seiner Überzeugung der nächste große Schritt hin zu Hochleistungs-Rechentechnik auf Basis heterogener Chiplets.

Branche peilt Billionen-Umsatz an

Laith Altimime rechnet mit einem starken Branchenwachstum in den nächsten JahrenDass die Branche derzeit soviel Energie in dieses Thema steckt, hängt nicht zuletzt mit der – jenseits aller periodischen Schwankungen – langfristig stetig wachsenden Nachfrage aus immer mehr Branchen für immer leistungsfähigere Mikroelektronik zusammen. Darauf hatte Semi-Europe-Präsident Laith Altimime bereits zum Auftakt der Konferenz in Dresden hingewiesen: Neue Digitalisierungsschübe in zahlreichen Wirtschaftszweigen, der Umstieg auf Elektroautos, der Trend zum autonomen Fahren und zahlreiche staatliche Beihilfeprogramme für Chipfabriken weltweit bleiben dabei vorerst die wichtigsten Wachstumstreiber für die globale Halbleiterindustrie, betonte Altimime. So sei damit zu rechnen, dass sich der weltweite Mikroelektronik-Umsatz bis 2030 etwa verdoppeln werde – von derzeit rund 500 Mrd. $ auf dann über 1 Bn. $.

Laith Altimime rechnet mit einem starken Branchenwachstum in den nächsten JahrenDass die Branche derzeit soviel Energie in dieses Thema steckt, hängt nicht zuletzt mit der – jenseits aller periodischen Schwankungen – langfristig stetig wachsenden Nachfrage aus immer mehr Branchen für immer leistungsfähigere Mikroelektronik zusammen. Darauf hatte Semi-Europe-Präsident Laith Altimime bereits zum Auftakt der Konferenz in Dresden hingewiesen: Neue Digitalisierungsschübe in zahlreichen Wirtschaftszweigen, der Umstieg auf Elektroautos, der Trend zum autonomen Fahren und zahlreiche staatliche Beihilfeprogramme für Chipfabriken weltweit bleiben dabei vorerst die wichtigsten Wachstumstreiber für die globale Halbleiterindustrie, betonte Altimime. So sei damit zu rechnen, dass sich der weltweite Mikroelektronik-Umsatz bis 2030 etwa verdoppeln werde – von derzeit rund 500 Mrd. $ auf dann über 1 Bn. $.

Speziell in Europa kommen derzeit vor allem auch von staatlicher Seite starke Marktimpulse. Altimime verweist da insbesondere auf den ‚European Chips Act', mit dem EU-Kommissionspräsidentin Ursula von der Leyen (CDU) binnen einer Dekade den Marktanteil der europäischen Halbleiterindustrie von derzeit 7–9 % (die Schätzungen schwanken je nach Analyse) auf 20 % mehr als verdoppeln will.

Allerdings steht die Branche auch vor erheblichen Herausforderungen. Dazu gehört der Fachkräftemangel: Wenn die Halbleiterbranche das Billionen-Umsatzziel bis zum Ende dieser Dekade wirklich erreichen will, dann wird sie weltweit rund eine Million zusätzliche Mikrotechnologen, Chipwerker, Mechatroniker, Ingenieure und andere Fachleute brauchen, prognostiziert Seniordirektor Chris Jones vom britischen Chipwerk-Ausrüster ‚SPTS Technologies'.

Quellen

3D & System Summit Semi 2023, Semi Europe, Yole, AT&S, Fraunhofer EAS, Cea-Leti, Siemens EDA, Oiger.de