Konzept des Digitalen Zwillings

Ein Digitaler Zwilling ist nichts anderes als eine virtuelle Darstellung, das Spiegelbild eines physischen Objekts, Systems oder Prozesses. Es ist ein digitales Gegenstück, das die reale Entität in Bezug auf ihre Eigenschaften, ihr Verhalten und ihre Interaktionen nachahmt. Das Konzept des digitalen Zwillings kombiniert Technologien wie das ‚Internet of Things' (IoT), ‚künstliche Intelligenz' (KI), Datenanalyse sowie Modellierungs- und Simulationstechniken (Abb. 1).

Abb. 1: Konzept des Digitalen ZwillingsDigitale Zwillinge entstehen in der Regel durch das Sammeln und Einbinden von Daten der Sensoren, Geräte und anderer Quellen, die mit dem physischen Gegenstück verbunden sind. Mithilfe dieser Daten wird ein virtuelles Modell erstellt, welches das physische Objekt oder System nachbildet und seine Überwachung, Analyse und Optimierung in Echtzeit ermöglicht. Der digitale Zwilling kann Einblicke in die Leistung, den Zustand und das Verhalten des physischen Objekts geben und so eine bessere Entscheidungsfindung, vorausschauende Wartung und Leistungsoptimierung ermöglichen, die in einem sicheren und kurzen Zeitraum entwickelt werden kann. Das Konzept des digitalen Zwillings findet in verschiedenen Bereichen Anwendung, z. B. in der Fertigung, bei Energiesystemen, im Gesundheitswesen, im Transportwesen und in der Stadtplanung. In der Leiterplattenherstellung kann ein digitaler Zwilling beispielsweise zur Analyse und Optimierung des Prozessschritts der Verkupferung verwendet werden, indem zunächst die tatsächliche Prozessleistung erkannt und dann die optimale Strategie zur Leistungsoptimierung entworfen wird.

Abb. 1: Konzept des Digitalen ZwillingsDigitale Zwillinge entstehen in der Regel durch das Sammeln und Einbinden von Daten der Sensoren, Geräte und anderer Quellen, die mit dem physischen Gegenstück verbunden sind. Mithilfe dieser Daten wird ein virtuelles Modell erstellt, welches das physische Objekt oder System nachbildet und seine Überwachung, Analyse und Optimierung in Echtzeit ermöglicht. Der digitale Zwilling kann Einblicke in die Leistung, den Zustand und das Verhalten des physischen Objekts geben und so eine bessere Entscheidungsfindung, vorausschauende Wartung und Leistungsoptimierung ermöglichen, die in einem sicheren und kurzen Zeitraum entwickelt werden kann. Das Konzept des digitalen Zwillings findet in verschiedenen Bereichen Anwendung, z. B. in der Fertigung, bei Energiesystemen, im Gesundheitswesen, im Transportwesen und in der Stadtplanung. In der Leiterplattenherstellung kann ein digitaler Zwilling beispielsweise zur Analyse und Optimierung des Prozessschritts der Verkupferung verwendet werden, indem zunächst die tatsächliche Prozessleistung erkannt und dann die optimale Strategie zur Leistungsoptimierung entworfen wird.

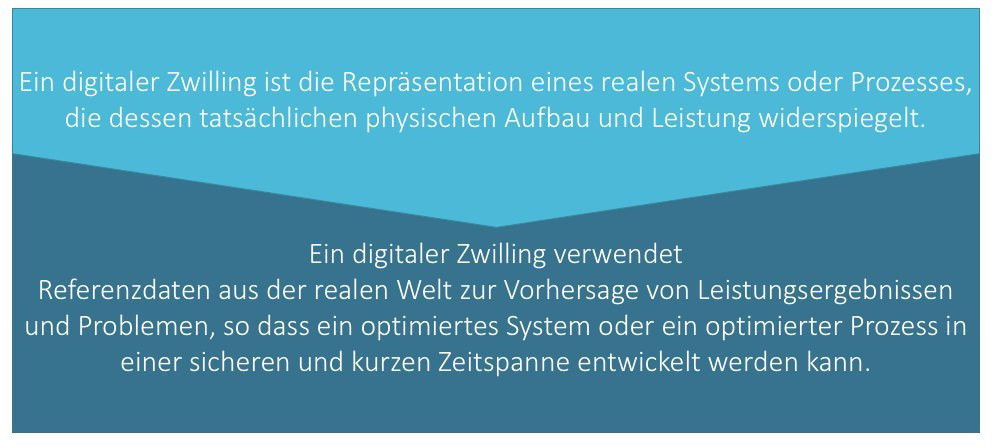

Das Konzept des digitalen Zwillings spielt eine wichtige Rolle in der Industrie 4.0 und in der intelligenten Fertigung (Smart Manufacturing), die sich auf den Einsatz fortschrittlicher digitaler Technologien zur Schaffung intelligenter, vernetzter und datengesteuerter Fertigungssysteme bezieht (Abb. 2).

Abb. 2: Industrie 4.0-KonzeptDigitale Zwillinge können im Konzept der intelligenten Fertigung folgende Schlüsselrollen einnehmen:

Abb. 2: Industrie 4.0-KonzeptDigitale Zwillinge können im Konzept der intelligenten Fertigung folgende Schlüsselrollen einnehmen:

- Design und Entwicklung: Digitale Zwillinge ermöglichen es Herstellern, virtuelle Prototypen von Produkten und Produktionssystemen zu erstellen. Durch die Simulation und Analyse verschiedener Designoptionen können Unternehmen die Produktleistung optimieren, die Entwicklungszeit verkürzen und die Kosten minimieren, bevor die physische Produktion beginnt.

- Vorausschauende Wartung: Digitale Zwillinge helfen bei der Umsetzung vorausschauender Wartungsstrategien, indem sie den Zustand und die Leistung von Produkten und Produktionssystemen anhand der technischen Daten analysieren und frühe Anzeichen für potenzielle Ausfälle erkennen. Dies ermöglicht eine proaktive Wartungsplanung, die Ausfallzeiten minimiert, Wartungskosten senkt und die Effektivität der Anlagen insgesamt verbessert.

- Optimierung und Simulation: Digitale Zwillinge bieten eine Plattform für die Simulation und Optimierung von Fertigungsprozessen. Durch die Erstellung virtueller Nachbildungen von Produktionslinien ermöglicht der digitale Zwilling den Herstellern, mit verschiedenen Szenarien zu experimentieren, Arbeitsabläufe zu optimieren und Möglichkeiten zur Effizienzsteigerung zu erkennen. Dazu gehören die Optimierung von Produktionsplänen, die Minimierung des Energieverbrauchs und die Reduzierung von Materialabfällen.

- Produktqualität: Digitale Zwillinge können die Produktqualität während des gesamten Herstellungsprozesses überwachen. Durch die Integration von Daten aus Sensoren und Qualitätskontrollsystemen kann der digitale Zwilling Abweichungen und Fehlerursachen anzeigen und Korrekturmaßnahmen vorschlagen. Dies gewährleistet eine gleichbleibende Produktqualität und ermöglicht die Rückverfolgbarkeit durch die Erfassung von Daten über Materialien, Prozesse und Komponenten, die im Herstellungsprozess verwendet werden.

- Integration der Lieferkette: Digitale Zwillinge erleichtern die Integration und Koordination der gesamten Lieferkette in der intelligenten Fertigung. Durch die Erstellung virtueller Darstellungen von Lieferanten, Logistiknetzwerken und Bestandssystemen können Hersteller den Materialfluss, die Lagerbestände und die Logistikplanung optimieren. Dies trägt dazu bei, die Vorlaufzeiten zu verkürzen, die Agilität zu verbessern und die Gesamtleistung der Lieferkette zu steigern.

- Kontinuierliche Verbesserung und Innovation: Digitale Zwillinge bieten eine Feedback-Schleife für kontinuierliche Verbesserung und Innovation – durch das Sammeln von Daten über die Produktleistung, das Kundenfeedback und die Marktnachfrage können Hersteller Bereiche mit Verbesserungspotenzial analysieren und identifizieren. Dazu gehören die Optimierung von Designs, die Implementierung von Produkt-Upgrades und die Anpassung von Angeboten an spezifische Kundenbedürfnisse.

Alles in allem ermöglichen digitale Zwillinge in der intelligenten Fertigung eine datengesteuerte Entscheidungsfindung, erhöhen die betriebliche Effizienz, verbessern die Produktqualität und können Innovationen vorantreiben. Sie bieten eine ganzheitliche Sicht auf das Ökosystem der Fertigung und ermöglichen die Optimierung und kontinuierliche Verbesserung der gesamten Wertschöpfungskette.

Konzept eines Galvanisierungsprozesses

Bei der Galvanisierung wird eine Metallschicht durch eine elektrochemische Reaktion auf einer leitfähigen Oberfläche abgeschieden. Bei der galvanischen Beschichtung von Leiterplatten wird in einem ersten Schritt ein stromloser Prozess durchgeführt, bei dem eine chemische Abscheidung von Kupfer auf die Oberflächen der Leiterplatte, einschließlich der Innenseite von Bohrungen, aufgebracht wird. Zweck dieses Beschichtungsvorgangs ist es, eine dünne Metallschicht auf der Leiterplatte und in den Löchern zu erzeugen, die als Grundlage für den nachfolgenden Galvanisierungsprozess dient. Danach wird die Platine für den Galvanisierungsprozess vorbereitet:

- Verunreinigungen und Bohrrückstände werden aus den Löchern entfernt

- Das Innere der Löcher wird einem Mikroätzverfahren unterzogen, um die Haftung des Kupfers zu verbessern

- Ein Fotoresist wird sowohl auf die Ober- als auch auf die Unterseite der Platine aufgetragen

- Der Fotoresist wird selektiv mit ultraviolettem Licht bestrahlt, wobei nur die gewünschten metallischen Schaltkreismuster ungeschützt bleiben

- Der belichtete und biegsame Fotolack, der die Schaltkreismuster bedeckt, wird abgewaschen, so dass die verbleibenden Oberflächenbereiche der Leiterplatte durch gehärteten Fotolack maskiert werden (Abb. 3).

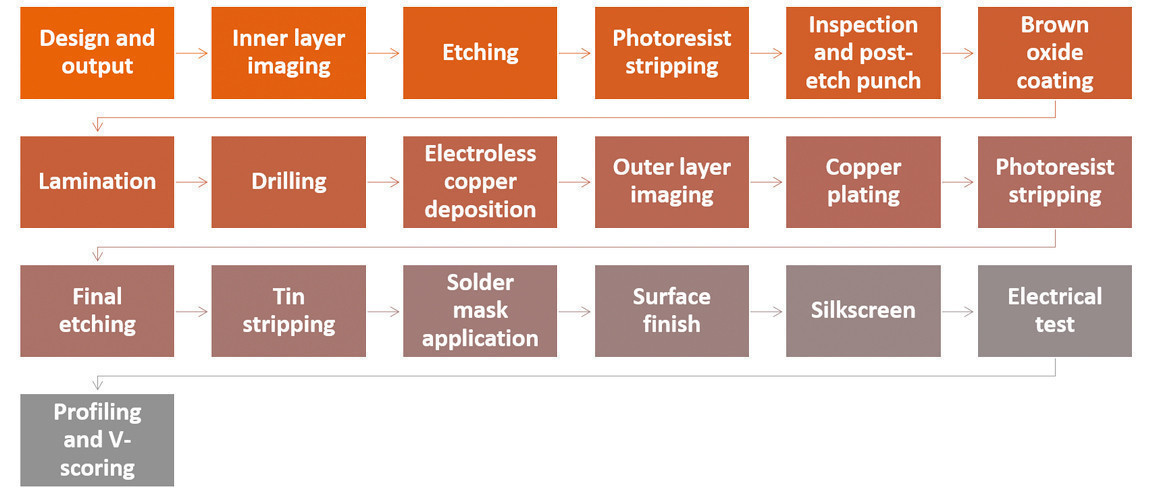

Abb. 3: Arbeitsablauf der LeiterplattenherstellungIn diesem Stadium wird die Leiterplatte für die galvanische Beschichtung mit Kupfer auf den äußeren Schichten und in den Bohrlöchern vorbereitet. Sie wird an die negativ geladene Kathode angeschlossen und in ein chemisches Bad getaucht, das speziell für die Galvanisierung entwickelt wurde. Während des Galvanisierungsprozesses wandern die Kupferionen in der Lösung in Richtung Kathode und lagern sich an den freiliegenden Kupferschaltkreisen auf der Platine an (Abb. 4).

Abb. 3: Arbeitsablauf der LeiterplattenherstellungIn diesem Stadium wird die Leiterplatte für die galvanische Beschichtung mit Kupfer auf den äußeren Schichten und in den Bohrlöchern vorbereitet. Sie wird an die negativ geladene Kathode angeschlossen und in ein chemisches Bad getaucht, das speziell für die Galvanisierung entwickelt wurde. Während des Galvanisierungsprozesses wandern die Kupferionen in der Lösung in Richtung Kathode und lagern sich an den freiliegenden Kupferschaltkreisen auf der Platine an (Abb. 4).

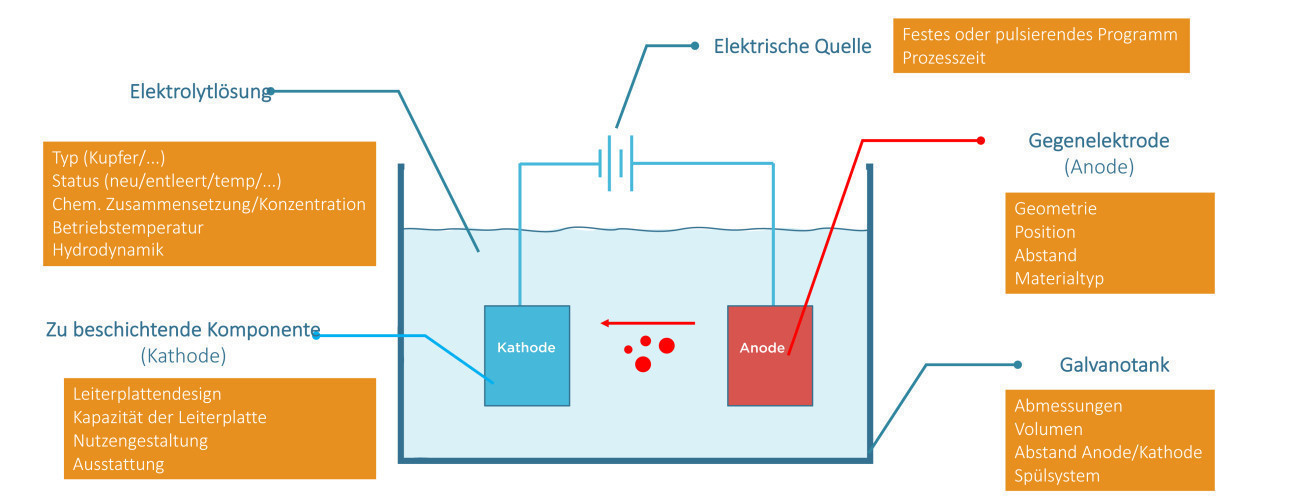

Abb. 4: Schematischer Aufbau eines Galvanisierungsprozesses mit Hervorhebungen, die die Prozessleistung beeinflussen

Abb. 4: Schematischer Aufbau eines Galvanisierungsprozesses mit Hervorhebungen, die die Prozessleistung beeinflussen

Der Prozess der Verkupferung dient einem doppelten Zweck. Erstens erhöht sich die Dicke des Kupfers auf den Oberflächenpads und Leitern und stärkt so deren Integrität. Zweitens stellt es eine zuverlässige Kupferverbindung zwischen den Schichten her, indem es sich durch die durchkontaktierten Durchgangsbohrungen erstreckt. Damit wirkt sich die Qualität der galvanischen Kupferschicht direkt auf die Leistung der Leiterplatte sowie auf ihre mechanischen Eigenschaften aus und hat einen gewissen Einfluss auf die nachfolgenden Schritte der Leiterplattenherstellung. Daher ist die Qualitätskontrolle der galvanischen Kupferbeschichtung ein entscheidender Aspekt der Leiterplattenbeschichtungstechnik, die selbst für erfahrene Hersteller oft eine Herausforderung darstellt. Er muss etwa berücksichtigen, dass Probleme im Zusammenhang mit der galvanischen Kupferabscheidung die Integrität der Verbindungen in den Lochwänden gefährden können, was zu einem möglichen Ausfall der Leiterplatte führen kann. Zu den häufigsten Abscheidungsfehlern gehört das Vorhandensein von Hohlräumen in der Kupferbeschichtung der Lochwand. Eine unzureichende und unvollständige Beschichtung der Lochwände kann den elektrischen Stromfluss behindern. Das Auftreten von Hohlräumen in durchkontaktierten Löchern entsteht, wenn das Kupfer während des Abscheidungsprozesses nicht gleichmäßig beschichtet wird, was eine effektive Beschichtung behindert. Dazu tragen mehrere Faktoren bei, darunter Verunreinigungen, das Vorhandensein von Luftblasen an den Lochseiten und grobes Bohren. Diese Faktoren zusammengenommen führen zu einer unebenen Oberfläche innerhalb der Durchgangsbohrung, was es schwierig macht, eine nahtlose und ununterbrochene Kupferschicht zu erhalten. Diese Herausforderung betrifft vor allem das Leiterplattendesign, da Durchgangsbohrungen ein integrierter Bestandteil des Leiterplattendesigns sind. Der Aufbau des Galvanisierungsprozesses und die fehlende Prozesskontrolle können jedoch weitere Probleme mit sich bringen, deren Folgen sich in einer ungleichmäßigen Verteilung der Kupferschicht zeigen. Die Herausforderungen, die mit dem Prozess selbst zusammenhängen, gefährden die physikalischen Parameter (Abb. 4), die ebenfalls berücksichtigt werden müssen: die Art des Galvanobades und sein elektrochemisches Verhalten, das von der chemischen Zusammensetzung und Konzentration, der Temperatur, der Bewegung und der Stromdichte abhängt; der Substrattyp, die Badgröße, der Anodentyp, der Anodenabstand und die Spezifikationen des Gleichrichters. Dies zeigt bereits, wie viele Variablen man kontrollieren muss, um sicherzustellen, dass der Kupfergalvanisierungsprozess auf die am besten geeignete Weise betrieben wird, so dass eine gleichmäßige Kupferabscheidung entlang aller aktiven Oberflächenbereiche auf der Leiterplatte erreicht werden kann. Daher erscheint es sinnvoll und vorteilhaft, einen Ansatz zu verwenden, der es ermöglicht, die Verteilung der galvanisch abgeschiedenen Kupferschichten auf einem speziellen Leiterplattendesign vorherzusagen, bevor der eigentliche, physikalische Prozess eingestellt wird. Auf diese Weise können wir potenzielle Probleme mit einer ungleichmäßigen Kupferbedeckung erkennen und im Vorfeld entschärfen, um einen reproduzierbaren Prozess mit der höchstmöglichen Beschichtungsqualität zu gewährleisten. Zu diesem Zweck kann das Konzept des digitalen Zwillings verwendet werden.

Leistungsbewertung des Kupfergalvanisierungsprozesses durch ein digitales Zwillingskonzept

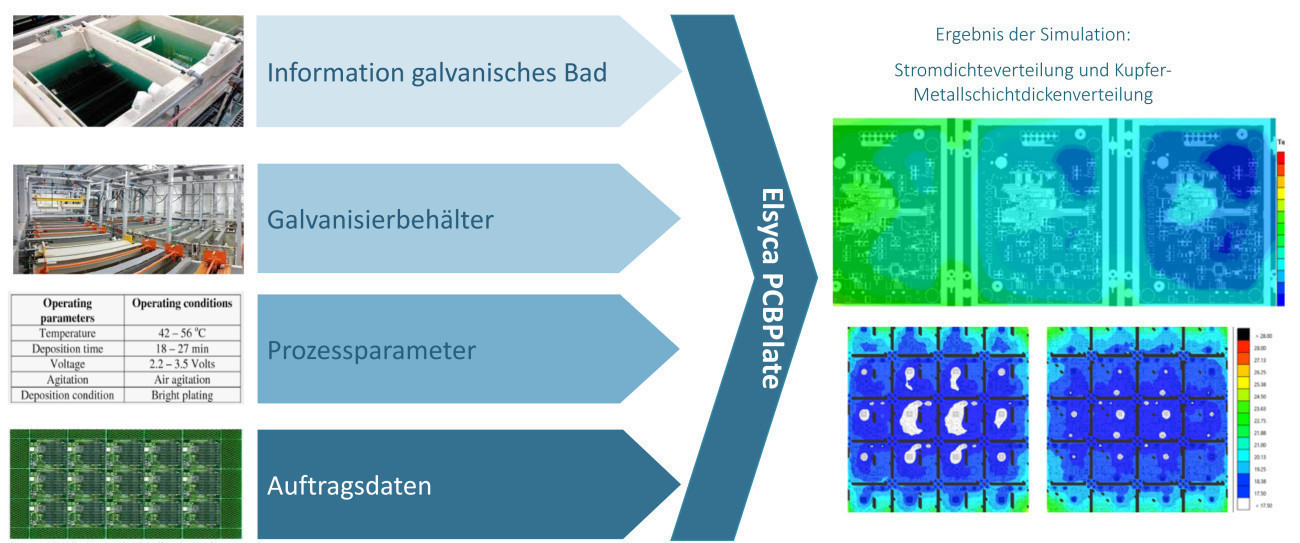

Ein digitaler Zwilling der Verkupferung ist eine virtuelle Darstellung des physischen Kupfergalvanisierungsprozesses, wie er im Arbeitsablauf der Leiterplattenherstellung definiert ist. Dazu gehört die Erstellung eines digitalen Modells, das die physische Infrastruktur des Galvanisierungsprozesses nachbildet. Dazu gehören: Informationen über das Kupferbad (insbesondere das elektrochemische Verhalten des Elektrolyten, das durch Polarisationsdaten dargestellt wird, die bei Abscheidungsexperimenten im Labormaßstab gewonnen wurden), Informationen über die Infrastruktur des Galvanikbehälters (Abmessungen des Behälters, des Gestells, Anodentypen, Anoden-Anoden-Abstand und Anoden-Kathoden-Abstand usw.), Prozessparameter (Abscheidungszeit, Art des Stromprogramms usw.) und Auftragsdaten, die sich auf die spezifische Leiterplatte und das Plattendesign beziehen (Abb. 5).

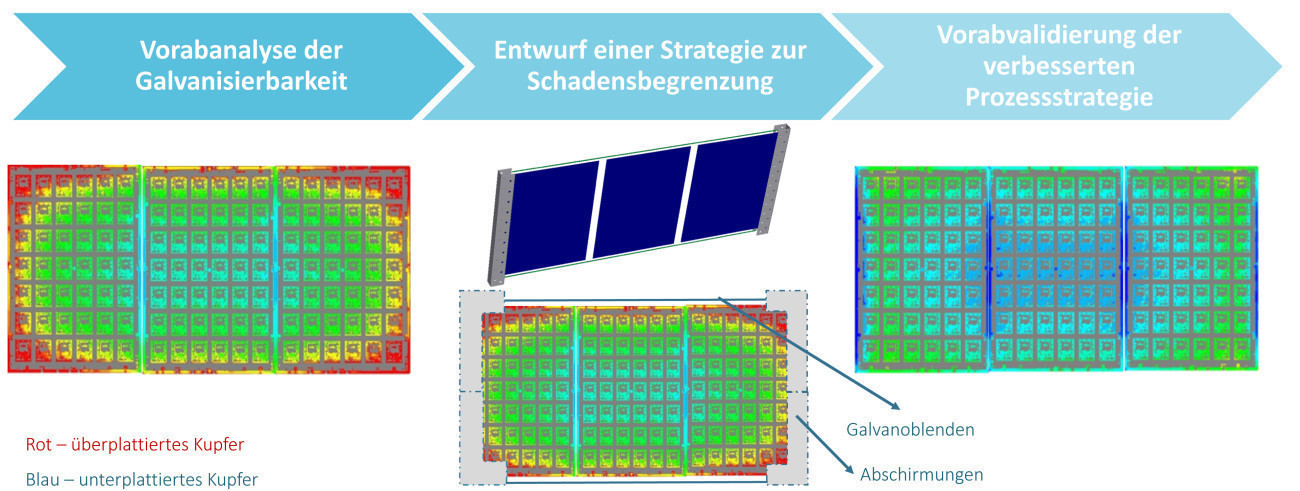

Abb. 5: Digitaler Zwilling für die prädiktive Modellierung der galvanischen Kupferschichtverteilung auf einer Leiterplatte – links: Daten des digitalen Zwillings – rechts: Simulationsergebnis – Die Farbabbildung zeigt Unterschiede in den Kupferschichtdicken: rote Farbe zeigt zu hohe Schichtdicken an, während dunkelblaue Farbe zu geringe Schichtdicken anzeigtAufgrund dieser Informationen wird ein Berechnungsmodell erstellt und die Analyse der Galvanisierbarkeit auf der Grundlage der Technologie durchgeführt, die Finite-Elemente-Analyse (FEA) verwendet, um die Verteilung der Stromdichte zu lösen und die Werte der Metallschichtdicke anhand des Faradayschen Gesetzes zu berechnen. Das Ergebnis solcher Simulationen ist ein klarer Überblick über die Stromdichteverteilung und die Verteilung der Kupferschichtdicke über alle aktiven Oberflächenbereiche des Leiterplattenprodukts. So ermöglicht der Ansatz eine Voraberkennung aller über- und unterkupferten Oberflächenbereiche auf der Grundlage des Leiterplattendesigns und des Aufbaus der Galvanisierungslinie unter Berücksichtigung des verwendeten Cu-Bades. Dies wiederum bietet die Möglichkeit, den Prozess weiter zu optimieren, um eine homogenere Verteilung der Kupferschichten zu erreichen, indem die Prozessparameter (Abscheidungszeit, Stromdichte) weiter angepasst werden und/oder eine spezielle Strategie zur Risikominimierung entwickelt wird, die den Einsatz von Werkzeugkomponenten (Abschirmungen, Galvanoblenden, Blindplatten, Hilfsanoden / konforme Anoden; Abb. 6) beeinträchtigt.

Abb. 5: Digitaler Zwilling für die prädiktive Modellierung der galvanischen Kupferschichtverteilung auf einer Leiterplatte – links: Daten des digitalen Zwillings – rechts: Simulationsergebnis – Die Farbabbildung zeigt Unterschiede in den Kupferschichtdicken: rote Farbe zeigt zu hohe Schichtdicken an, während dunkelblaue Farbe zu geringe Schichtdicken anzeigtAufgrund dieser Informationen wird ein Berechnungsmodell erstellt und die Analyse der Galvanisierbarkeit auf der Grundlage der Technologie durchgeführt, die Finite-Elemente-Analyse (FEA) verwendet, um die Verteilung der Stromdichte zu lösen und die Werte der Metallschichtdicke anhand des Faradayschen Gesetzes zu berechnen. Das Ergebnis solcher Simulationen ist ein klarer Überblick über die Stromdichteverteilung und die Verteilung der Kupferschichtdicke über alle aktiven Oberflächenbereiche des Leiterplattenprodukts. So ermöglicht der Ansatz eine Voraberkennung aller über- und unterkupferten Oberflächenbereiche auf der Grundlage des Leiterplattendesigns und des Aufbaus der Galvanisierungslinie unter Berücksichtigung des verwendeten Cu-Bades. Dies wiederum bietet die Möglichkeit, den Prozess weiter zu optimieren, um eine homogenere Verteilung der Kupferschichten zu erreichen, indem die Prozessparameter (Abscheidungszeit, Stromdichte) weiter angepasst werden und/oder eine spezielle Strategie zur Risikominimierung entwickelt wird, die den Einsatz von Werkzeugkomponenten (Abschirmungen, Galvanoblenden, Blindplatten, Hilfsanoden / konforme Anoden; Abb. 6) beeinträchtigt.

Abb. 6: Arbeitsablauf bei der Simulation der Verkupferung mit dem Softwaretool ‚Elsyca PCBPlate‘: Vorabanalyse der Galvanisierbarkeit als Basissimulation, um die Schichtdickenverteilung zu erkennen, Entwurf einer Strategie zur Risikominimierung – Schritt der Prozessoptimierung, Vorabvalidierung der verbesserten Prozessstrategie – Bewertung der tatsächlichen Prozessleistung nach der Festlegung der vorbeugenden MaßnahmenDa sowohl die Analyse der Prozessleistung als auch die Prozessoptimierung in einer Computerumgebung durchgeführt werden, bietet der Ansatz der prädiktiven Modellierung oder der Ansatz des digitalen Zwillings enorme Möglichkeiten für eine bessere Prozessgestaltung, -analyse und -optimierung. Er reduziert die Anzahl der Tests für den Nassprozess erheblich, spart Ressourcen auf jeder Ebene und stellt sicher, dass die Qualität der abgeschiedenen Kupferschicht immer den Anforderungen entspricht und nicht mehr vom Prozessbediener abhängig ist. Einer der größten Vorteile der digitalen Zwillinge für die Galvanik ist die Möglichkeit, schnelle Was-wäre-wenn-Analysen durchzuführen. Mit diesen können verschiedene Szenarien untersucht werden, um das Potenzial des Prozesses für eine Vielzahl von Leiterplattenprodukten zu prüfen, von eher einfachen bis hin zu den komplexesten. Dies bietet die Möglichkeit, mehr Aufträge mit verschiedenen Produkten verschiedener Leiterplattenherstellern zu bewältigen.

Abb. 6: Arbeitsablauf bei der Simulation der Verkupferung mit dem Softwaretool ‚Elsyca PCBPlate‘: Vorabanalyse der Galvanisierbarkeit als Basissimulation, um die Schichtdickenverteilung zu erkennen, Entwurf einer Strategie zur Risikominimierung – Schritt der Prozessoptimierung, Vorabvalidierung der verbesserten Prozessstrategie – Bewertung der tatsächlichen Prozessleistung nach der Festlegung der vorbeugenden MaßnahmenDa sowohl die Analyse der Prozessleistung als auch die Prozessoptimierung in einer Computerumgebung durchgeführt werden, bietet der Ansatz der prädiktiven Modellierung oder der Ansatz des digitalen Zwillings enorme Möglichkeiten für eine bessere Prozessgestaltung, -analyse und -optimierung. Er reduziert die Anzahl der Tests für den Nassprozess erheblich, spart Ressourcen auf jeder Ebene und stellt sicher, dass die Qualität der abgeschiedenen Kupferschicht immer den Anforderungen entspricht und nicht mehr vom Prozessbediener abhängig ist. Einer der größten Vorteile der digitalen Zwillinge für die Galvanik ist die Möglichkeit, schnelle Was-wäre-wenn-Analysen durchzuführen. Mit diesen können verschiedene Szenarien untersucht werden, um das Potenzial des Prozesses für eine Vielzahl von Leiterplattenprodukten zu prüfen, von eher einfachen bis hin zu den komplexesten. Dies bietet die Möglichkeit, mehr Aufträge mit verschiedenen Produkten verschiedener Leiterplattenherstellern zu bewältigen.

Die richtige Kupferbalance in der Entwurfsphase einer Leiterplatte

Bei der Herstellung von Leiterplatten, die Ätz- und Beschichtungsprozesse umfasst, sind Kupferbahnen für die Leitfähigkeit verantwortlich. Durch eine gleichmäßige Verkupferung auf jeder Leiterplattenschicht wird eine gleichmäßige Leiterdicke auf den beschichteten Oberflächen erreicht, was die Signalübertragung und die Gesamtleistung der Schaltung verbessert. Die homogene Kupferverteilung über alle aktiven Oberflächenbereiche sorgt für eine bessere Leiterplattendicke während des Laminiervorgangs und verringert die Anzahl der Bereiche mit niedrigem Druck, die möglicherweise ein Redesign erfordern. Eine optimale Kupferabdeckung und Schichtdickenverteilung während der Beschichtung kann durch die Sicherstellung einer ordnungsgemäßen Kupferbalance in der Phase des Leiterplattendesigns erreicht werden: Die Kupferbalance ist eine der wichtigsten Spezifikationen, die bei der Herstellung von Leiterplattenprodukten befolgt werden müssen. Mit ihr wird eine symmetrischen Verteilung der Kupferbahnen in jeder Schicht des Lagenaufbaus erzielt, um elektrische und mechanische Probleme (Krümmung, Verdrehung, Verformung) zu vermeiden, die die Leistung der Schaltung beeinträchtigen können. Betrachtet man den Galvanisierungsprozess, so kann ein Ungleichgewicht des Kupfers auf der Ober- und Unterseite oder innerhalb einzelner Lagenaufbauten zu einer Überplattierung führen, die unerwünschte Verbindungen zwischen den Leiterbahnen oder Unterätzungen zur Folge hat. Eine gleichmäßige Schichtdickenverteilung ist also aus mehreren Gründen wichtig:

- Stromverteilung: Kupferleitungen auf einer Leiterplatte leiten elektrische Ströme zwischen verschiedenen Komponenten. Wenn der Strom durch eine Leiterbahn fließt, stößt er auf Widerstand, was zu einem Spannungsabfall führt. Wenn die Kupferverteilung nicht ausgewogen ist, können einige Leiterbahnen mehr Strom führen als andere, was zu ungleichmäßigen Spannungsabfällen führt. Dies kann zu Schwankungen in der Leistung der Komponenten und sogar zu einem Ausfall der Schaltung führen.

- Signalintegrität: In digitalen Hochgeschwindigkeitsschaltungen ist die Signalintegrität entscheidend für die korrekte Datenübertragung. Kupferungleichgewichte können zu Impedanzfehlanpassungen und Signalreflexionen führen, die Signalverzerrungen, Datenfehler und eine geringere Systemzuverlässigkeit verursachen. Durch die Sicherstellung der Kupferbalance kann die Impedanz von Signalleitungen kontrolliert werden, wodurch die Signalverschlechterung minimiert und die allgemeine Systemleistung verbessert wird.

- Wärmemanagement: Kupferspuren dienen als Leiter für die Wärmeableitung in PCBs. Wenn die Kupferverteilung unausgewogen ist, können einige Bereiche eine höhere Stromdichte aufweisen und folglich mehr Wärme erzeugen. Dies kann zu lokalisierten Hotspots führen, die die Zuverlässigkeit und Leistung der Komponenten beeinträchtigen. Durch eine ausgewogene Verteilung des Kupfers kann die Wärme gleichmäßig abgeleitet werden, wodurch thermische Probleme vermieden werden.

- Herstellbarkeit: Eine ungleichmäßige Kupferverteilung kann die Gleichmäßigkeit von Ätz- und Beschichtungsprozessen beeinträchtigen, was zu Schwierigkeiten bei der Herstellung und potenziellen Defekten führt. Durch das Ausbalancieren des Kupfers wird der Herstellungsprozess vorhersehbarer und konsistenter, was zu qualitativ hochwertigeren Leiterplatten führt.

In den meisten Fällen wird die Kupferbalance beim Leiterplattendesign jedoch oft übersehen oder unzureichend durchgeführt. Dies wird deutlich, wenn Sie sich in Benutzerforen zum Thema Leiterplattendesign umsehen. Dies liegt daran, dass die Kupferbalance in der Regel mit Standard-Leiterplattedesignsoftware durchgeführt wird, die vordefinierte Optionen für die Kupferbalance bietet. Sich ausschließlich auf diese integrierten Funktionen zu verlassen, ist jedoch nicht die optimale Lösung. Diese Tools bieten eine begrenzte Flexibilität bei der Definition der Form von Kupferflächen und beschränken sich häufig auf die Auswahl rechteckiger oder polygonaler Objekte aus einem vordefinierten Menü. Außerdem muss die Kupferbilanzierung manuell durchgeführt werden, was den gesamten Prozess zeitaufwändig macht. Darüber hinaus ist anzumerken, dass viele Kupferausgleichsoperationen, die mit einer gewöhnlichen Leiterplattendesignsoftware durchgeführt werden, aufgrund falscher Spezifikationseinstellungen und mangelnden Verständnisses des Kupferausgleichsansatzes fehlschlagen. In Abbildung 7 kann man die Folgen einer unzureichenden Kupferbalance sehen.

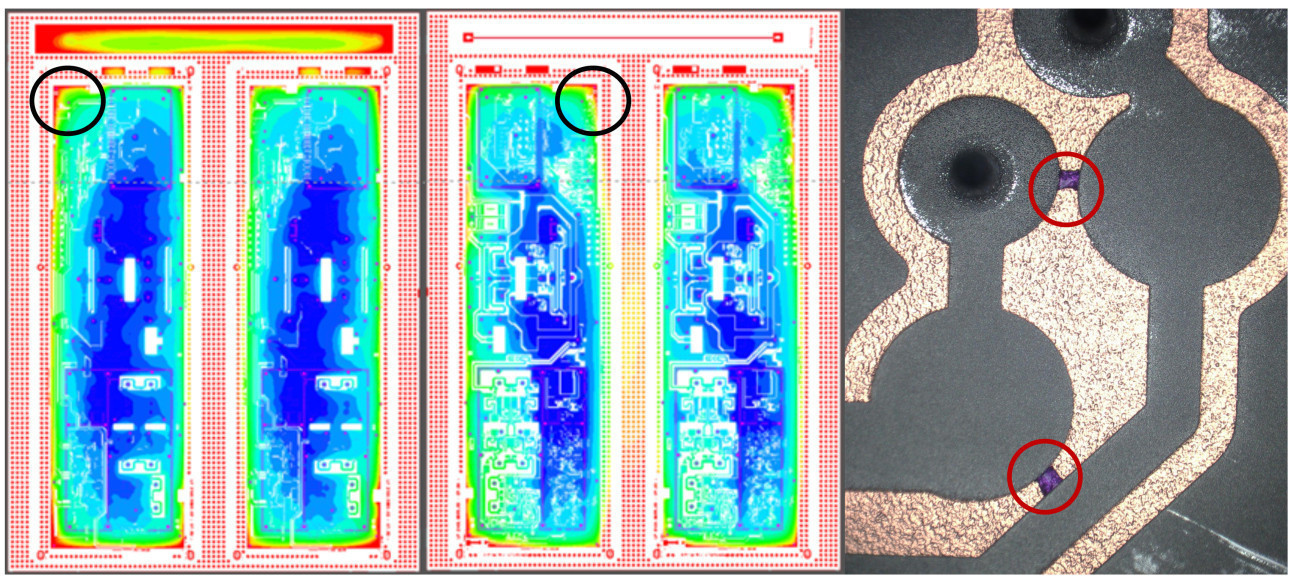

Abb. 7: l. und m.: Vorder- und Rückseite eines Leiterplattendesigns – unsachgemäße Kupferbalance in einem Standard-Leiterplattendesign- Tool, die zu überplattiertem Kupfer führt (rote Oberflächenbereiche, die durch schwarze Kreise gekennzeichnet sind) – r.: Kurzschlüsse (rote Kreise), verursacht durch Lackrückstände, die nach dem Ablösen des Fotolacks im SES-Prozess noch eingeklemmt sindDie Bilder links und in der Mitte zeigen überplattierte Kupferflächen (rot gekennzeichnet innerhalb schwarzer Kreise) auf beiden Seiten des Leiterplattenmodells (Vorder- und Rückseite). Diese überplattierten Bereiche waren das Ergebnis einer falschen Kupferbalance während der Designphase der Leiterplatte. Infolgedessen entstanden Kurzschlüsse (im rechten Bild mit roten Kreise markiert) aufgrund von Lackrückständen, die nach dem Ablösen des Fotolacks im Strip-Etch-Strip-Verfahren (SES) hängen blieben. Diese Kurzschlüsse hatten einen erheblichen Einfluss auf die Leistung der Leiterplatte.

Abb. 7: l. und m.: Vorder- und Rückseite eines Leiterplattendesigns – unsachgemäße Kupferbalance in einem Standard-Leiterplattendesign- Tool, die zu überplattiertem Kupfer führt (rote Oberflächenbereiche, die durch schwarze Kreise gekennzeichnet sind) – r.: Kurzschlüsse (rote Kreise), verursacht durch Lackrückstände, die nach dem Ablösen des Fotolacks im SES-Prozess noch eingeklemmt sindDie Bilder links und in der Mitte zeigen überplattierte Kupferflächen (rot gekennzeichnet innerhalb schwarzer Kreise) auf beiden Seiten des Leiterplattenmodells (Vorder- und Rückseite). Diese überplattierten Bereiche waren das Ergebnis einer falschen Kupferbalance während der Designphase der Leiterplatte. Infolgedessen entstanden Kurzschlüsse (im rechten Bild mit roten Kreise markiert) aufgrund von Lackrückständen, die nach dem Ablösen des Fotolacks im Strip-Etch-Strip-Verfahren (SES) hängen blieben. Diese Kurzschlüsse hatten einen erheblichen Einfluss auf die Leistung der Leiterplatte.

Um das oben beschriebene Szenario zu verhindern, müssen Sie sich unbedingt an die vorgeschriebenen Richtlinien für die richtige Kupferbalance halten:

- Um die Bildung von Kupfernestern zu vermeiden, ist es entscheidend, die Leiterbahnen so gleichmäßig wie möglich über die gesamte Platine zu verteilen. Dieses Prinzip sollte für jede einzelne Lage befolgt werden, ebenso wie für jede Symmetrieachse zwischen zwei oder mehr Lagen.

- Werden große Flächen benötigt, ist es notwendig, die Kupferbalance aufrechtzuerhalten, indem die entsprechenden Lagen in den Bereichen, die den Freiflächen gegenüberliegen, symmetrisch mit Kupfer gefüllt werden. Dadurch wird sichergestellt, dass ein Gegengewicht zu dem Kupfer in der gegenüberliegenden Schicht besteht.

- Wann immer es möglich ist, sollten große Kupferflächen als Gittermuster angelegt werden. Diese Gitterstruktur trägt dazu bei, Krümmungs- oder Verdrehungseffekte zu vermeiden, insbesondere bei einlagigen Leiterplatten. Außerdem fördert die Verwendung eines Gittermusters eine bessere Gleichmäßigkeit des Kupfers entlang der Wände der durchkontaktierten Löcher.

Um obengenannte Ziele zu erreichen, wird ein spezielles Kupferbalancestool verwendet (vgl. Abb. 8). Es ermöglicht dem Leiterplattendesigner, die Kupferbalance zu optimieren, indem er kritische Bereiche auf der Leiterplatte identifiziert, die während des Herstellungsprozesses Probleme mit der Beschichtung verursachen könnten. Durch den Einsatz eines automatisierten Ansatzes können potenzielle Probleme effektiv entschärft werden. Das Tool verwendet die Finite-Elemente-Methode (FEM), um den Balancebereich zu bestimmen, der die Kupferdichte innerhalb jedes Elements im Balancebereich darstellt. Dieser Prozess gewährleistet eine optimale Kupferverteilung innerhalb von Sekunden, wobei das Ergebnis in erster Linie von der Komplexität des Leiterplattendesigns abhängt und nicht vom manuellen Eingreifen des Leiterplattendesigners. Folglich ermöglicht das Tool den sofortigen Eins-zu-Eins-Vergleich, was Designanpassungen erleichtert und die Wahrscheinlichkeit verringert, dass ein Redesign erforderlich wird.

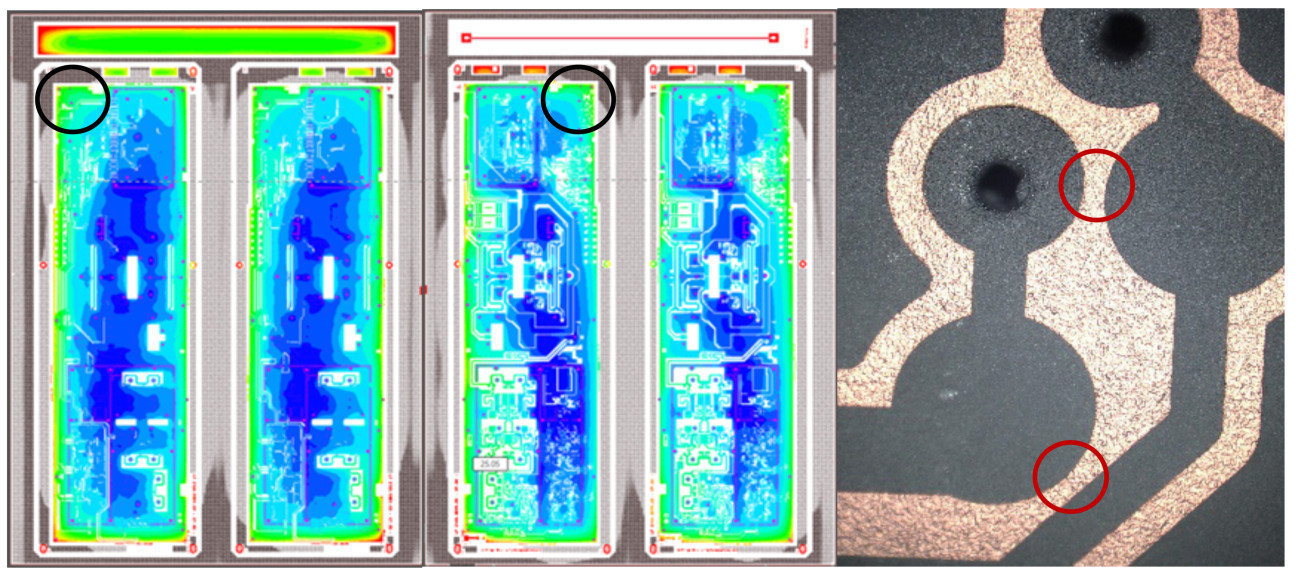

Abb. 8: l. und m.: Vorder- und Rückseite eines Leiterplattendesigns: korrekte Kupferbalance, die zu einer optimalen Kupferdicke führt (mit schwarzem Kreis markiert) – r.: es sind keine Kupferkurzschlüsse (mit rotem Kreis markiert) zu sehen, da die Kupferbalance mit einem speziellen Elsyca-PCB-Balance-Softwaretool durchgeführt wurdeDie oben aufgeführten Beispiele zeigen, dass die Kupferbalance beim Leiterplattendesign eine optimale Stromverteilung gewährleistet, die Signalintegrität aufrechterhält, ein effizientes Wärmemanagement fördert und die Herstellbarkeit verbessert. Sie trägt zur allgemeinen Funktionalität, Zuverlässigkeit und Leistung der Leiterplatte und des elektronischen Systems bei, zu dem sie gehört. Darüber hinaus hat sich gezeigt, dass die richtige Kupferbalance ein entscheidender Schritt ist, um die angestrebte Kupferdicke bei der Galvanisierung zu erreichen. Das Konzept des digitalen Zwillings ermöglicht eine Vorabanalyse und Optimierung der Oberflächenbehandlungsprozesse und des Kupfergalvanisierungsprozesses der Leiterplattenprodukte. Durch das virtuelle Testen verschiedener Szenarien und Variablen können die Hersteller die effizientesten und kostengünstigsten Produktionsparameter und Vermeidungsstrategien ermitteln. Dies verbessert die Produktqualität, reduziert den Ausschuss, verkürzt die Produktionszyklen und steigert die Gesamtproduktivität. Digitale Zwillinge erleichtern die Datenanalyse und Leistungsbewertung. Dieser datengesteuerte Ansatz unterstützt kontinuierliche Verbesserungsinitiativen und Entscheidungsprozesse, und die virtuelle Darstellung verbessert das Verständnis, die Sichtbarkeit und die Kontrolle über Produktionsabläufe, was zu langfristigen Vorteilen führt.

Abb. 8: l. und m.: Vorder- und Rückseite eines Leiterplattendesigns: korrekte Kupferbalance, die zu einer optimalen Kupferdicke führt (mit schwarzem Kreis markiert) – r.: es sind keine Kupferkurzschlüsse (mit rotem Kreis markiert) zu sehen, da die Kupferbalance mit einem speziellen Elsyca-PCB-Balance-Softwaretool durchgeführt wurdeDie oben aufgeführten Beispiele zeigen, dass die Kupferbalance beim Leiterplattendesign eine optimale Stromverteilung gewährleistet, die Signalintegrität aufrechterhält, ein effizientes Wärmemanagement fördert und die Herstellbarkeit verbessert. Sie trägt zur allgemeinen Funktionalität, Zuverlässigkeit und Leistung der Leiterplatte und des elektronischen Systems bei, zu dem sie gehört. Darüber hinaus hat sich gezeigt, dass die richtige Kupferbalance ein entscheidender Schritt ist, um die angestrebte Kupferdicke bei der Galvanisierung zu erreichen. Das Konzept des digitalen Zwillings ermöglicht eine Vorabanalyse und Optimierung der Oberflächenbehandlungsprozesse und des Kupfergalvanisierungsprozesses der Leiterplattenprodukte. Durch das virtuelle Testen verschiedener Szenarien und Variablen können die Hersteller die effizientesten und kostengünstigsten Produktionsparameter und Vermeidungsstrategien ermitteln. Dies verbessert die Produktqualität, reduziert den Ausschuss, verkürzt die Produktionszyklen und steigert die Gesamtproduktivität. Digitale Zwillinge erleichtern die Datenanalyse und Leistungsbewertung. Dieser datengesteuerte Ansatz unterstützt kontinuierliche Verbesserungsinitiativen und Entscheidungsprozesse, und die virtuelle Darstellung verbessert das Verständnis, die Sichtbarkeit und die Kontrolle über Produktionsabläufe, was zu langfristigen Vorteilen führt.

Übersetzung: Markolf Hoffmann

Autorin

Dipl. Ing. Agnieszka Franczak, PhD, leitet die Abteilung Oberflächenveredelung bei Elsyca, einem Anbieter computergestützter Ingenieurdienstleistungen für Kunden, die mit Herausforderungen beim Prozessdesign konfrontiert sind. Franczak entwickelt mit ihrem Team spezielle Softwarelösungen für die elektrochemisch basierte Prozessanalyse und -optimierung.

Weitere Informationen:

www.elsyca.com, Diese E-Mail-Adresse ist vor Spambots geschützt! Zur Anzeige muss JavaScript eingeschaltet sein!.

Referenzen

[1] Elsyca PCBPlate solution: www.elsyca.com/elsyca-solutions/elsyca-pcbplatewww.elsyca.com/elsyca-solutions/elsyca-pcbplate

[2] Elsyca PCBBalance solution: www.elsyca.com/elsyca-solutions/elsyca-pcbbalancewww.elsyca.com/elsyca-solutions/elsyca-pcbbalance

[3] PCB Metal Balancing, Patent, WO 2021/191346 A1.

[4] T. Lechler; J. Fuchs; M. Sjarov; M. Brossog; A. Selmaier; F. Faltus; T. Donhauser; J. Franke: Introduction of a comprehensive structure model for the digital twin in manufacturing, 25th IEEE International Conference of Emerging Technologies and Factory Automation (ETFA), 2020.

[5] G. Nelissen; B. Van den Bossche; I. Purcar; J. Deconinck: Three-dimensional simulations of current density distribution for patterned wafers and PCBs, In IPC, 2004.

[6] M. Purcar; B. Van den Bossche; L. Bortels; J. Deconinck; G. Nelissen: Three-dimensional current density distribution simulations for a resistive patterned wafer., Journal of the Electrochemical Society, 2004.

[7] G. Nelissen; B. Van den Bossche; L. Wanten: A performance simulaton tool for bipolar pulsed PCB plating, In ECWC 10 Conference at IPC, 2005.

Bildquellen

Elsyca

Sierra Circuits: www.protoexpress.com/kb/pcb-manufacturing-overview/

Danksagung

Ich danke im Besonderen Sascha Reuter und Manuel Luschtinetz, Rohde & Schwarz, für die Bereitstellung von Referenzmaterialien zu den Kupferbalancesimulationen und den Produktionsergebnissen (Abb. 7 und 8) sowie für die hervorragende Zusammenarbeit in den vergangenen Monaten.