Anzeige der Artikel nach Schlagwörtern: risc

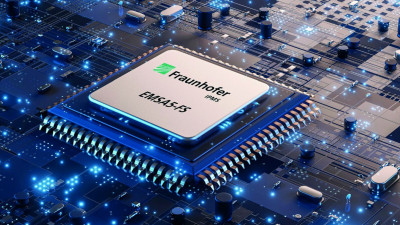

Der vom IPMS entwickelte Prozessorkern EMSA5-FS für funktionale Sicherheit auf Basis der Open-Source-Befehlssatzarchitektur RISC-V wird durch Mikroprozessor-Entwicklungswerkzeuge von Lauterbach – und damit von einem weiteren wichtigen Debugging-Tool – unterstützt.

Das Fraunhofer-Institut für Photonische Mikrosysteme IPMS, Dresden, bietet fertige, plattformunabhängige IP-Core-Module an. Mit diesen IP-Modulen können Entwickler schnell vollständige Funktionsbereiche in Standardprodukten wie SoCs, Mikrocontroller, FPGAs und ASICs übernehmen und so Entwicklungszeiten und -kosten erheblich reduzieren. Mit dem EMSA5 bietet das IPMS einen Prozessorkern auf Basis der offenen RISC-V-Befehlssatzarchitektur an. Seine aktuelle Version ist für Edge-KI-Anwendungen geeignet.