With the global focus on digitalization and the green deal, the electronics sector is facing major challenges, such as sustainable production, the use of innovative materials and the avoidance of bottleneck resources. With ‚time to market‘ being a key success factor, shorter development times and concurrent quality assurance measures of R&D, production and market performance are necessary. To this end, a highly efficient method for accelerated lifetime evaluation of solder joints in a variety of multilayer electronic components has been developed at TU Wien. With this high-frequency cyclic bending test-system, the testing time can be reduced from several months required by conventional methods to just a few hours.

Einführung

Die kontinuierliche Entwicklung in der Halbleiterindustrie hat in den letzten Jahrzehnten zu erheblichen technologischen Fortschritten geführt. Durch zahlreiche aufkommende Technologien erwartet die Branche ein starkes Wachstum und weitere Innovationen in der IC-Technologie, die wiederum eine erhöhte Komplexität erfordern. Insbesondere in Branchen wie der E-Mobilität und bei erneuerbaren Energien hat die zunehmende Nachfrage nach Hochleistungs-Halbleiterbauelementen zur Entwicklung von Modulen mit höherer Leistungsdichte, Betriebsfrequenz und Integration geführt [1, 2]. Dabei wird zunehmend die Übergangstemperatur herkömmlicher bleihaltiger- und bleifreier Lote sowie elektrisch leitfähiger Klebstoffe (ECAs) von etwa 150 °C überschritten [3–6]. Bereits bei der Herstellung und im späteren Betrieb treten in mehrschichtigen elektronischen Bauteilen Spannungen auf, die hauptsächlich auf die unterschiedlichen Wärmeausdehnungskoeffizienten der verwendeten Materialien zurückzuführen sind. Auf Dauer führen die als Folge der Temperaturschwankungen und der ungleichmäßigen Wärmeverteilung in den Bauteilen induzierten thermomechanischen, zyklischen Beanspruchungen zur Bildung und Ausbreitung von Rissen und schließlich zu Ermüdung und Versagen [7–10].

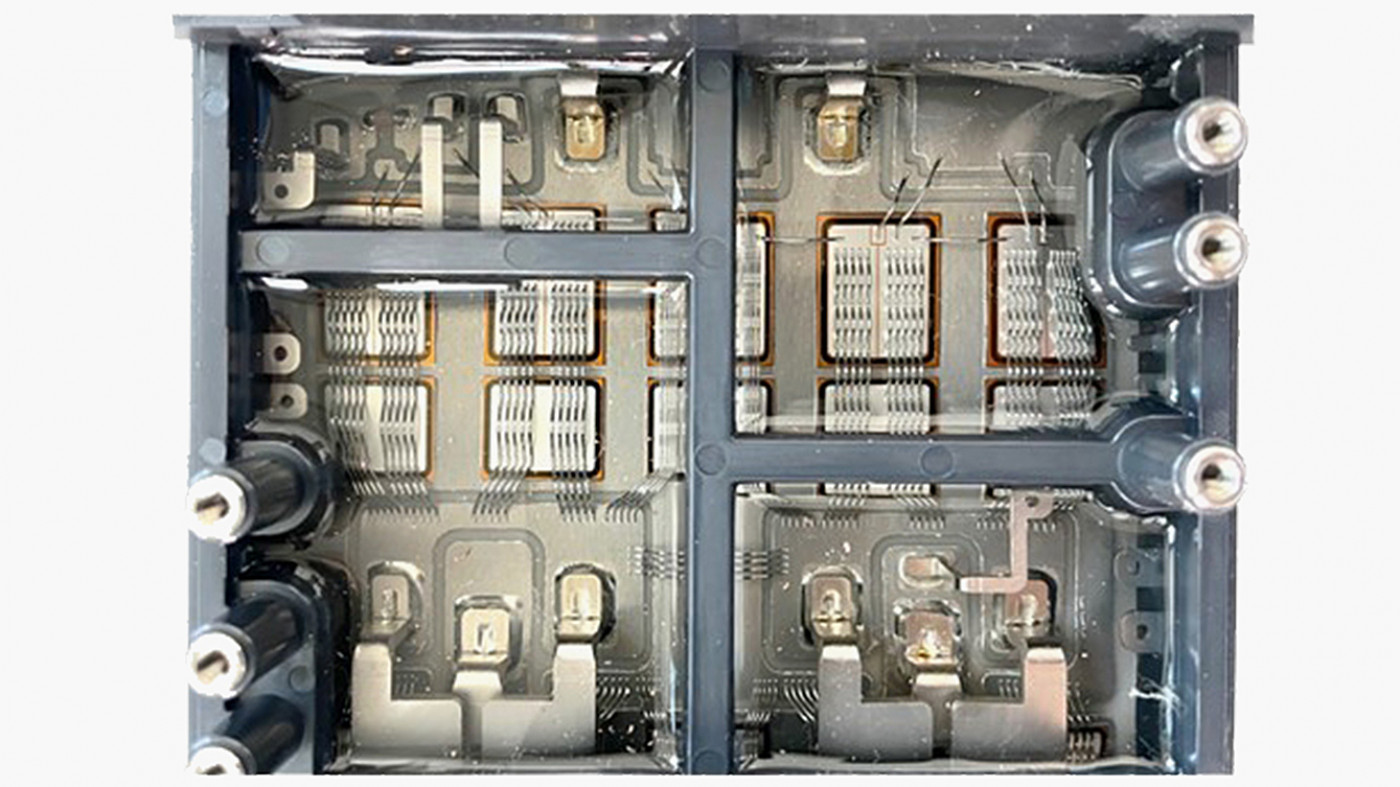

Bekanntermaßen stellen dabei großflächige Lötverbindungen, die neben Bonddrähten die wichtigsten elektrischen, mechanischen und thermischen Verbindungen zwischen Chips, Substrat und Grundplatte ausmachen, die größte Schwachstelle dar. Zusätzlich führen die hohen homologen Temperaturen in den Lötstellen, die die Diffusionsprozesse begünstigen, zu großen mikrostrukturellen Veränderungen und Kriecheffekten, die zu einer stärkeren Anfälligkeit dieser Verbindungen beitragen. Durch das in vielen Anwendungen verstärkte Aufkommen von Breitband-Halbleiter Technologien (WBG) wie Siliciumkarbid (SiC) und Galliumnitrid (GaN) mit Sperrschichttemperaturen von 175 °C und mehr, wird dieses Problem weiter verschärft und erfordert neue Verbindungstechnologien, Materialien und Aufbaumethoden [3, 4].

Alternative Verbindungstechnologien

Bleifreie Alternativen als Ersatz für Lote mit hohem Bleigehalt (d. h. mit mehr als 85 Gew.-% Pb) befinden sich noch in einem frühen Entwicklungsstadium. Neue Verbindungstechnologien wie Ag-Sintern, Niedertemperatur-Transient Flüssigphasensintern (wie Sn-Cu, Au-Sn, Au-In, Ag-In, Ag-Sn, Cu-In und Ni-Sn) oder hochschmelzende Lotlegierungssysteme wie AuSn, AuGe, ZnAl, ZnSn, BiAg und SnSb sind potenzielle, bleifreie und RoHS-konforme Ersatzstoffe für PbSn und andere bleihaltige Lote für die Hochtemperaturanwendungen [3, 4, 6]. Die meisten Alternativen sind in Bezug auf die Materialkosten deutlich teurer als Pb5Sn2.5Ag, eines der gängigsten Lote mit hohem Bleigehalt. Einige diese alternativen Technologien haben sich aufgrund der nur begrenzt verfügbaren Daten über ihre langfristige Zuverlässigkeit noch nicht als geeigneter Ersatz für Hochtemperatur Pb-Lote etabliert. Aufgrund der inhomogenen Mikrostruktur und des viskoplastischen Verhaltens der Lote bei typischen Betriebstemperaturen ist die Identifizierung der auftretenden Versagensmechanismen und die Prognose der Produktlebensdauer keine leichte Aufgabe.

Die meisten Alternativen sind in Bezug auf die Materialkosten deutlich teurer als Pb5Sn2.5Ag, eines der gängigsten Lote mit hohem Bleigehalt

Weil die potenziellen bleifreien Hochtemperaturwerkstoffe nicht ohne Einschränkungen hinsichtlich der drei Hauptkriterien Leistung, Verarbeitung und Kosten als Drop-in-Lösungen herangezogen werden können, wurde die Ausnahmeregelung für die Verwendung von bleihaltigen Loten mit hoher Schmelztemperatur erneut zumindest bis 2024 verlängert [5]. Um die derzeitigen Technologien aufrechtzuerhalten und weiter zu verbessern, besteht ein dringender Bedarf an der Suche und der Entwicklung von Lotlegierungen, die bleihaltige Hochtemperaturlote vollständig ersetzen können. Es wurden daher umfangreiche Studien zur Entwicklung alternativer Aufbau- und Verbindungstechnologien für Hochtemperaturanwendungen initiiert. Um diesen Entwicklungsprozess voranzutreiben und mit den Markttrends Schritt zu halten, ist die Entwicklung und Anwendung von hoch-beschleunigten und praxisrelevanten Methoden zur Zuverlässigkeitsbewertung besonders bei Hochleistungsbauteilen erforderlich.

Zuverlässigkeitstests

In der industriellen Praxis wird die Zuverlässigkeit von elektronischen Bauteilen mit Hilfe von Temperaturwechseltests bewertet. Statische Scher- und Pull-Tests werden zur Bestimmung der Qualität und Haftfestigkeit der Chip/Substrat-Verbindung verwendet. Die Temperaturwechseltests sollen die thermomechanischen Betriebsbedingungen in beschleunigter Form nachbilden, wobei zwischen aktiven Power Cycling (PC) Tests in Bezug auf die Sperrschichttemperatur (ΔTvj) und passiven Thermal Cycling (TC) Tests in Bezug auf die Lötstellen- und Gehäusetemperatur (ΔTC) unterschieden wird. Beim PC-Test wird die Temperatur der Chipverbindungen in relativ kurzen Intervallen von einigen Sekunden angehoben und gesenkt. Dabei werden hauptsächlich die Bonddrähte auf den Chips und die Lötstellen unter den Chips belastet. Typische beschleunigte PC-Tests für klassische Module werden mit einem Temperaturhub (ΔT) von etwa 90 K oder mehr und Heiz-/Kühlzyklen von etwa 30–60 Sekunden durchgeführt, wobei der Temperaturunterschied an der Sperrschicht und die Zyklusdauer je nach Anwendungsbereich variieren können.

Bei höheren Sperrschichttemperaturen kann es zu einem Versagen der Drahtbonds kommen, während geringere Temperaturunterschiede zu einer Degradation und einem Versagen der Lötschicht unter dem Siliciumchip führen [8]. Die Zuverlässigkeitsdiagramme stellen die Lebensdauer des gesamten Moduls als ΔT gegen die Zyklen bis zum Ausfall dar, ohne zwischen den verschiedenen Ausfallarten zu unterscheiden. Aufgrund der sehr langen Prüfzeiten von bis zu mehreren Monaten wird die Ermüdungslebensdauer bei hohen Zyklen (> 1e6 Zyklen) in der Regel durch Interpolation der Ermüdungsdaten ermittelt. Beim Thermal-Cycling (TC) wird die Gehäusetemperatur in relativ langen Intervallen innerhalb von Minuten erhöht und gesenkt. Dabei werden vor allem die Lötstellen zwischen Keramiksubstrat und Modulgrundplatte belastet. Zahlreiche Studien haben ergeben, dass unterschiedliche Prüfbedingungen die Lebensdauer und die vorherrschenden Ausfallarten der Geräte stark beeinflussen können [5, 6].

Um die geforderten Lebensdauern dieser Verbindungen zu gewährleisten und den wachsenden Bedarf an virtualisierten Qualifikationsmethoden zu decken, ist es unerlässlich, detaillierte Informationen über deren Verhalten unter zyklischen Belastungen zu ermitteln. Die Erstellung von zuverlässigen Lebensdauervorhersagemodellen erfordert daher, nicht nur zuverlässige experimentelle Daten, sondern ein fundiertes Wissen und Verständnis des zeit- und temperaturabhängigen Verformungsverhaltens der Lote und der Spannungs-Dehnungsbedingungen in den Verbindungen. Das Wissen über Rissbildung, -ausbreitung und Degradation ist entscheidend für das Verständnis der Ermüdungsmechanismen von Materialien. Deshalb werden in zahlreichen Studien die statischen und zyklischen Eigenschaften des Lotmaterials und der Lötstellen untersucht. In vielen Fällen werden isotherme mechanische Ermüdungsversuche bei niedrigen und mittleren Testfrequenzen durchgeführt, um Daten für konstitutive Modelle zu gewinnen, Finite-Elemente-Simulationen zu validieren und Lebensdauervorhersagemodelle zu erstellen.

Das Wissen über Rissbildung, -ausbreitung und Degradation ist entscheidend für das Verständnis der Ermüdungsmechanismen von Materialien

Für die Analyse von Delaminationen und die Detektion von Ausfällen elektronischer Komponenten stehen ex-situ Techniken wie Ultraschall-Mikroskopie (SAM), Computertomographie (CT), thermische Widerstandsmessungen [11] oder Puls-Phasen-Thermographie [12] zur Verfügung. Dennoch ist die Entwicklung effektiver und zuverlässigerer Methoden zur zerstörungsfreien in-situ-Erkennung und Überwachung von Delamination und Rissbildung vor dem endgültigen Versagen dringend erforderlich. Dies kann notwendige Informationen für präzise Lebensdauerprognosemodelle liefern, die den realen Bedingungen genau entsprechen. Insbesondere da es wichtig ist, die durch das Aufeinandertreffen verschiedener Technologien und Materialkombinationen und die damit verbundenen unterschiedlichen Versagensmoden in einem frühen Stadium der Entwicklung eines Produkts erkennen zu können.

Zu diesem Zweck wurde in unserer Forschungsgruppe an der TU Wien eine hocheffiziente Methode zur beschleunigten Bewertung von Elektronikbauteilen entwickelt [13–17]. Mit Hilfe eines speziellen hochfrequenten zyklischen Biegeprüfsystems könnte die Lebensdauer von Lötstellen in einer Vielzahl von mehrschichtigen elektronischen Strukturen in kürzester Zeit bestimmt werden. Dadurch können die Prüfzeiten der klassischen Testverfahren von einigen Monaten auf nur wenige Stunden reduziert werden. Ausgestattet mit einer neuartigen, zerstörungsfreien in-situ-Methode auf Basis der Laser-Doppler-Vibrometrie (LDV) kann dieses Prüfsystem zusätzlich zur Erkennung von Rissbildung und Delaminationen in Halbleiterstrukturen auch vor dem ‚End-of-Life‘ eingesetzt werden.

Im Folgenden wird die Anwendbarkeit dieses beschleunigten mechanischen Ermüdungsprüfsystems für die Zuverlässigkeitsbewertung elektronischer Verbindungen anhand von Beispielen speziell entwickelter Modell-Teststrukturen und Proben aus der Produktion vorgestellt und diskutiert.

Aufbau der beschleunigten mechanischen Ermüdungsprüfsysteme

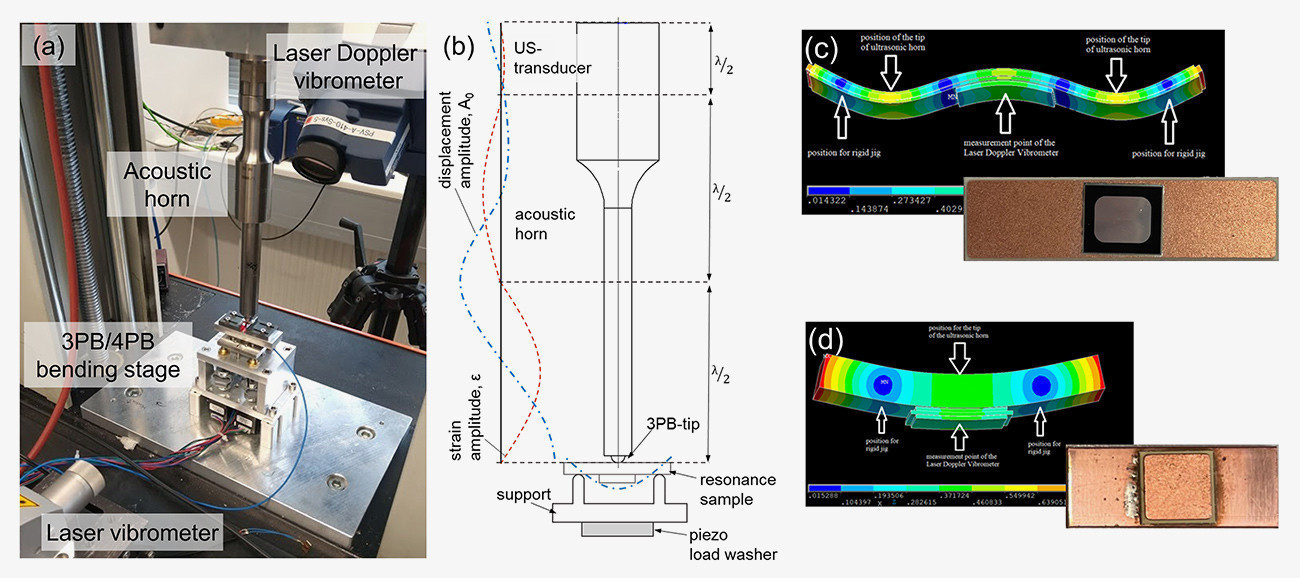

Die beschleunigten Ermüdungsversuche wurden mittels eines Ultraschall-Resonanzprüfsystems durchgeführt, das aus einer Stromversorgung, einem piezoelektrischen Wandler, einem akustischen Horn mit Tip und der Probe besteht, wie in Abbildung 1 a dargestellt ist. Die Schwingungsanregung einer longitudinalen Vibration bei 20kHz erfolgt im Piezo-Wandler und wird durch das Horn beziehungsweise passende Kopplungsstücke verstärkt. An der Stelle maximaler Auslenkung wird das System mittels der Drei/Vier-Punkt Biege (3PB)/4PB-Tip des Horns an die Probe gekoppelt (Abb. 1 b). Diese muss geometrisch so dimensioniert werden, dass es bei 20 kHz zur Ausbildung einer stehenden transversalen Schwingbewegung kommt. Beispiele von mit Hilfe von FE- Simulationen bestimmten Probengeometrien für großflächige Lotverbindungen in Halbleiter-Mehrlagenstrukturen sind in Abbildung 1 c, d dargestellt. Die statischen und zyklisch eingebrachten Lasten können mittels eines piezoelektrischen Kraftaufnehmers, der unter den Auflagern der 3PB/4PB Vorrichtung angebracht ist, gemessen werden. Eine geringe testabhängige statische Vorlast ist erforderlich, um während der Schwingungsanregung einen ständigen Kontakt des Tips mit der Probe zu gewährleisten. Die Schwingungsmodi und die Auslenkungsamplitude der Probe während der Anregung wurden mit einem Laser-Doppler-Vibrometer bestimmt.

Abb. 1: (a) Aufbau des Ultraschall-Ermüdungssystems für die zyklische 3PB/4PB Biegebelastungstest mit (b) schematischer Darstellung des Testprinzips; (c, d) FEM-Simulationen und Probenansicht typischer 4PB bzw. 3PB Proben für großflächige Chiplot bzw. Keramik-Substratlotverbindungen. Die Pfeile zeigen die Positionen der Beanspruchung und der Messpunkte in den 3- und 4-Punkt Biegeversuchen

Abb. 1: (a) Aufbau des Ultraschall-Ermüdungssystems für die zyklische 3PB/4PB Biegebelastungstest mit (b) schematischer Darstellung des Testprinzips; (c, d) FEM-Simulationen und Probenansicht typischer 4PB bzw. 3PB Proben für großflächige Chiplot bzw. Keramik-Substratlotverbindungen. Die Pfeile zeigen die Positionen der Beanspruchung und der Messpunkte in den 3- und 4-Punkt Biegeversuchen

In-situ Delaminationsmessung

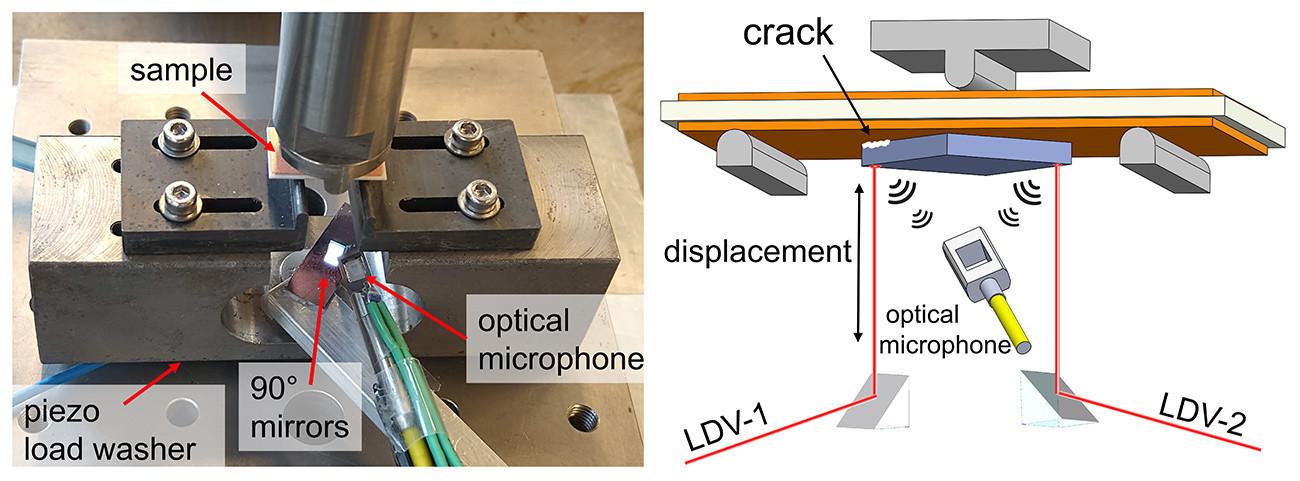

Der Aufbau der zerstörungsfreien in-situ Vibrometer-Messung während der zyklischen Biegeversuche ist in Abbildung 2 dargestellt. Der Aufbau besteht aus einem Laser-Doppler-Vibrometer, um die Auslenkungsamplitude der Probe, die in einem transversalen Resonanzmodus bei 20 kHz schwingt, zu bestimmen. Zwei separate Messpunkte werden durch 90 ° Umlenkspiegel an die Ecken des Chips gerichtet. Sobald nun Risse, aufgrund des Spannungsüberhöhung an den Ecken des Chips, zu wachsen beginnen, erhöht sich die Auslenkungsamplitude des Vibrometer-Signals an der entsprechenden Ecke im Vergleich zur Auslenkung bzw. der Grundschwingung des Substrats. Diese Zunahme erhöht sich bei Rissausbreitung stetig, bis der Test gestoppt wird oder der Chip vollständig delaminiert ist. Die in-situ Delaminationserkennung wurde auf eine Auswahl der oben beschriebenen Probensysteme angewandt, um den Zeitpunkt der Rissentstehung sowie die Delaminationsrate zu bestimmen. Die Ermüdungstests können unter isothermen Bedingungen bis zu etwa 200 °C durchgeführt werden um die Schädigungen der Lotverbindungen unter hohen Belastungen, denen Leistungsmodule im Betrieb ausgesetzt sein können, nachzustellen. Zur Erwärmung der Proben während der Prüfung wird dabei ein Heißluftgebläse eingesetzt. Die Proben können entweder bis ‚End-of-Life‘, das heißt bis zur vollständigen Delamination oder mit der in-situ Methode bis zu einem bestimmten Schädigungsgrad geprüft werden.

Abb. 2: (a) Setup und (b) schematisches Prinzip der zerstörungsfreien in-situ Delaminationsmessung mittels Laser-Doppler-Vibrometrie und akustischer Emissionsmessung während der zyklischen Ultraschall-Biegebelastungstests

Abb. 2: (a) Setup und (b) schematisches Prinzip der zerstörungsfreien in-situ Delaminationsmessung mittels Laser-Doppler-Vibrometrie und akustischer Emissionsmessung während der zyklischen Ultraschall-Biegebelastungstests

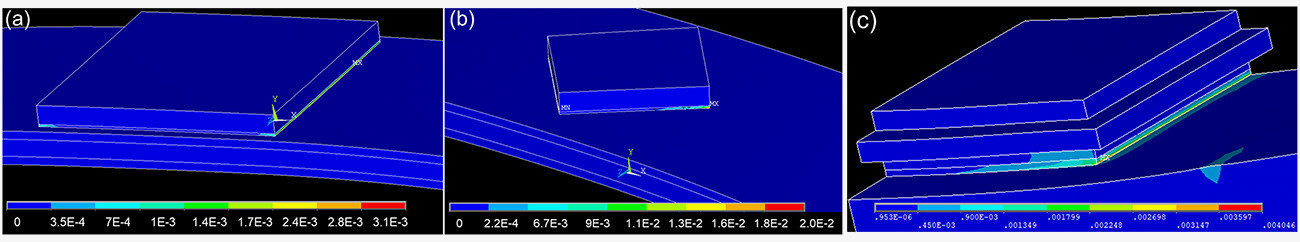

Abb. 3: Diagramm der akkumulierten plastischen Dehnung in den Lotschichten der verschiedene Probenkonfigurationen. Die kritischen Stellen der maximalen plastischen Dehnung, an der erste Risse zu erwarten sind, sind an den Probenrändern lokalisiert

Abb. 3: Diagramm der akkumulierten plastischen Dehnung in den Lotschichten der verschiedene Probenkonfigurationen. Die kritischen Stellen der maximalen plastischen Dehnung, an der erste Risse zu erwarten sind, sind an den Probenrändern lokalisiert

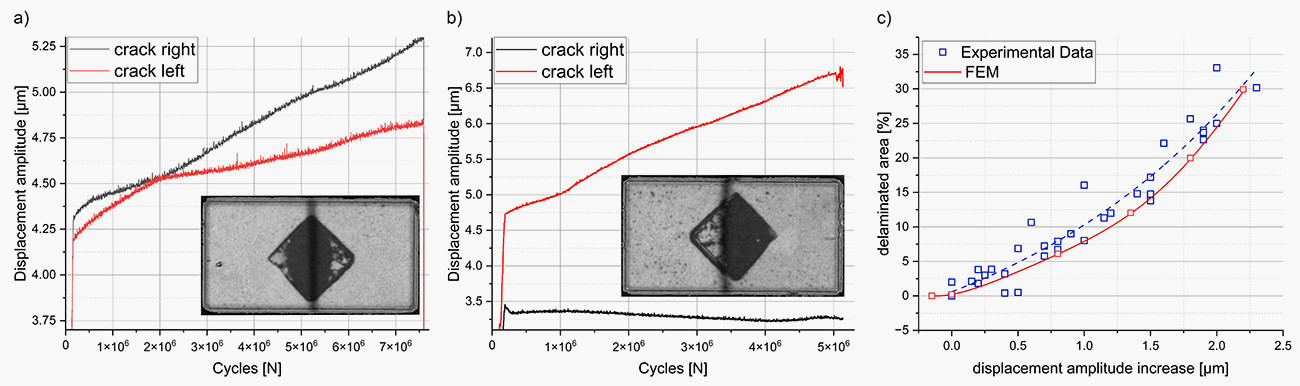

Im folgenden sind Ergebnisse der in-situ Delaminationsmessungen für eine Serie von Chip/Lot/DCB (Direct Copper Bonded) Proben in 3PB Anordnung an 45 ° gedrehter Chipgeometrie, die einer zusätzlichen Erhöhung der Spanungskonzentration dienen, erläutert. In Abbildung 4 a, b sind zwei exemplarische Kurven der Auslenkungsamplitude gegen die Zyklenzahl den SAM (Scanning Acoustic Microscopy) Bildern der delaminierten Flächen gegenübergestellt. Im ersten Fall geht die Erhöhung der Auslenkungsamplitude auf beiden Seiten mit symmetrischem Risswachstum an beiden Ecken des Si-Chips einher. Das zweite Beispiel zeigt eine einseitige Delamination im SAM-Bild mit einer starken Erhöhung der Auslenkungsamplitude der entsprechenden Vibrometer-Messungen, während die Amplitude am anderen Eck währen der Versuchsdauer konstant bleibt. Asymmetrisches Delaminationsverhalten kann auf prozessbedingte Qualitätsunterschiede der Lotverbindungen (Poren, Dicke etc.) bzw. kleine Abweichungen von der zentralen Positionierung des Si-Chips zurückgeführt werden.

Abbildung 4 c zeigt die experimentell bestimmte Abhängigkeit der delaminierten Lotfläche von der gemessenen Änderung der Auslenkungsamplitude des Chips für eine definierte Modellstruktur. Eine Fläche von 50 % entspricht dabei vollständiger Delamination der jeweiligen Chiphälfte. Die Korrelation zwischen dem Vibrometer-Signal und der delaminierten Fläche kann dabei klar identifiziert werden. Die damit bestimmte Kalibrationskurve wurde durch Messung zahlreicher Proben verschiedener Lote unabhängig der Belastungszyklen bestätigt. Die alternativ aus dem Schwingungsverhalten der Probengeometrie bei unterschiedlichem Delaminationsgrad mittels FEM berechnete Kurve stimmt dabei gut mit den experimentellen Daten überein. Diese Kurven können als Grundlage zur in-situ Bestimmung von Rissinitiierung und der Delaminationsrate für die jeweilige Teststruktur dienen.

Abb. 4: Beispiele für (a) beidseitiges und (b) einseitiges Risswachstum, SAM-Bilder (helle Bereiche zeigen Delamination) und die entsprechenden Diagramme; (c) Beziehung zwischen der delaminierten Fläche und der relativen Auslenkungszunahme, Kalibrationskurven aus experimentell bestimmten Daten (blau) bzw. aus der FEM Simulation (rot)

Abb. 4: Beispiele für (a) beidseitiges und (b) einseitiges Risswachstum, SAM-Bilder (helle Bereiche zeigen Delamination) und die entsprechenden Diagramme; (c) Beziehung zwischen der delaminierten Fläche und der relativen Auslenkungszunahme, Kalibrationskurven aus experimentell bestimmten Daten (blau) bzw. aus der FEM Simulation (rot)

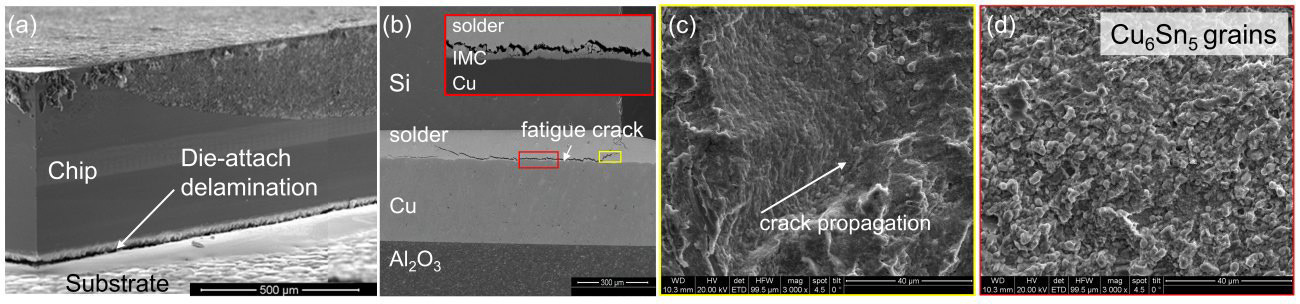

Um das Delaminationsverhalten zu bewerten, werden metallographische Untersuchungen der ermüdeten Proben und Bruchflächenanalyse mittels REM eingesetzt. Die sichtbare Risslänge entlang der Kante des Si-Chips, beginnend an der Ecke ist in REM-Aufnahmen ersichtlich (Abb. 5 a, b). Die Bestimmung der Delaminationslänge entlang der Chip-Seitenkante kann ebenfalls mit guter Übereinstimmung zur Abschätzung der delaminierten Fläche herangezogen werden.

Unsere Ergebnisse, zeigen einen typischen Rissverlauf, der in der Nähe der Ecke der Chip/Lötverbindungs-Grenzfläche entsteht und sich in Richtung des DBC-Substrats ausbreitet (Abb. 5 a). Der Riss folgt dann hauptsächlich der Grenzfläche zwischen Lotverbindung und der Cu6Sn5 intermetallischen Phase (IMC) (Abb. 5 b).

Der Vergleich der delaminierten Fläche zwischen den SAM-Messungen und der Auswertung der alternativ durchgeführten ‚Die-shear‘-Tests lieferte ebenfalls sehr ähnliche Ergebnisse. Beispiele der Ermüdungsbruchflächen der Lötstellen nach den Schertests, die in Abbildung 5 c, d dargestellt sind, zeigen ebenfalls einen Ermüdungsrisspfad der zunächst innerhalb des Lots und anschließend nahe der IMC-Schicht auf der Rückseite des Chips verläuft.

Abb. 5: Typische Ermüdungsrissbildung und Delaminationen in Chiplot (a) Ermüdungsrissbildung im Lot an der Ecke des Chips und entlang der Grenzfläche. (b) Querschnitt des Ermüdungsrisses im Lot und entlang der Grenzfläche zur intermetallischer Phase (IMC) mit beispielhaften Bruchbildern die den Bruchmodus (c) am IMC und (d) im Lot zeigen

Abb. 5: Typische Ermüdungsrissbildung und Delaminationen in Chiplot (a) Ermüdungsrissbildung im Lot an der Ecke des Chips und entlang der Grenzfläche. (b) Querschnitt des Ermüdungsrisses im Lot und entlang der Grenzfläche zur intermetallischer Phase (IMC) mit beispielhaften Bruchbildern die den Bruchmodus (c) am IMC und (d) im Lot zeigen

Anwendungsbeispiele

Zuverlässigkeit von Hochtemperatur-Bleilotlegierungen

Obwohl die derzeitige Ausnahmeregelung die Verwendung von Blei in hochschmelzenden Loten wie etwa bei elektronischen Geräten für militärische und Luft- und Raumfahrtanwendungen erlaubt, rückt die Frist für die Einhaltung der RoHS-Richtlinie schnell näher [5]. Ein aktuelles Anwendungsbeispiel ist der Einsatz von bleireichen Pb-Sn-Ag-Loten für Die-Attach-Anwendungen in Hochleistungs-Halbleiterbauelementen mit hohen Anforderungen an die Zuverlässigkeit [8, 10]. Typische binäre und ternäre Pb-reiche Lote mit Schmelzpunkten im Bereich von 300 °C und darüber, die 5 bis 15 Gew.-% Zinn und bis zu 5 Gew.-% Silber enthalten, weisen ein stabiles Gefüge, ein langsames Wachstum von IMC-Grenzflächenschichten sowie eine hohe thermomechanische Ermüdungsfestigkeit auf und sind zusätzlich relativ kostengünstig. Die Zusammensetzung der Lote sowie die Art der Metallisierung der Chip-Rückseite spielen eine wichtige Rolle, wie aus dem folgenden Beispiel hervorgeht.

In den folgenden Studien wurde das hier vorgestellte beschleunigte zyklische Biegeprüfsystem für die Bewertung von Hochtemperatur-PbSnAg-Loten verwendet [13, 14]. Um die dafür typischen Halbleiterstrukturen nachzubilden, wurden kommerzielle IGBT-Chips mit einer Ni-Metallisierung auf die Ni-beschichteten AMB-Substrate gelötet. Als Die-Attach wurden zwei verschiedene Pb-Lote mit niedrigerem Sn-Gehalt (PbSnAg-L) und höherem Sn-Gehalt (PbSnAg-H) verwendet. Die Geometrien der erhaltenen Halbleiter-Modellstrukturen entsprechen den für das zyklische Biegesystem erforderlichen Resonanzbedingungen.

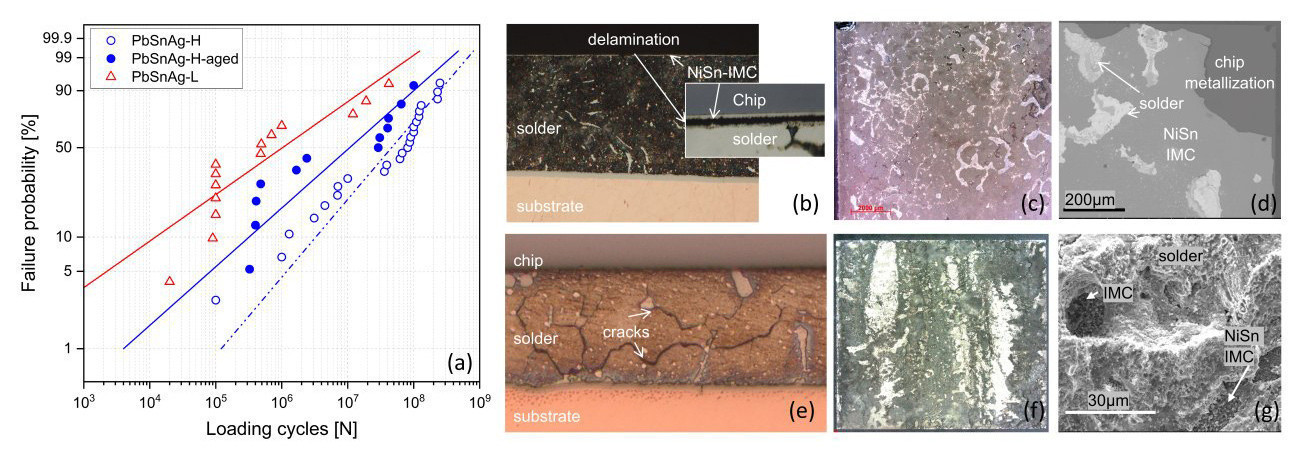

Die Bruchwahrscheinlichkeitskurven, ermittelt bei einer konstanten Biegebelastungsamplitude von ca. 5µm und 80 °C, sind in Abbildung 6 a dargestellt. Die Ergebnisse der beschleunigten Tests zeigen, dass PbSnAg-L- im Vergleich zu den PbSnAg-H-Lötverbindungen eine geringere Zuverlässigkeit aufweisen. Einer Alterung der Proben mit höherem Sn-Gehalt (PbSnAg-HA) bei 250 °C für 250 Stunden führt zur Verminderung der Lebensdauer. Die Fehleranalyse der Proben ergab, dass der dominante Versagensmodus der Lötverbindungen mit dem geringeren Sn die vollständige oder Teil-Delamination des Chips vom Substrat hauptsächlich an der Grenzfläche zwischen dem Ni3Sn2 IMC und der Ni-Metallisierung (Abb. 6 b, c und d) war. Dieser Versagensmodus ähnelt dem Versagen durch ‚Abplatzen/Spalling‘, wie es in der Flip-Chip-Technologie bei PbSn und bleifreien Loten häufig beobachtet wurde. Das Spalling der intermetallischen Verbindungen aus den UBM (under bump metallization)-Schichten wurde durch schnelle Reaktionen zwischen den geschmolzenen Loten und dünnen UBM-Schichten und den Abbau der benetzbaren Schicht erklärt [18]. Es wird angenommen, dass massive Abplatzungen in Lötstellen auftreten, in denen das Reaktionsprodukt empfindlich auf die Zusammensetzung des Lots reagiert und die Konzentration der reaktiven Komponente im Lot begrenzt ist. In diesem Fall, führt die Verringerung der Sn-Konzentration an der Ni/Lot-Grenzfläche und das kontinuierliche Eindringen von Pb in die Ni-Metallisierung zu einer Schwächung der Verbindung an der Grenzfläche zwischen der IMC und der Metallisierungsschicht und zu einem frühzeitigen Versagen. Ein höherer Sn-Gehalt in der Legierung trägt zur Zuverlässigkeit der Lötstellen bei, indem er selbst nach langfristiger thermischer Belastung starke Delaminationen und Grenzflächenversagen verhindert. Der metallographische Querschnitt in Abbildung 6 e belegt die Bildung von Ermüdungsrissen innerhalb des Lots einer PbSnAg-H-Durchläufer-Probe. Die Bruchflächen der ausgefallenen Proben zeigen einen durch Ermüdung des Lots bedingten Fehlermodus (Abb. 6 b, c, d mit 6 e, f, g).

Abb. 6: a) Bruchwahrscheinlichkeitskurven der PbSnAg-Die-Attach-Lötstellen nach hochfrequenter zyklischer Biegebeanspruchung für PbSnAg-Lote mit niedrigem und hohem Sn-Gehalt; Querschnitte der Verbindungsstellen (b, e) und c, d und f, g) Bruchflächen der Chiprückseite nach Ermüdungsbeanspruchung (obere Reihe für PbSnAg-L und untere Reihe für PbSnAg-H)

Abb. 6: a) Bruchwahrscheinlichkeitskurven der PbSnAg-Die-Attach-Lötstellen nach hochfrequenter zyklischer Biegebeanspruchung für PbSnAg-Lote mit niedrigem und hohem Sn-Gehalt; Querschnitte der Verbindungsstellen (b, e) und c, d und f, g) Bruchflächen der Chiprückseite nach Ermüdungsbeanspruchung (obere Reihe für PbSnAg-L und untere Reihe für PbSnAg-H)

Vergleich von bleifreien und bleihaltigen Loten

Generell ist eine hohe Wärmebeständigkeit gegenüber statischen und zyklischen Belastungen eine essentielle Voraussetzung für Die-Attach Materialien. Antimonhaltige Lote gelten derzeit als potenzieller Ersatz für Blei-Lote für Anwendungen im Hochtemperaturbereich. Sn-5Sb (Sn-5wt%Sb) mit einer Liquidus-Temperatur von 245 °C, weist beispielsweise nur ein begrenztes IMC-Wachstum auf, was zu attraktiven Kriech- und mechanischen Eigenschaften wie ausgezeichneten thermischen Ermüdungsverhalten und relativ hoher Bruchfestigkeit führt. Eine weitere Verbesserung der mechanischen Eigenschaften von SnSb-Legierungen kann durch Beifügung zusätzlicher Elemente wie Ag, Au, Ni erreicht werden. Untersuchungen zufolge führt die Zugabe von Ag aufgrund der Bildung von Ag3Sn und der Verfeinerung der β-Sn-Körner zu einer weiteren Erhöhung der Zugfestigkeit des SnSb-Lots.

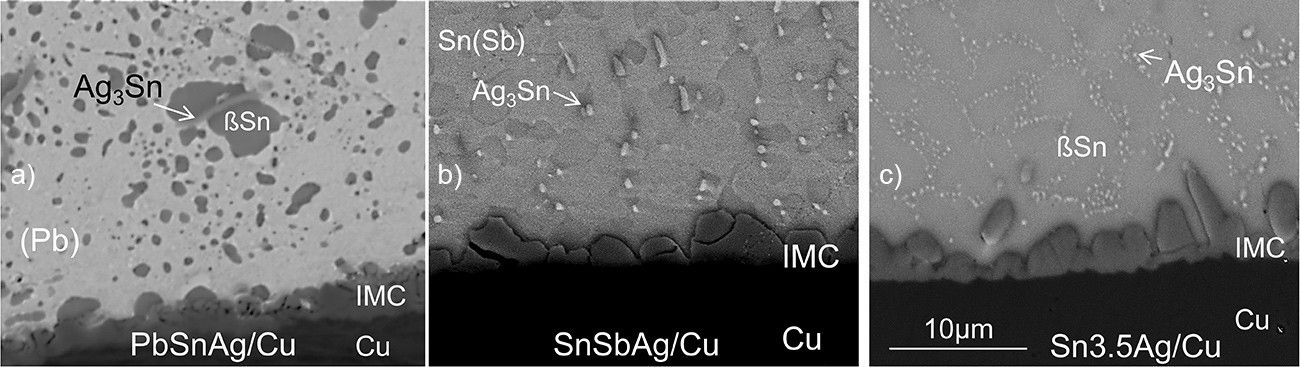

In der folgenden Studie werden die mechanischen Ermüdungseigenschaften von SnSbAg Lotverbindungen, mit denen der häufig verwendeten PbSnAg- und Ag3.5Sn-Lote bei Temperaturen bis zu 175 °C verglichen. Die Modellteststrukturen aus Chip/Lot/DCB und DCB/Lot/Cu wurden in Drei- und Vier-Punkt-Biegekonfigurationen hergestellt (Abb. 1 c, d). Repräsentative Mikrostrukturen der Lötstellen sind in Abbildung 7 dargestellt.

Abb. 7: Typische Gefüge der (a) hochbleihaltigen PbSnAg sowie der (b) bleifreien SnSbAg- und (c) Sn3.5Ag-Cu Lötstellen

Abb. 7: Typische Gefüge der (a) hochbleihaltigen PbSnAg sowie der (b) bleifreien SnSbAg- und (c) Sn3.5Ag-Cu Lötstellen

Abbildung 8 a zeigt einen Vergleich zwischen dem Ermüdungsverhalten der Pb-reichen Lötstellen und dem der SnSbAg-Lotstellen bei 80 °C in Form von Belastungszyklen bis zum Versagen als Funktion der Auslenkungsamplituden im zyklischen Biegeversuch. Um einen Vergleich zwischen den Lebensdauerkurven des Pb-reichen und des SnSbAg-Lots in Bezug auf die Dehnungs- und Spannungswerte zu ermöglichen, wurden die experimentellen Lebensdauerkurven in Abbildung 8 a als Funktion der Gesamtdehnung (8 b) und der durchschnittlichen v. Mises-Spannung (8 c) dargestellt [15]. Dafür wurden transiente FEM-Simulationen der zyklischen Biegeversuche mit elasto-plastischen Materialmodellen für die Lote unter Berücksichtigung der Dehnraten- und Temperaturabhängigkeit der Fließspannung durchgeführt. Es ist zu beachten, dass in diesem Fall die angegebenen Spannungs- und Dehnungswerte für die Initiierung der Risse berechnet wurden und mit zunehmender Risslänge variieren. Die Diagramme zeigen eine bemerkenswert höhere Ermüdungsfestigkeit für das SnSbAg-Lotmaterial bei hohen Zyklen, was auf die hohe Steifigkeit und Kriechfestigkeit der Sb-haltigen Lotlegierung zurückzuführen ist [4, 15, 19].

![Abb. 8: Ermüdungskurven von PbSnAg- und SnSbAg-Lötstellen bei 80 °C, dargestellt als Gesamtlebensdauer in Abhängigkeit von der Auslenkungsamplitude (a) und der gesamten mechanischen Dehnung (b) und der volumengemittelten Spannung (c), die zur Rissentstehung (N0) führt [15]. Abb. 8: Ermüdungskurven von PbSnAg- und SnSbAg-Lötstellen bei 80 °C, dargestellt als Gesamtlebensdauer in Abhängigkeit von der Auslenkungsamplitude (a) und der gesamten mechanischen Dehnung (b) und der volumengemittelten Spannung (c), die zur Rissentstehung (N0) führt [15].](/images/stories/Abo-2023-09/plus-2023-09-099.jpg) Abb. 8: Ermüdungskurven von PbSnAg- und SnSbAg-Lötstellen bei 80 °C, dargestellt als Gesamtlebensdauer in Abhängigkeit von der Auslenkungsamplitude (a) und der gesamten mechanischen Dehnung (b) und der volumengemittelten Spannung (c), die zur Rissentstehung (N0) führt [15].

Abb. 8: Ermüdungskurven von PbSnAg- und SnSbAg-Lötstellen bei 80 °C, dargestellt als Gesamtlebensdauer in Abhängigkeit von der Auslenkungsamplitude (a) und der gesamten mechanischen Dehnung (b) und der volumengemittelten Spannung (c), die zur Rissentstehung (N0) führt [15].

Ein Vergleich der Zuverlässigkeitskurven der drei unter identischen Bedingungen getesteten Lotlegierungen ist in den Abbildungen 9 a und 9 b zu sehen. Es ist dabei ersichtlich, dass die bleifreien Lotverbindungen eine höhere Lebensdauer aufweisen. Die Versuche im Dreipunktbiegemodus wurden bei Temperaturen von 25 °C, 80 °C und 125 °C durchgeführt, während die Vierpunktbiegung bei 175 °C angewendet wurde. Die Trends stimmen dabei sehr gut mit den Ergebnissen der PC- und TC-Tests überein.

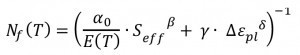

Es ist bekannt, dass die Lebensdauer von Loten unter thermomechanischen oder isothermen mechanischen Belastungsbedingungen auf ein komplexes Materialverhalten zurückzuführen ist, das von der akkumulierten plastischen Dehnung, der Wechselspannung und der mittleren Spannung an den kritischen Stellen der Bauteile abhängt. Daher wird mit dem hier vorgeschlagenen Lebensdauermodell die Zeit bis zur Rissentstehung in der Lötstelle durch die Kombination des Coffin-Manson-Basquin-Modells mit einer multiaxialen Behandlung der Goodman-Relation abgeschätzt, die auch die Auswirkungen der Mittelspannung beschreibt.

Das Lebensdauermodell mit den temperaturabhängigen Materialparametern α0, β, γ und δ ist nachstehend dargestellt, wobei Seƒƒ die effektive Vergleichsspannung und Nf die Anzahl der Zyklen bis zum Ausfall ist.

Dabei werden die aus den verschiedenen Versagensmechanismen resultierenden Anteile an der Lebensdauer nach der Miner-Regel der linearen Schadensakkumulation addiert. Darüber hinaus wurde die Dehnraten- und Temperaturabhängigkeit der inelastischen Verformung durch das viskoplastische Anand-Modell beschrieben. Die exemplarische Kurve in Abbildung 9 c zeigt, dass die experimentellen Lebensdauern der PbSnAg-Lötstellen gut mit dem Schadensakkumulationsmodell beschrieben werden, anhand dessen die optimierten Werte für die Lebensdauerparameter ermittelt wurden. Einzelheiten zu den Simulationen sind in [16] zu finden.

Dabei werden die aus den verschiedenen Versagensmechanismen resultierenden Anteile an der Lebensdauer nach der Miner-Regel der linearen Schadensakkumulation addiert. Darüber hinaus wurde die Dehnraten- und Temperaturabhängigkeit der inelastischen Verformung durch das viskoplastische Anand-Modell beschrieben. Die exemplarische Kurve in Abbildung 9 c zeigt, dass die experimentellen Lebensdauern der PbSnAg-Lötstellen gut mit dem Schadensakkumulationsmodell beschrieben werden, anhand dessen die optimierten Werte für die Lebensdauerparameter ermittelt wurden. Einzelheiten zu den Simulationen sind in [16] zu finden.

![Abb. 9: Weibull-Diagramm der PbSnAg, Sn3.5Ag und SnSbAg Chip/Lot/DCB Verbindungen bis zum Ausfall bei einer Auslenkungsamplitude von 5,2 µm (a) 3PB-Versuch bei 125 °C (b), 4PB-Versuch bei 175 °C, (c) die durch das Modell bestimmten Lebensdauern im Vergleich zu den gemittelten experimentellen Lebensdauern für PbSnAg, dargestellt in einer doppelt logarithmischen Skala [16] Abb. 9: Weibull-Diagramm der PbSnAg, Sn3.5Ag und SnSbAg Chip/Lot/DCB Verbindungen bis zum Ausfall bei einer Auslenkungsamplitude von 5,2 µm (a) 3PB-Versuch bei 125 °C (b), 4PB-Versuch bei 175 °C, (c) die durch das Modell bestimmten Lebensdauern im Vergleich zu den gemittelten experimentellen Lebensdauern für PbSnAg, dargestellt in einer doppelt logarithmischen Skala [16]](/images/stories/Abo-2023-09/plus-2023-09-071.jpg) Abb. 9: Weibull-Diagramm der PbSnAg, Sn3.5Ag und SnSbAg Chip/Lot/DCB Verbindungen bis zum Ausfall bei einer Auslenkungsamplitude von 5,2 µm (a) 3PB-Versuch bei 125 °C (b), 4PB-Versuch bei 175 °C, (c) die durch das Modell bestimmten Lebensdauern im Vergleich zu den gemittelten experimentellen Lebensdauern für PbSnAg, dargestellt in einer doppelt logarithmischen Skala [16]

Abb. 9: Weibull-Diagramm der PbSnAg, Sn3.5Ag und SnSbAg Chip/Lot/DCB Verbindungen bis zum Ausfall bei einer Auslenkungsamplitude von 5,2 µm (a) 3PB-Versuch bei 125 °C (b), 4PB-Versuch bei 175 °C, (c) die durch das Modell bestimmten Lebensdauern im Vergleich zu den gemittelten experimentellen Lebensdauern für PbSnAg, dargestellt in einer doppelt logarithmischen Skala [16]

Bewertung von TLP (Transient Liquid Phase)- und Ag-Sinter-Verbindungen

Beim Transient Liquid Phase (TLP) Bonding und Sintering handelt es sich um Verbindungsverfahren, bei denen niedrige Schmelztemperaturen verwendet werden, um Verbindungen mit hoher Schmelztemperatur herzustellen. TLP-Verbindungen werden durch Fest-Flüssig-Interdiffusion eines niedrigschmelzenden Metalls oder einer Legierung (z. B. Sn, Sn, In) mit einem hochschmelzenden Metall (z. B. Cu, Ag, Au, Ni) als Substrat erreicht. Die vollständige Umwandlung des gesamten niedrigschmelzenden Metalls ergibt eine Verbindung, die nur aus hochschmelzenden intermetallischen Verbindungen (IMCs) besteht. Abhängig von der verwendeten Verbindung liegen die Verarbeitungstemperaturen bei etwa max. 350 ° C.

Beim Niedertemperatursintern von Ag oder Cu wird eine Paste aus Metallpartikeln unterschiedlicher Größe (Mikrometer bis Nanometer) in einem zähflüssigen Zustand ähnlich wie Lötpasten gedruckt, getrocknet und dann drucklos oder unter erhöhtem Druck bei ca. 230 °C gesintert. Der Sinterprozess basiert auf der Festkörperdiffusion, bei der Silber bzw. Cu-Partikel miteinander und mit der Metallisierung von Chip und Substrat verbunden werden. Ein wesentlicher Unterschied zu Lötverfahren besteht darin, dass beim Verbinden von Cu- Substraten mit Silber die Bildung und das Wachstum spröder intermetallischer Grenzflächenphasen im Ag-Cu-System nicht möglich sind. Da insbesondere bei großflächigen Verbindungen, wie z. B. bei der Montage von Leistungshalbleitern, oftmals ein erhöhtes Risiko von Flussmitteleinschlüssen besteht, ist die Anwendung von flussmittelfreien Verfahren wie dem Sintern, von großem Vorteil.

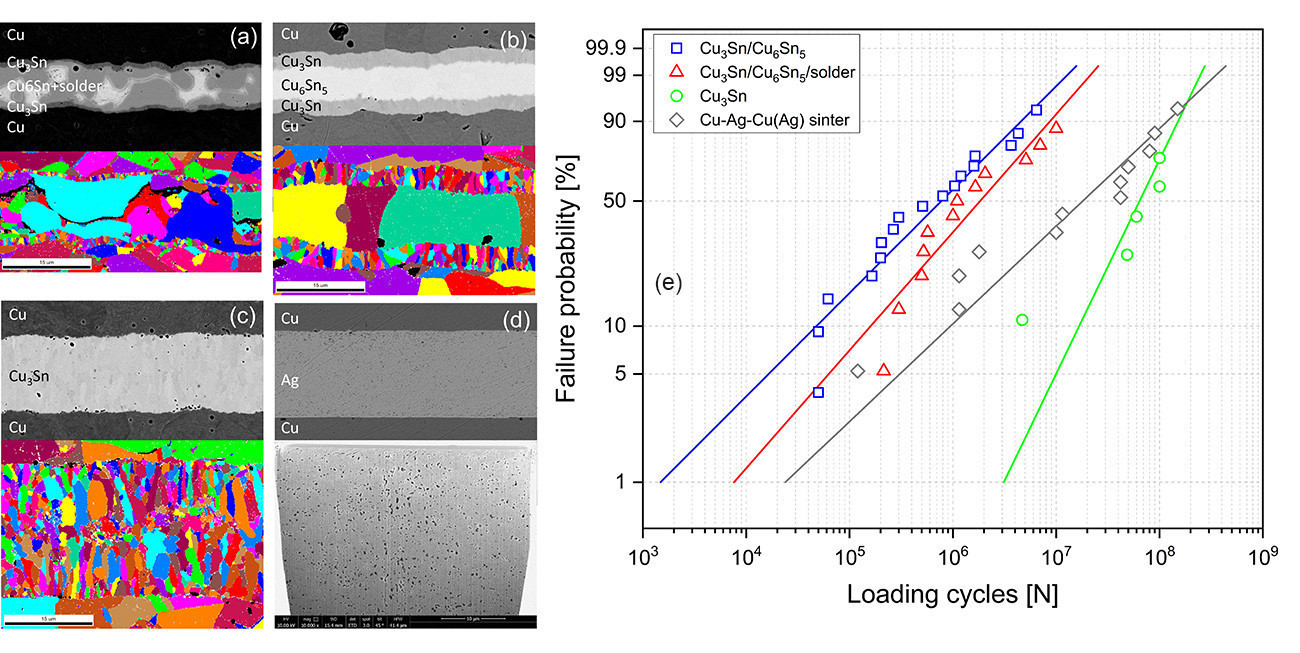

Im folgenden Beispiel wird die Langzeit Zuverlässigkeit von TLP- und Ag- Sinter -Verbindungen untersucht. TLP-Verbindungen wurden mittels Cu-Substraten und einer 97Sn3Cu-Lotlegierung als Zwischenschicht unter verschiedenen Bedingungen (Temperatur, Druck, Zeit) hergestellt. Abhängig von den Prozessparametern wurde das Lot teilweise oder komplett zu Intermetallischen Phasen (IMC) umgewandelt sodass man drei verschiedene Verbindungen bestehend aus i) drei Phasen (Cu3Sn/Cu6Sn5/Lot), ii) zwei Phasen (Cu3Sn/Cu6Sn5) und iii) einer Phase (Cu3Sn) erhält (Abb. 10 a, b, c).

Die in Abbildung 10 e dargestellten Bruchwahrscheinlichkeitsdiagramme von zyklischen 3-PB-Tests bei Raumtemperatur zeigen, dass die höchste Zuverlässigkeit für die einphasigen Cu3Sn-Verbindungen erzielt wurde. Die zweiphasigen Verbindungen (Cu3Sn/Cu6Sn5) wiesen eine etwas geringere Lebensdauer als das dreiphasige System mit IMCs und Rest-Lot auf. Die Fehleranalyse der Proben zeigt, dass im Zweiphasensystem die Cu3Sn/Cu6Sn5-Grenzfläche eine Schwachstelle darstellt, während sich der Riss in der Cu3Sn-Verbindung entweder intergranular oder im Cu-Substrat ausbreitet. Diese Ergebnisse stehen in guter Übereinstimmung mit den höheren Scher- und Biegebruchfestigkeitswerten, die für die Cu3Sn-Phase ermittelt wurden [20].

Um einen Vergleich zwischen der Lebensdauer von TLP-Verbindungen und Ag-Sintern zu ermöglichen, wurde eine Versuchsreihe mit Ag-gesinterten Cu/Cu-Verbindungen durchgeführt (Abb. 10 d) [21]. Die Proben, die eine statische Scherfestigkeit von etwa 30MPa aufwiesen, zeigten niedrigere Werte als Cu3Sn-TLPs, aber immer noch eine verhältnismäßig gute zyklische mechanische Belastbarkeit, wie in Abbildung 10 e gezeigt.

Obwohl TLP und Sintern bereits als Verfahren zur Herstellung hochfester und temperaturbeständiger Verbindungen für Anwendungen in der Leistungselektronik anerkannt sind, wurde die langfristige Zuverlässigkeit und Haltbarkeit dieser Verbindungen noch nicht ausreichend untersucht. Das vorgestellte Verfahren bietet einen effektiven Weg zur Bewertung solcher Hochtemperaturverbindungen, bei denen die temperaturabhängigen Gefüge Veränderungen und Kriecheffekte keine dominierenden Faktoren sind.

Abb. 10: (a) Übersicht und Korngrößenverteilung der drei Typen der TLP Verbindungen bestehend aus Cu3Sn/ Cu6Sn5/97Sn3Cu Lot (b), Cu3Sn/Cu6Sn5 (c), Cu3Sn (d) und Überblick und Detail der porösen, Ag-gesinterten Verbindung (e) Ausfallwahrscheinlichkeit der Cu-Sn TLP Verbindungen (Auslenkungsamplitude 5.3μm) und der Cu/Ag/Cu gesinterten Verbindungen (Auslenkungsamplitude 5 μm) bei 20 kHz / RT

Abb. 10: (a) Übersicht und Korngrößenverteilung der drei Typen der TLP Verbindungen bestehend aus Cu3Sn/ Cu6Sn5/97Sn3Cu Lot (b), Cu3Sn/Cu6Sn5 (c), Cu3Sn (d) und Überblick und Detail der porösen, Ag-gesinterten Verbindung (e) Ausfallwahrscheinlichkeit der Cu-Sn TLP Verbindungen (Auslenkungsamplitude 5.3μm) und der Cu/Ag/Cu gesinterten Verbindungen (Auslenkungsamplitude 5 μm) bei 20 kHz / RT

Zusammenfassung

Im Rahmen des ‚Christian Doppler Labors für Zuverlässigkeit der Grenzflächen in der Elektronik‘ an der TU Wien wurde ein hochfrequenter isothermer zyklischer Biegetest entwickelt, um großflächige Verbindungen in Halbleiter-Teststrukturen zu bewerten, mit weitreichenden Anwendungsmöglichkeiten in Forschung und Entwicklung (F&E). Das System erfüllte erfolgreich die Hauptanforderungen, wie die Testmöglichkeit relevanter Mehrlagenstrukturen (Chip/Lot/Keramiksubstrat oder SMD-Verbindungen), definierte Ausfallkriterien und eine Echtzeit-Methode zur Ausfallbewertung.

Zusätzlich wurde eine zerstörungsfreie In-situ-Methode basierend auf Laser-Doppler-Vibrometrie für beschleunigte mechanische Ermüdungstests eingeführt, um Rissbildung und Risswachstum in Halbleiterstrukturen zu erkennen. Die Ergebnisse zeigten die Anwendbarkeit dieser Technik zur Bewertung von großflächigen Lotverbindungen in mehrschichtigen elektronischen Bauteilen und machen sie zu einer vielversprechenden Alternative für die schnelle Bewertung und das Screening von Lotmaterialien oder anderen elektronischen Verbindungen.

Anhand von Untersuchungen an klassischen, hochbleihaltigen- und bleifreien Loten sowie Sinter- und TLP Verbindungen, die in Hochtemperatur-Halbleiterelementen zur Anwendung kommen wurde die hervorragende Eignung der Methode zur Schadensbewertung und zuverlässigen Erkennung von Rissbildung bestätigt. Einerseits können dadurch in kürzester Zeit Lebensdauerkurven bis zum vollständigen Ausfall (‚End of Life‘) oder einem definierten Ausfallkriterium erstellt werden. Andererseits ermöglicht die Methode in Kombination mit FE-Simulationen eine quantitative Echtzeit-Bestimmung des Delaminationsgrades der jeweiligen Strukturen.

Die beschleunigte mechanische Ermüdungsprüfung hat sich als zuverlässige und präzise Methode zur Bestimmung wesentlicher Materialeigenschaften erwiesen, die für die Entwicklung robuster Modelle zur Lebensdauervorhersage erforderlich sind. Darüber hinaus bietet die Methode durch die Vielseitigkeit in der Anwendung das Potential zur Lebensdauerbewertung für verschiedene elektronische Bauteile (z. B. SMD-Verbindungen).

Diese innovativen Techniken bieten wertvolle Werkzeuge für Forschung und Entwicklung und haben das Potenzial, Entwicklungsprozesse zu beschleunigen und gleichzeitig die Gesamtzuverlässigkeit von elektronischen Geräten und Systemen zu verbessern.

Literatur

[1] 17th annual KPMG Global Semiconductor Industry Outlook, 2022

[2] M. Pecht: Product Reliability, Maintainability, and Supportability, J. of Electr. Pack, 8, (2009), doi:10.1115/1.279215

[3] T. Behrens: Infineon DA5 Consortiumm Customer Consumer Presentation vom 6.4.2023, https://www.infineon.com/dgdl/DA5+Customer+Presentation+06042023.pdf?fileId=5546d4616102d26701610905cfde0005 (Abruf: 14.08.2023)

[4] K. Siow: Die-Attach Materials for High Temperature Applications in Microelectronics Packaging, Springer (2019)

[5] EU RoHS Pack-23 Exemption Recommendations

[6] S. Menon; E. Georg; M. Osterman; M. Pecht: Overview of high lead solder (over 85 %) in the electronics in-dustry, J. Mater. Sci. Mater. Electron., Vol. 26, (2015), 4021–4030

[7] N. Heuck; R. Bayerer; S. Krasel; F. Otto; R. Speckels; K. Guth: Lifetime analysis of power modules with new packaging technologies (2015), 321–324,10.1109/ISPSD.2015.7123454

[8] T. Hunger; R. Bayerer: Reliability of Substrate Solder Joints from Power Cycling Tests PCIM (2009), 713–16

[9] M. Junghaenel; U. Scheuermann: Microelectron Reliab. 76–77, (2017), 480–84

[10] H. Wang; K. Ma; F. Blaabjerg: Design for reliability of power electronic systems, IECON 2012 – 38th Annual Conference on IEEE Industrial Electronics Society, (2012), 33–44

[11] Z. Li; K. Fushinobu; H. Haketa; R. Yasui; T. Shinoda: In-situ diagnosis of solder joint failure by means of thermal resistance measurement, Microelectronics Reliability, Vol. 123, (2021)

[12] D. May; B. Wunderle; R. Schacht; B. Michel: Transient thermal analysis as failure analytical tool in electronic packaging, Proc. 13th Eurosime Conf., (2012)

[13] A. Betzwar Kotas; G. Khatibi: Isothermal bending fatigue response of solder joints in high power semiconductor test structures, Microelectronics Reliability, Vol. 76–77, (2017), 357–361, https://doi.org/10.1016/j.microrel.2017.06.095 (Abruf: 14.08.2023)

[14] G. Khatibi; A. Betzwar Kotas; M. Lederer: Effect of aging on mechanical properties of high temperature Pb-rich solder joints, Microelectron. Reliab., 85 (2018) 1–11

[15] M. Lederer; A. Betzwar Kotas; G. Khatibi: A lifetime assessment and prediction method for large area solder joints, Microelectronics Reliability, Volume 114, (2020), https://doi.org/10.1016/j.microrel.2020.113888 (Abruf: 14.08.2023)

[16] M. Lederer; A. Betzwar Kotas; G. Khatibi: Lifetime modeling of solder joints based on accelerated mechanical test-ing and Finite Element Analysis, Power Electronic Devices and Components,Volume 4, (2023), https://doi.org/10.1016/j.pedc.2023.100034 (Abruf: 14.08.2023)

[17] T. Walter; A. Betzwar Kotas; N. Kretschy; G. Khatibi: In-situ delamination detection in multi-layered semiconductor packages, Microelectronics Reliability (2023) – in press

[18] S.C. Yang; C.E. Ho; C.W. Chang; C.R. Kao: Massive spalling of intermetallic compounds in solder-substrate re-actions due to limited supply of the active element, Journal of Applied Physics, 101 (2007) 8, 084911, https://doi.org/10.1063/1.2717564 (Abruf: 14.08.2023)

[19] A. Morozumi; H. Hokazono; Y. Nishimura; E. Mochizuki: Influence of Antimony on Reliability of Solder Joints Us-ing Sn-Sb Binary Alloy for Power Semiconductor Modules, Transactions of The Japan Institute of Electronics Packaging, 8, 1, 8–17, DOI:10.5104/jiepeng.8.8

[20] A. Betzwar Kotas; G. Khatibi; A. Steiger-Thrisfeld: High cycle fatigue behavior of Cu/Sn intermetallic compounds prepared by transient liquid phase bonding process, Materials Science Forum, 1016, 268–273, DOI: www.scientific.net/MSF.1016.268 (Abruf: 14.08.2023)

[21] Z. Gökdeniz; G. Khatibi; J. Nicolics; C. Gierl-Mayer: Temperature Dependent Mechnical Properties of Sintered Sil-ver-Copper Joints, ISSE 2018 41st Int. Spring Seminar on Electronics Technology, https://doi.org/10.1109/ISSE.2018.8443659 (Abruf: 14.08.2023)