Diese internationale Konferenz bietet Keramiktechnologie sowohl für Mikrosysteme als auch für Verbindungsanwendungen in einem mehrgleisigen technischen Programm.

Der Ceramic Interconnect Track konzentriert sich auf kostengünstige und zuverlässige Hochleistungs-Keramik-Verbindungsprodukte für extreme Umgebungen in der Automobil-, Luft- und Raumfahrt-, Beleuchtungs-, Solar- und Kommunikationsindustrie.

Der Track Ceramic Microsystems konzentriert sich auf neue Anwendungen und neue Produkte, die die Fähigkeit von 3D-Keramikstrukturen nutzen, um das Packaging mit mikrofluidischen, optischen, Mikroreaktor- und Sensorfunktionen zu integrieren.

Bild: WienTourismus/Christian Stemper

Bild: WienTourismus/Christian Stemper

Mehrlagenkeramik-, Dünnschicht-, Tape-Casting-, Dickschicht-Hybrid-, Direct-Write- und Rapid-Prototyping-Technologien sind beiden Tracks gemeinsam, wobei der Schwerpunkt auf Materialien, Prozessen, Prototypenentwicklung, fortschrittlichem Design und Anwendungsmöglichkeiten liegt. Die geplanten Sitzungen und Vortragsthemen umfassen:

1. Functional materials for passive/active devices and their properties

1. Functional materials for passive/active devices and their properties

- Microwave/mm-wave LTCC/ULTCC dielectric materials

- Dielectric/ferroelectric/piezoelectric composites

- Ferroelectric/piezoelectric/pyroelectric/ferrite/ multiferroic materials

- Sensitive ceramics/thermoelectric/ electrocaloric materials

- Pastes/inks/slurries for electronics

2. Material processing and device manufacturing technologies

- LTCC/HTCC and multilayer ceramic and glass processing

- Emerging ultralow temperature, room temperature processing, and cold sintering processing

- Additive manufacturing /3D printing/ direct writing

- Advanced thick film processing

- Fine structuring technologies

- Emerging embedding/integration technologies

3. Design, modeling, simulation, characterization and reliability

3. Design, modeling, simulation, characterization and reliability

- Metamaterials design, realization and characterization

- High frequency devices design/ modeling/simulation

- Materials and devices characterization

- Material and device reliability, lifetime, and failure estimation

- Thermal management/thermal transfer simulation

4. Devices and systems for emerging applications

- Circuits, antennas, and filters for MHz, GHz and THz for communications

- Automotive/aerospace/medical electronics/ optoelectronics

- Flexible/wearable electronics

- Integrated physical/chemical/biological sensors and actuators

- Packaging and integration issues for MEMS and BioMEMS devices

- Batteries/fuel cells/ energy conversion systems

- Micro-reactors/micro-fluidic devices

Begleitende AusstellungDie vollständigen Beiträge sind bis zum 15. Mai 2022 fällig und sollten separat hochgeladen werden, nachdem die Abstracts angenommen wurden. Alle Beiträge werden in englischer Sprache präsentiert und veröffentlicht. Bei Problemen mit dem Online-System wenden Sie sich bitte per E-Mail an das Tagungsbüro Diese E-Mail-Adresse ist vor Spambots geschützt! Zur Anzeige muss JavaScript eingeschaltet sein!.

Begleitende AusstellungDie vollständigen Beiträge sind bis zum 15. Mai 2022 fällig und sollten separat hochgeladen werden, nachdem die Abstracts angenommen wurden. Alle Beiträge werden in englischer Sprache präsentiert und veröffentlicht. Bei Problemen mit dem Online-System wenden Sie sich bitte per E-Mail an das Tagungsbüro Diese E-Mail-Adresse ist vor Spambots geschützt! Zur Anzeige muss JavaScript eingeschaltet sein!.

Die CICMT 2022 wird voraussichtlich als Vor-Ort-Veranstaltung zurückkehren. Als Aussteller haben Sie die einmalige Gelegenheit, Ihre Produkte und Dienstleistungen einem interessierten Publikum aus Anwendern, Entwicklern und einflussreichen Forschern vorzustellen. Die Ausstellungszeiten sind so angeordnet, dass die Aussteller eine maximale Präsenz erhalten. Im Ausstellungsbereich sind Kaffeepausen geplant, um alle Teilnehmer zu ermutigen, sich nach Belieben formell und informell zu treffen. Plätze sind nach dem Prinzip „Wer zuerst kommt, mahlt zuerst“ verfügbar. Wir werden versuchen, alle Ihre speziellen Bedürfnisse und Wünsche zu berücksichtigen.

Details zu Optionen und Gebühren werden in Kürze verfügbar sein.

General Chair:

Ulrich Schmid, TU Wien

Vice General Chair:

Markus Eberstein, TDK Sensors

Technical Organizing Committee:

- Simon Ang, High Density Electronic Center, University of Arkansas

- Heli Jantunen, University of Oulu

- Eung Soo Kim, Kyonggi University

- Soshu Kirihara, Joining and Welding Research Institute Osaka University

- Daniel Krueger, Honeywell

- Zhifu Liu, Shanghai Institute of Ceramics of the Chinese Academy of Sciences

- Jens Müller, Technische Universität Ilmenau

- Uwe Partsch, Fraunhofer IKTS

- Steve Dai, Sandia National Laboratories

- Michael Schneider, TU Wien

Technische Sponsoren:

- IMAPS Deutschland e. V.

- IMAPS International Microelectronics and Packaging Society

- ACerS – American Ceramics Society

Harsh environment interconnection technology for three-dimensional packaging

J. Bickel [1,3], Joachim Scherer [4], M. Schneider Ramelow [2,3], K.-D. Lang [2,3], H.-D. Ngo [1,2]

Die Arbeitsgruppe um Prof. Dr.-Ing. Ha Duong Ngo kann auf einen erfolgreichen Projektabschluss zum Thema „3D – Metallisation mittels Atmosphärendruck-Sputtern für harsh environment Sensorgehäuse (3D Wire)“ zurückblicken.

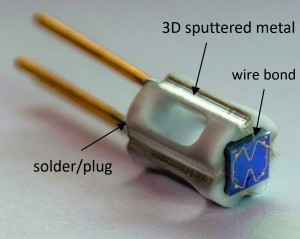

Es wurde eine Technologie entwickelt, welche mittels Atmosphärendruck-Sputtern Dünnschicht-Leiterzüge auf Keramik-Rohlinge für Sensorgehäuse aufbringt, um so die elektrische Verbindung zwischen Sensor und Gehäuse-Außenseite zu bewerkstelligen. Das abgeschiedene Hochtemperaturmetallsystem wurde erfolgreich mittels fotoelektrochemischer Ätztechnik strukturiert. Erste Muster belegen die Flexibilität des Verfahrens, die eine bedarfsgerechte Anpassung der Keramikgeometrie an die Umgebungsbedingungen und an das verwendete System ermöglicht.

1. Motivation

In the field of SiC electronics, more and more improvements have been made in the area of harsh environment in recent years. Especially in terms of high temperature resistance. While initially only simple transistors were used (P. G. Neudeck, 2008), the first more complex circuits in 6H-SiC are now possible (M. Shakir, 2019). Also in the sector of micromechanical sensors, solutions for temperatures of 500 °C have existed for several years (L. Y. Chen, 2013) (A. A. Ned, 1998). However, the limiting factor today is often the circumstance of reliable and inexpensive interconnection technology (ICT) and packaging technology. Due to the high temperatures and the different CTEs of different materials that are used, only a few raw materials can be considered for high temperature ITC. Obvious materials are ceramics and for low cost systems especially Al2O3. Platinum and gold thin wire bonding is suitable for the interconnect level between chip and substrate (L. Coppola, 2007).

2. State of the Art

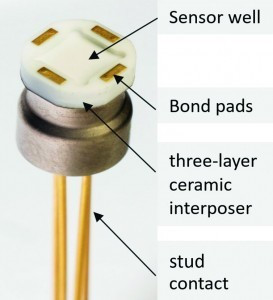

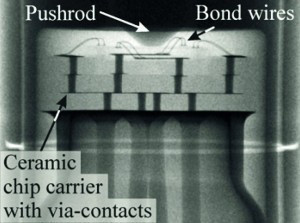

Since Al2O3, like other ceramics, is difficult to pattern by micro technological methods, the capabilities for ICT are very limited. Thick film pastes of gold and platinum are generally used on planar substrates (R. Zeiser, 2015). The disadvantages are the increased consumption of resources due to the technological and not the physical limits as well as the fact that no through-hole vias or 3D structures can be realized. Today, a punching through hole stud bonding process is often used to establish electrical connections in three dimensions from the chip level to the environment. With such a system, a very large number of steps are required to place the solid metal stud through the hole in the ceramic. Then, layer by layer, the materials have to be stacked on top of each other. Such a stacked system is shown in Figures 1 and 2 and has been used since several years for the application in pressure sensor measuring systems (H. D. Ngo, 2012).

3. Technical Approach

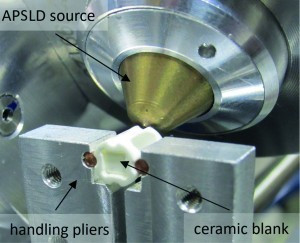

To overcome the drawbacks of existing technologies, we have developed a solution that uses the atmospheric pressure sputtering layer deposition technology (APSLD) (J. Bickel, 2019) to enable signal routing on special 3D printed ceramic substrates using platinum and gold metallization. The APSLD technology is used to additively deposit the metal directly and in a structured process in notches that are located along the side of a cylinder. The metal covers only the surface in the notch, as can be seen in Figures 3 and 4. In addition, the metallization coating is applied over the end faces of the cylinder. This allows the ceramic to be subsequently framed and welded as required, including by conductive materials such as Invar or Kovar, and to be contacted from the top and bottom surfaces. Thin-wire wire bonding is very well suited as a contacting solution to the chip level. In this system, SMD solder contacts can be used on the underside, or an FR4 interposer can be attached, as the thermal stress on the underside is no longer in the critical range and since high temperatures no longer exist here.

4. Discussion

Due to the high flexibility of the process, the ceramic geometry can be adapted as required to the environmental conditions and the system used. When applying pure platinum as conductive material, platinum layer thicknesses of 200 to 300 nm can be used for 10 mm long conductors with 10 Ohm resistance and thus technology consumption costs and material costs for the metallisation of only a few cents per conductor can be realized. These are significant cost reductions compared to the solid metal connections in today’s standard systems. The conductor can be applied fully automatically to any solid material, eliminating the need for further assembly and handling steps for the manufacture of the package itself.

Firmen:

[1] University of Applied Sciences, Berlin, Germany

[2] Fraunhofer IZM, Berlin, Germany

[3] Technische Universität Berlin, Berlin, Germany

[4] Aurion Anlagentechnik GmbH, Seligenstadt, Germany

Referenzen:

A. A. Ned, R. S. (1998), 6H-SiC pressure sensor operation at 600 °C, Fourth International High Temperature Electronics Conference. HITEC

H.D. Ngo, (2012), Liquid-free SOI-based piezoresistive pressure sensor for measurement up to 400 °C, IEEE Sensors, S. 100–114, Taiwan

J. Bickel, H.-D. N.-D, (2019), Increasing the productivity of the novel atmospheric pressure sputtering technology for 3D chip interconnection, Pisa: IEEE

L. Coppola, D.H. (2007), Survey on High-Temperature Packaging Materials for SiC-Based Power Electronics Modules, IEEE Power Electronics Specialists Conference

L.Y. Chen, G.W. (2013), Packaging technologies for high temperature electronics and sensors, Joint Conference on 67th Machinery Failure Prevention Technology

M. Shakir, S.H. (2019), Shakir, Muhammad et al., 555-Timer and Comparators Operational at 500 ° C, IEEE Transactions on Electron Devices

P. G. Neudeck, e. a. (2008), 6H-SiC Transistor Integrated Circuits Demonstrating Prolonged Operation at 500 °C, IMAPS HiTEC

R. Zeiser, P. W. (2015), Flip-chip package for pressure sensors with operationtemperatures up to 500 °C, AMA Conferences

Im Oktober vergangenen Jahres fand die IMAPS-Herbstkonferenz wieder in Präsenz in München statt, wir berichteten bereits im Dezemberheft darüber. Es gab auch wieder einen „Best Presentation Award“. Die Entscheidung fiel auf den Vortrag von Kathrin Reinhardt vom Fraunhofer IKTS Dresden. Sie überzeugte im Vortrag und in der anschließenden Diskussion durch fundiertes Wissen und sachliche Formulierungsweise. Der Vortrag war sehr anschaulich und strukturiert vorbereitet. Sie stellte ein bekanntes, aber neu belebtes Thema vor – Fotostrukturierbare Pasten. Damit könnte die Lücke zwischen dem technisch „einfachen“ Siebdruckverfahren und der technologisch aufwendigen Mikrostrukturierung gefüllt werden. Frau Reinhardt hat freundlicherweise einen Abriss des präsentierten Themas für die PLUS aufgearbeitet.

Fotostrukturierbare Pasten – Neueste Innovationen in der Fineline-Dickschichttechnik

Abb. 1: Darstellung der beiden zusätzlichen Prozessschritte: a) Schicht nach Siebdruck, b) Belichtung mittels UV Licht durch eine Negativ-Fotomaske, c) Entwicklung mittels wässriger Lösungen und d) entwickelte Strukturen vor dem SinternEntwicklungen im Bereich mobile Kommunikation (5G, 6G), (autonome) Mobilität sowie Internet of Things (Smart Cities, Wearables, Objekt Tracking, Smart Grids, Video Security) sind in der europäischen Forschungs- und Industrielandschaft hochaktuell. Hierfür werden immer höhere Übertragungsbandbreiten und somit immer höhere Arbeitsfrequenzen > 60 GHz benötigt. Um dieses Potential ausschöpfen zu können, werden neue Technologien zur Erzeugung der Hochfrequenzschaltungen benötigt, mit denen immer feinere Leiterzüge mit immer engeren Abständen im Bereich von jeweils 10–30 µm realisiert werden können. Für diese Zielsetzung wurden am Fraunhofer IKTS Dickschichtpasten entwickelt, welche mittels UV-Licht fotostrukturierbar sind und die angestrebten geometrischen Auflösungen ermöglichen können. Dabei ist ein vergleichbarer Technologieansatz bereits in der Vergangenheit von der Firma DuPont – FODELTM verfolgt worden, allerdings konnte es auf Grund einer eingeschränkten Materialvielfalt (Gold, Silber, Dielektrika) und unzureichenden Geometrieauflösungen (40 µm Linienbreiten; 50 µm -abstände) nie zur industriellen Anwendung gebracht werden. Im Bereich der drahtlosen Kommunikation stellen deshalb die neu entwickelten IKTS fotostrukturierbaren Pasten (Silber, Gold, Platin, Widerstände) einen enormen Mehrwert dar, welche vergleichend zu FODEL zudem robuster (Verarbeitung unter Weißlicht), prozessfreundlicher (sehr kurze Prozesszeiten) und umweltfreundlicher (RoHS/REACH-kompatibel) sind. Zum besseren Verständnis ist in Abbildung 1 der Fotostrukturierungsprozess skizziert. Im Vergleich zur konventionellen Dickschichttechnik sind zur Strukturierung zwei Zusatzschritte (Belichtung und Entwicklung) nach dem Siebdruck notwendig. Die zusätzlichen Prozessschritte benötigen jeweils nur zwischen 5 und 20 s und können problemlos in etablierte Produktionsprozesslinien integriert werden. Die Belichtung kann dabei entweder über Fotomasken oder maskenlose Laser-Direkt-Schreibverfahren (LDI) erreicht werden. Dieses neuartige Merkmal wird durch gezielte Anpassung des fotosensitiven Binders ermöglicht und trägt zur Digitalisierung der Prozesstechnologie und zu einer dadurch nochmaligen Verbesserung der Strukturgenauigkeit bei.

Abb. 1: Darstellung der beiden zusätzlichen Prozessschritte: a) Schicht nach Siebdruck, b) Belichtung mittels UV Licht durch eine Negativ-Fotomaske, c) Entwicklung mittels wässriger Lösungen und d) entwickelte Strukturen vor dem SinternEntwicklungen im Bereich mobile Kommunikation (5G, 6G), (autonome) Mobilität sowie Internet of Things (Smart Cities, Wearables, Objekt Tracking, Smart Grids, Video Security) sind in der europäischen Forschungs- und Industrielandschaft hochaktuell. Hierfür werden immer höhere Übertragungsbandbreiten und somit immer höhere Arbeitsfrequenzen > 60 GHz benötigt. Um dieses Potential ausschöpfen zu können, werden neue Technologien zur Erzeugung der Hochfrequenzschaltungen benötigt, mit denen immer feinere Leiterzüge mit immer engeren Abständen im Bereich von jeweils 10–30 µm realisiert werden können. Für diese Zielsetzung wurden am Fraunhofer IKTS Dickschichtpasten entwickelt, welche mittels UV-Licht fotostrukturierbar sind und die angestrebten geometrischen Auflösungen ermöglichen können. Dabei ist ein vergleichbarer Technologieansatz bereits in der Vergangenheit von der Firma DuPont – FODELTM verfolgt worden, allerdings konnte es auf Grund einer eingeschränkten Materialvielfalt (Gold, Silber, Dielektrika) und unzureichenden Geometrieauflösungen (40 µm Linienbreiten; 50 µm -abstände) nie zur industriellen Anwendung gebracht werden. Im Bereich der drahtlosen Kommunikation stellen deshalb die neu entwickelten IKTS fotostrukturierbaren Pasten (Silber, Gold, Platin, Widerstände) einen enormen Mehrwert dar, welche vergleichend zu FODEL zudem robuster (Verarbeitung unter Weißlicht), prozessfreundlicher (sehr kurze Prozesszeiten) und umweltfreundlicher (RoHS/REACH-kompatibel) sind. Zum besseren Verständnis ist in Abbildung 1 der Fotostrukturierungsprozess skizziert. Im Vergleich zur konventionellen Dickschichttechnik sind zur Strukturierung zwei Zusatzschritte (Belichtung und Entwicklung) nach dem Siebdruck notwendig. Die zusätzlichen Prozessschritte benötigen jeweils nur zwischen 5 und 20 s und können problemlos in etablierte Produktionsprozesslinien integriert werden. Die Belichtung kann dabei entweder über Fotomasken oder maskenlose Laser-Direkt-Schreibverfahren (LDI) erreicht werden. Dieses neuartige Merkmal wird durch gezielte Anpassung des fotosensitiven Binders ermöglicht und trägt zur Digitalisierung der Prozesstechnologie und zu einer dadurch nochmaligen Verbesserung der Strukturgenauigkeit bei.

|

PI-Paste auf Al2O3 |

Flächenwiderstand1 [mOhm/sq] |

Gebrannte Schichtdicke [µm] |

Linienauflösung Linie / Abstand [µm/µm] |

|

Silber2 (PI1101) |

≤ 3,5 |

8–12 |

20/20 |

|

Gold2 (PI2101) |

≤ 6 |

8–15 |

20/20 |

|

Platin3 (PI6101) |

≤ 40 |

6–12 |

20/30 |

|

RuO22 (W20024) |

3500 k |

11–17 |

40/35 |

1 Sheet resistivity, calculated for a fired thickness of 10±1 μm

2 Firing profile: 10 min at 850 °C

3 Firing profile: 10 min at 1200 °C

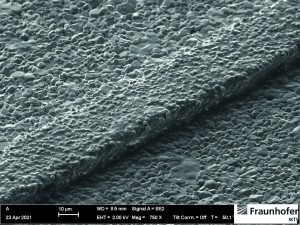

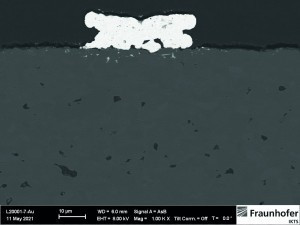

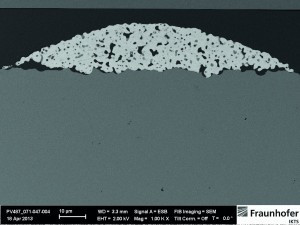

Die realisierten Querschnitte der Leiterzüge weisen im Vergleich zu konventionell gedruckten Leiterzügen eine nahezu rechteckige Form auf, wobei die Schichtdicken im für Hochfrequenzapplikationen relevanten Bereich 8–12 µm gesintert liegen (Abb. 2).

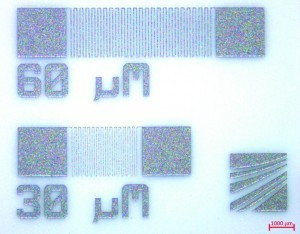

Abb. 2: Mittels fotostrukturierbaren Pasten am IKTS hergestellte Strukturen mit einer Auflösung von 60 bzw. 30 µm Linien mit je 30 µm Abstand (oben links) sowie elektronmikroskopischen Aufnahmen der ungesinterten Leiterzugflanke (20 µm) (oben rechts), einen Querschliff eines gesinterten fotostrukturierten (20 µm) (unten links) sowie konventionell hergestellten Leiterzugs (100 µm) (unten rechts)

Der Fokus der aktuellen Entwicklungen der PI-Pasten am IKTS liegt auf den Metallisierungspasten, wie Silber, Gold, Platin und Kupfer. Aber auch PI-Widerstands- und Dielektrikumspasten werden derzeit entwickelt. Am Beispiel der PI-Silberpasten konnte gezeigt werden, dass diese sowohl für Aluminiumoxidsubstrate als auch für Low Temperature Cofired Ceramics (LTCC) eingesetzt werden können. Die entwickelten Silberpasten ermöglichen somit LTCC-Aufbauten im Post- als auch Cofiringprozess. Hierbei wurden Linienbreiten von 10 µm und Spaltbreiten von 16 µm im co-gesinterten Zustand realisiert. Erste Untersuchungen haben außerdem gezeigt, dass die IKTS-PI-Pasten für das Laserdirektbelichten geeignet sind. Tabelle 1 zeigt zusammenfassend einen Eigenschaftsüberblick der Silber-, Gold-, Platin- und RuO2-PI-Pasten hinsichtlich geometrischer Auflösung und elektrischer Leitfähigkeit auf Al2O3-Substraten.

Die Ergebnisse zu den PI-Pasten des Fraunhofer IKTS zeigen einen vielversprechenden Massen- und Industrieprozess auf, mit geringen Investitionskosten und nur wenig höherer Fertigungszeit, mit dessen Hilfe Bauteile hergestellt werden können, die bei höheren Frequenzen eine wesentlich bessere HF-Performance als bisher möglich machen und eine deutliche Miniaturisierung für die Zukunft erlauben.

IMAPS Deutschland – Ihre Vereinigung für Aufbau- und Verbindungstechnik

IMAPS Deutschland, Teil der ‚International Microelectronics and Packaging Society' (IMAPS), stellt seit 1973 in Deutschland das Forum für alle dar, die sich mit Mikroelektronik und Aufbau- und Verbindungstechnik beschäftigen. Mit fast 300 Mitgliedern verfolgen wir im Wesentlichen drei wichtige Ziele:

- wir verbinden Wissenschaft und Praxis

- wir sorgen für den Informationsaustausch unter unseren Mitgliedern und

- wir vertreten den Standpunkt unserer Mitglieder in internationalen Gremien.

Veranstaltungskalender

|

Ort |

Zeitraum |

Name |

Veranstalter |

|

Fellbach |

2./3. März 2022 |

Elektr. Baugruppen und Leiterplatten EBL 2022 |

DVS / GMM |

|

Fountain Hills, AZ |

7.-10. März 2022 |

Device Packaging Conference |

IMAPS US |

|

Grenoble, FR |

10.-11. März 2022 |

MiNaPad 2022 |

IMAPS France |

|

Landshut |

6. April 2022 |

Symposium Elektronik und Systemintegration |

HS Landshut |

|

Göteborg, S |

12.-14. Juni 2022 |

NordPac 2022 |

IMAPS Nordic |

|

Wien, AT |

13.-15. Juli 2022 |

CICMT 2022 |

IMAPS |

|

Sibiu, RO |

13.-16. September 2022 |

ESTC 2022 |

IEEE-CPMT IMAPS Europe IEEE-CPMT IMAPS Europe |

|

Berlin |

26.-29. Sept. 2022 |

ESREF 2022 |

IZM / TU |

|

Boston, MA |

3.-6. Oktober 2022 |

Internationales Symposium |

IMAPS US |

|

München |

Okt. 2022 |

Herbstkonferenz |

IMAPS D |

|

München |

Nov. 2022 |

SEMICON EUROPA |

SEMI Europa |

Impressum

IMAPS Deutschland e. V.

Kleingrötzing 1

D-84494 Neumarkt-St. Veit

1. Vorsitzender:

Prof. Dr.-Ing. Martin Schneider-Ramelow,

Stellv. Institutsleiter Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration (IZM),

Diese E-Mail-Adresse ist vor Spambots geschützt! Zur Anzeige muss JavaScript eingeschaltet sein!

Schatzmeister

(bei Fragen zu Mitgliedschaft und Beitrag):

Ernst G. M. Eggelaar, Diese E-Mail-Adresse ist vor Spambots geschützt! Zur Anzeige muss JavaScript eingeschaltet sein!

Ausführliche Kontaktinformationen zu den Vorstandsmitgliedern finden Sie unter www.imaps.de

(Vorstand)